# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 6 Issue: II Month of publication: February 2018

DOI: http://doi.org/10.22214/ijraset.2018.2044

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

Volume 6 Issue II, February 2018- Available at www.ijraset.com

### Performance Analysis of Asymmetrical Cascaded Multilevel DC Link Inverter using Unipolar Modulation Techniques

S. Nagaraja Rao<sup>1</sup>, D. V. Ashok Kumar<sup>2</sup>, Ch. Sai Babu<sup>3</sup>

<sup>1</sup> Research Scholar, Department of Electrical & Electronics Engineering, JNTUK, Kakinada, AP, India <sup>3</sup> Professor, Department of Electrical & Electronics Engineering, RGMCET, Nandyal, AP, India <sup>3</sup> Professor, Department of Electrical & Electronics Engineering, JNTUK, Kakinada, AP, India

Abstract: This paper presents single-phase thirteen level asymmetrical cascaded multilevel DC-link (ACMLDCL) inverter using unipolar modulation techniques fed R and RL loads. The proposed ACMLDCL inverter consists of two stages. The first stage of the inverter consists of multiple half-bridge inverter cells with two switches and a single DC source. All half-bridge inverter cells are connected in a cascaded mode. The inverter performance can be enhanced by selecting the proper values of the DC sources. The second stage of the inverter circuit consists of full bridge circuit operating at a fundamental frequency. Compared with conventional cascaded H-bridge multilevel inverter the proposed ACMLDCL topology has the advantages of reduced switch count, size, cost, modularity and flexibility to increase the number of stages without changing structure of the first stage. The proposed topology can have the improved performance by implementing modulation techniques. This paper presents two unipolar modulation techniques, namely, sub-harmonic and modified space vector modulating techniques to validate the proposed ACMLDCL inverter. The validity of the proposed ACMLDCL inverter is verified in terms of total harmonic distortion (THD) and fundamental output phase voltage using Matlab/Simulink.

Keywords: MLI's, ACMLDCL Inverter, USMT, UMSVMT, THD

#### I. INTRODUCTION

The Multilevel inverters (MLI's) are most promising device in ac power drives when higher power ratings are required with limited harmonic content. The MLI's offers several advantages as compared to the conventional inverters, such as, lower dv/dt, low magnetic interference, high efficiency and operates at high voltage etc. There are three types of the traditional MLI's, namely diodeclamped, flying capacitor and cascaded H-bridge MLI's. Among these three types, cascaded H-bridge MLI widely used for many applications such as electrical drives and renewable energy systems etc. due to its modular structure and requires less number of components as compared to other two topologies [1-2]. But the traditional MLI's are required more number of components to increase the number of levels. So, the requirement of heat sinks, protection circuits and driver circuits are increased accordingly, so that it leads to increase in size, cost and complexity [3-4]. In order to overcome these difficulties, a reduced component count topologies are introduced. Generally, design of a new topology follows three categories such as structural modification and the placement of asymmetric DC source instead of symmetric DC source. The terms symmetric and asymmetric are the most well-known words in MLI topology. If the values of all the DC sources of MLI topology have the same magnitude it is called symmetric whereas asymmetric have unequal DC source value. Every topology has its own advantages and disadvantages. In this paper, analysis of the ACMLDCL inverter is addressed [5-6].

This paper presents a single-phase thirteen level ACMLDCL inverter based on an half-bridge and a full bridge inverter circuits. Compared with the traditional MLI's, the proposed ACMLDCL inverter can have the enhanced performance by implementing the modulating techniques [7-8]. This paper presents the unipolar sub harmonic modulating technique (USHMT) and unipolar modified space vector modulating technique (UMSVMT). The proposed ACMLDCL inverter can significantly reduce the switch count as well asthe number of gate drivers as the number of voltage levels increases [9].

#### II. ASYMMETRIC CASCADED MULTILEVEL DC LINK INVERTER TOPOLOGY

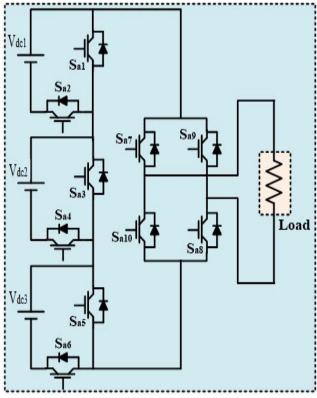

The proposed Thirteen Level ACMLDCL inverter circuit is shown in fig. 1 with an unequal DC voltage source with a ratio of 1:2:3. The corresponding values of dc voltage sources are to be chosen using equation (1).

$$V_{dci} = i*V_{dc}$$

, where  $i = 1,2$  and 3 (1)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue II, February 2018- Available at www.ijraset.com

The maximum value of the output voltage is obtained using equation (2).

$$V_{max} = \sum_{i=1}^{S} V_{dci} \tag{2}$$

The number of output voltage levels can be obtained using the equation (3) and the number of switches for the proposed ACMLDCL inverter can be obtained by using equation (4). Therefore, the proposed thirteen level ACMLDCL inverter consists of three voltage sources, one full bridge inverter and ten switches [10].

$$N_{Levels} = (2^{n+1} - 3)^{F}$$

(3)

$$N_S = 2 (n_1 + n_2 + \dots + n_n) + 4F$$

(4)

Where 'n' is the number of voltage sources and 'F' is the number of full bridge circuits.

Fig.1. Proposed ACMLDCL inverter (13-level)

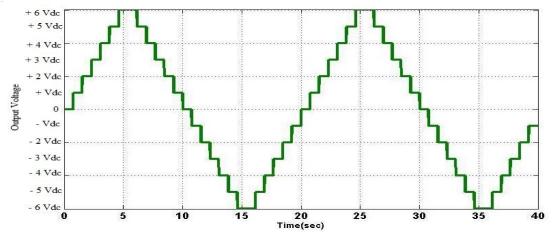

The operation of the proposed thirteen level ACMLDCL inverter explained in different modes of operation as follows and the corresponding output voltage is shown in figure 2.

Mode 1: Conduct the switches S<sub>2</sub>, S<sub>4</sub>, S<sub>6</sub>, S<sub>7</sub> and S<sub>8</sub> to generate + 6 V<sub>dc</sub>

Mode 2: Conduct the switches  $S_1$ ,  $S_4$ ,  $S_6$ ,  $S_7$  and  $S_8$  to generate + 5  $V_{dc}$

Mode 3: Conduct the switches  $S_2$ ,  $S_3$ ,  $S_6$ ,  $S_7$  and  $S_8$  to generate + 4  $V_{dc}$

Mode 4: Conduct the switches  $S_1$ ,  $S_3$ ,  $S_6$ ,  $S_7$  and  $S_8$  to generate  $+\ 3\ V_{dc}$

Mode 5: Conduct the switches S<sub>1</sub>, S<sub>4</sub>, S<sub>5</sub>, S<sub>7</sub> and S<sub>8</sub> to generate + 2 V<sub>dc</sub>

Mode 6: Conduct the switches  $S_2$ ,  $S_3$ ,  $S_5$ ,  $S_7$  and  $S_8$  to generate +  $V_{dc}$

Mode 7: Conduct the switches  $S_2$ ,  $S_3$ ,  $S_5$ ,  $S_9$  and  $S_{10}$  to generate –  $V_{dc}$

Mode 8: Conduct the switches  $S_1,\,S_4,\,S_5,\,S_9$  and  $S_{10}$  to generate – 2  $V_{dc}$

Mode 9: Conduct the switches  $S_1$ ,  $S_3$ ,  $S_6$ ,  $S_9$  and  $S_{10}$  to generate – 3  $V_{dc}$

Mode 10: Conduct the switches  $S_2$ ,  $S_3$ ,  $S_6$ ,  $S_9$  and  $S_{10}$  to generate – 4  $V_{dc}$

Mode 11: Conduct the switches  $S_1$ ,  $S_4$ ,  $S_6$ ,  $S_9$  and  $S_{10}$  to generate – 5  $V_{dc}$

Mode 12: Conduct the switches  $S_2$ ,  $S_4$ ,  $S_6$ ,  $S_9$  and  $S_{10}$  to generate – 6  $V_{dc}$

Volume 6 Issue II, February 2018- Available at www.ijraset.com

Fig.2. Output voltage of the proposed thirteen level ACMLDCL inverter using constant pulses

#### III.MODULATION TECHNIQUES

Modulation techniques are mainly classified into three types, namely fundamental switching frequency, space vector vector and carrier based modulation techniques. Among all the pulse width modulation methods for MLI's, carrier based modulation techniques and space vector control are often used but when the number of output level is more than five, the space vector method will be very complicated with the increase of switching states. So the carrier based modulation techniques are preferred under this condition in MLI's. This paper focuses on unipolar carrier based sub-harmonic and modified space vector modulation techniques which have been extended for use in MLI topologies by using multiple carriers [11].

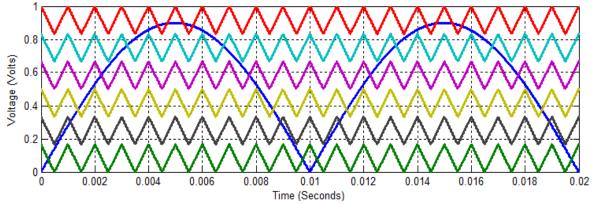

Unipolar carrier type modulation techniques are employed to trigger the switches of first stage of the proposed ACMLDCL inverter and the fundamental switching frequency is used to generate the pulses for the full bridge inverter circuit. For an m-level of ACMLDCL inverter the proposed modulation requires (m-1)/2 carriers with the same amplitude and frequency, therefore for the thirteen level ACMLDCL inverter, six carriers are used to generate the firing pulses and all the carrier signals will have same amplitude and frequency but the carrier signals are shifted in levels. All the carrier signals will be in-phase [12].

#### A. Unipolar Sub-harmonic Modulation Technique (USMT):

The pattern of in-phase triangular carrier based level shifted technique is used to generate firing pulses to power switches of thirteen level ACMLDCL inverter using USMT is shown in Figure 3.

Fig.3. Pulse generation of the proposed ACMDCL inverter using USMT

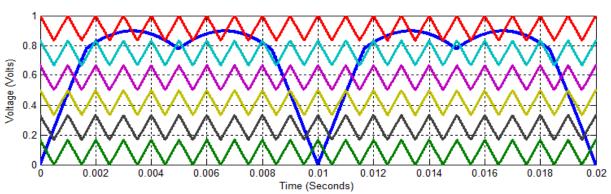

#### B. Unipolar modified space vector modulation technique (umsvmt)

To obtain the maximum possible peak amplitude of the fundamental phase voltage, a offset voltage, Voffset1, is added to the reference phase voltages to generate the USVMT waveform, where the magnitude of Voffset1 is given by equation (5). The pattern of in-phase triangular carrier based level shifted technique is used to generate firing pulses to power switches of thirteen level ACMLDCL inverter using UMSVMT is shown in Figure 4.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue II, February 2018- Available at www.ijraset.com

$$V_{offset1} = \frac{-(V_{\text{max}} + V_{\text{min}})}{2} - (5)$$

Fig.4. Pulse generation of the proposed ACMDCL inverter using UMSVMT

#### IV. SIMULATION RESULTS

The Simulation was conducted to verify the operation of the proposed single phase thirteen level ACMLDCL inverter using USPM and MSVPM Techniques fed R and RL-loads. The parameters used to simulate the proposed models are depicted in table 1.

TABLE I. SYSTEM PARAMETERS

| Parameter                                                                | Value                 |

|--------------------------------------------------------------------------|-----------------------|

| Resistance Load                                                          | 50 Ohms               |

| Inductance Load                                                          | 100 mH                |

| Voltage ratios (V <sub>dc1</sub> , V <sub>dc2</sub> , V <sub>dc3</sub> ) | 50 V, 100 V and 150 V |

| Switching frequency                                                      | 5 kHz                 |

| Modulation index                                                         | 0.866                 |

#### A. Unipolar Sub-harmonic Modulation Technique (USMT):

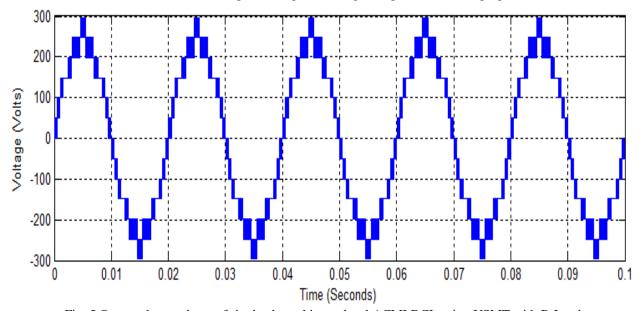

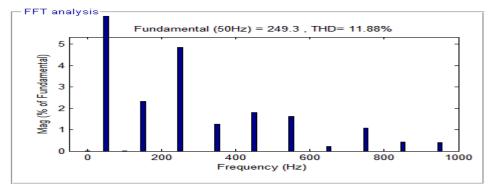

Fig. 5 and 7 shows the single-phase thirteen level output phase voltage and current of proposed ACMLDCL inverter using USMT fed R-load with a modulation index of 0.866 and Fig.6 and 8 shows the corresponding THD analysis, from the Fig's 6 and 8 it is noticed that the harmonic distortion of 11.88 % is present in phase voltage and phase current of proposed ACMLDCL inverter.

Fig. 5 Output phase voltage of single phase thirteen level ACMLDCL using USMT with R-Load

Volume 6 Issue II, February 2018- Available at www.ijraset.com

Fig. 6 Phase voltage THD of single phase thirteen level ACMLDCL using UMSVMT with R-Load

Fig. 7 Output phase current of single phase thirteen level ACMLDCL using USMT with R-Load

Fig. 8 Phase current THD of single phase thirteen level ACMLDCL using USMT with R-Load

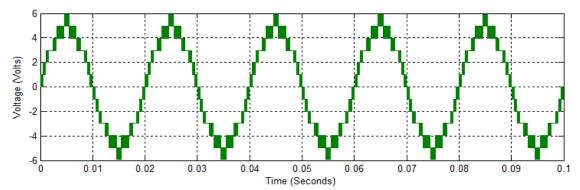

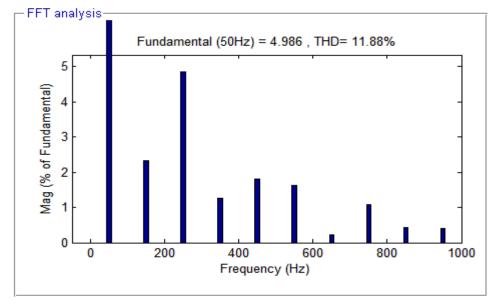

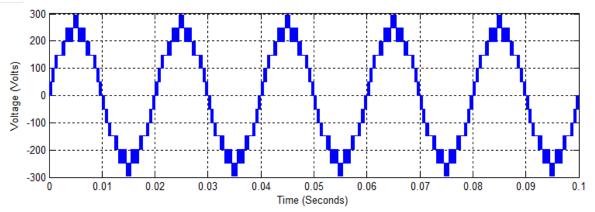

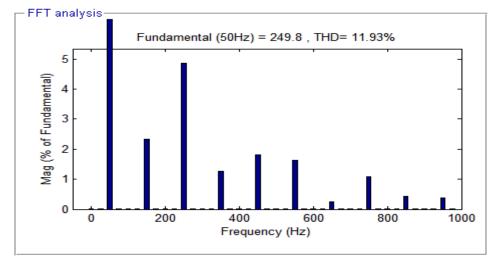

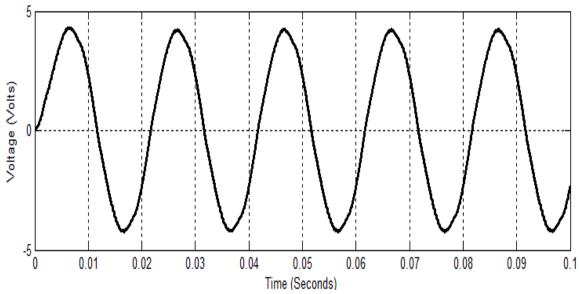

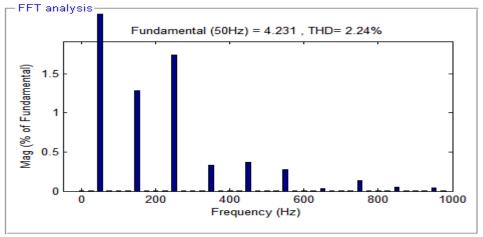

Fig. 9 and 11 shows the single-phase thirteen level output phase voltage and current of proposed ACMLDCL inverter using USMT fed RL-load with a modulation index of 0.866 and Fig.10 and 12 shows the corresponding THD analysis, from the Fig's 10 and 12 it is noticed that the harmonic distortion of 11.93 % is present in phase voltage and 2.24 % in phase current of proposed ACMLDCL inverter.

Volume 6 Issue II, February 2018- Available at www.ijraset.com

Fig. 9 Output phase voltage of single phase thirteen level ACMLDCL using USMT with RL-Load

Fig. 10 Phase voltage THD of single phase thirteen level ACMLDCL using UMSVMT with RL-Load

Fig. 11 Output phase current of single phase thirteen level ACMLDCL using USMT with RL-Load

Volume 6 Issue II, February 2018- Available at www.ijraset.com

Fig. 12 Phase current THD of single phase thirteen level ACMLDCL using USMT with RL-Load

#### B. Unipolar Modified Space Vector Modulation Technique (UMSVMT):

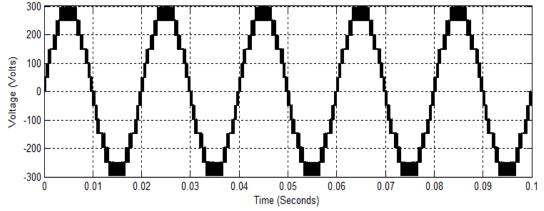

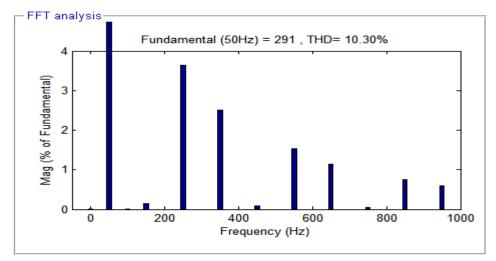

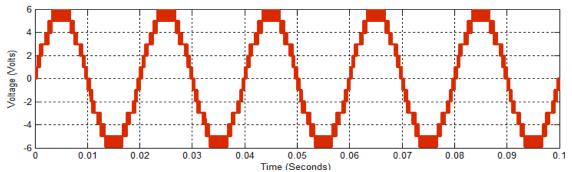

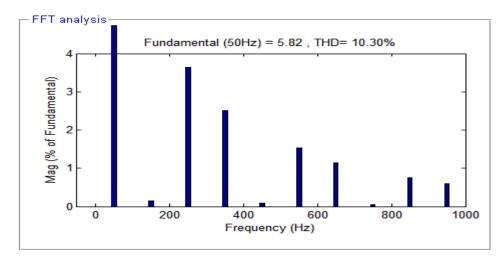

Fig. 13 and 15 shows the single-phase thirteen level output phase voltage and current of proposed ACMLDCL inverter using UMSVMT fed R-load with a modulation index of 0.866 and Fig.14 and 16 shows the corresponding THD analysis, from the Fig's 14 and 16 it is noticed that the harmonic distortion of 10.30 % is present in phase voltage and phase current of proposed ACMLDCL inverter.

Fig. 13 Output phase voltage of single phase thirteen level ACMLDCL using UMSVMT with R-Load

Fig. 14 Phase voltage THD of single phase thirteen level ACMLDCL using UMSVMT with R-Load

Volume 6 Issue II, February 2018- Available at www.ijraset.com

Fig. 15 Output phase current of single phase thirteen level ACMLDCL using UMSVMT with R-Load

Fig. 16 Phase current THD of single phase thirteen level ACMLDCL using UMSVMT with R-Load

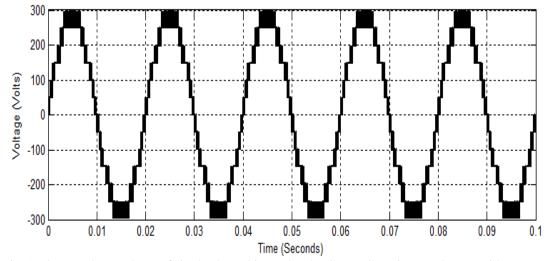

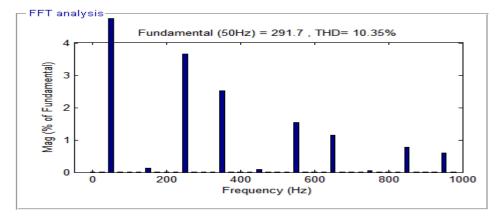

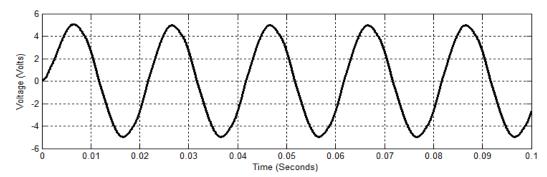

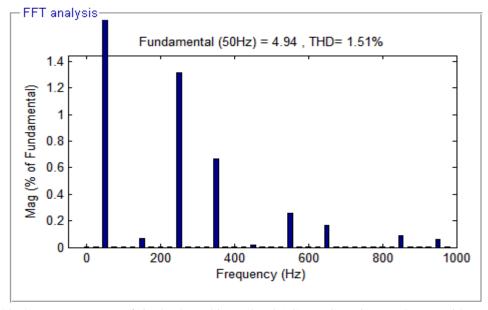

Fig. 17 and 19 shows the single-phase thirteen level output phase voltage and current of proposed ACMLDCL inverter using UMSVMT fed RL-load with a modulation index of 0.866 and Fig.18 and 20 shows the corresponding THD analysis, from the Fig's 18 and 20 it is noticed that the harmonic distortion of 10.35 % is present in phase voltage and 1.51 % in phase current of proposed ACMLDCL inverter.

Fig. 17 Output phase voltage of single phase thirteen level ACMLDCL using UMSVMT with RL-Load

Volume 6 Issue II, February 2018- Available at www.ijraset.com

Fig. 18 Phase voltage THD of single phase thirteen level ACMLDCL using UMSVMT with RL-Load

Fig. 19 Output phase current of single phase thirteen level ACMLDCL using UMSVMT with RL-Load

Fig. 20 Phase current THD of single phase thirteen level ACMLDCL using UMSVMT with RL-Load

#### V. COMPARISON OF RESULTS

A summary of THD and fundamental output voltage of proposed single phase thirteen level ACMLDCL inverter with their modulating techniques are presented in table 2 using USMT and modified UMSVMT with unipolar triangular carriers and it is concluded that proposed ACMLDCL inverter using UMSVMT has given good fundamental output voltage with less THD fed R and RL-loads when compared to USM technique.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887

Volume 6 Issue II, February 2018- Available at www.ijraset.com

Table ii. Comparison of results

|            | ACMLDCL inverter fed R-Load |         |         | ACMLDCL inverter fed RL-Load |         |         |         |         |

|------------|-----------------------------|---------|---------|------------------------------|---------|---------|---------|---------|

| Modulating | Output                      | Voltage | Output  | Current                      | Output  | Voltage | Output  | Current |

| Techniques | Voltage                     | THD     | Current | THD                          | Voltage | THD     | Current | THD     |

|            | (V)                         | (%)     | (A)     | (%)                          | (V)     | (%)     | (A)     | (%)     |

| USMT       | 249.3                       | 11.88   | 4.98    | 11.88                        | 249.8   | 11.93   | 4.23    | 2.24    |

| UMSVMT     | 291                         | 10.30   | 5.82    | 10.30                        | 291.7   | 10.35   | 4.94    | 1.51    |

#### VI. CONCLUSION

The presented thirteen level ACMLDCL inverter can significantly eliminates half the number of switches, gate drivers compared with the traditional MLI counterparts. Despite a higher total VA rating of the switches, the proposed ACMLDC inverter is cost less due to the savings from the eliminated gate drivers and from fewer assembly steps because of the substantially reduced number of components, which also leads to a smaller size and volume. The operational principles of the proposed thirteen level ACMLDCL inverter are explained in detail and also the modulation techniques are employed successfully.

#### REFERENCES

- [1] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multi-level inverter: a survey of topologies, controls, and applications," IEEETrans. Ind. Electron, vol. 49, no. 4, pp.724–738, Aug. 2002

- [2] Gui- jiasu, senior member ,IEEE "Multilevel DC-Link Inverter", IEEE Trans. on Indapplications, vol.41, issue 4, pp.724-738,may/june 2005.

- [3] K. Corzine and Y. Familiant, "Anew cascaded multilevel H-bridge drive," IEEE Trans. Power Electron., Vol. 17, No.1, pp. 125-131, Jan. 2002.

- [4] W. A. Halim, N. A. Rahim, and M. Azri, "Selective harmonic elimination for a single-phase 13-level TCHB based cascaded multilevel inverter using FPGA," Journal of Power Electronics, Vol. 14, No. 3, pp. 488-498, May 2014.

- [5] E. Najafi and A. H. M. Yatim, "Design and implementation of a new multilevel inverter topology," IEEE Trans. Ind. Electron., Vol. 59, No. 11, pp. 4148-4154, Nov. 2012.

- [6] H. Belkamel, S. Mekhilef, A. Masaoud, and M. A. Naeim; "Novel three-phase asymmetrical cascaded multilevel voltage source inverter," IET Power Electron., Vol. 6, No. 8, pp. 1696-1706, Sep. 2013.

- [7] W. Yao, H. Hu, and Z. Lu, "Comparisons of space-vector modulation and carrier-based modulation of multilevel inverter," IEEE Trans. Power Electron., vol. 23, no. 1, pp. 45–51, Jan. 2008.

- [8] Rao, S.N.; Kumar, D.V.A.; Babu, C.S., "New multilevel inverter topology with reduced number of switches using advanced modulation strategies," Power, Energy and Control (ICPEC), 2013 International Conference on, vol., no., pp. 693-699, 6-8 Feb. 2013 doi: 10.1109/ICPEC.2013.6527745.

- [9] Ebrahimi J., Babaei E., and Gharehpetian G.B., A New Topology of Cascaded Multilevel Converters with Reduced Number of Components for High-Voltage Applications, IEEE Power Electron. Soc., vol. 26, no. 11, pp. 3109-3118, Nov.2011.

- [10] VNB Reddy,; Rao, S.N.; Babu, C.S., "Emphasis of Modulated Techniques for Cascaded Multilevel Inverters fed drive using FPGA," Power, Energy and Control (ICPEC), 2013 International Conference on, vol., no., pp. 686-692, 6-8 Feb. 2013 doi: 10.1109/ICPEC.2013.6527744.

- [11] S. Nagaraja Rao, D.V. Ashok Kumar, Ch. Sai Babu Multilevel Inverter Topology for Distributed Generation with High Voltage Gain Cascaded DC-DC Converter Journal of Advanced Research in Dynamical and Control Systems, Vol. 9 no.1pp. 264-282 2017.

- [12] Shantanu Chatterjee, "A Multilevel Inverter Based on SVPWM Technique for Photovoltaic Application," International Journal of Power Electronics and Drive System (IJPEDS), vol. 3, no. 1, pp. 62 -73, 2013.

#### **BIBLIOGRAPHY OF AUTHORS**

**S.NagarajaRao**was born in kadapa, India.He received the B.Tech degree in Electrical and Electronics Engineering from the Jawaharlal Nehru Technological University, Hyderabad in 2006; M.Tech (Power Electronics) from the same university in 2008.He is currently an Asst.Professor of the Dept. of Electrical and Electronic Engineering, M.S. Ramaiah University of Applied Sciences, Bangalore. He is currently working towards the Ph.D. degree in Electrical and Electronics Engineering, Jawaharlal Nehru Technological University Kakinada, Kakinada, A.P., INDIA. He has published several National and International Journals and Conferences. His area of interest power electronics and Electric Drives.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 6 Issue II, February 2018- Available at www.ijraset.com

**D. V. Ashok Kumar** was born in Nandyal, India in 1975. He received the B.E (Electrical and Electronics Engineering) degree from Gulbarga University and the M.Tech (Electrical Power Systems) from J.N.T.U.C.E, Anantapur and Ph.D in Solar Energy from same University. Currently he is working as Professor of the Dept. of Electrical and Electronic Engineering, R.G.M College of Engineering and Technology, Nandyal. He has published/presented technical research papers in national and international Journals/conferences. His field of interest includes Electrical Machines, Power electronics, Power systems and Solar Energy.

**Ch. Sai Babu** received the B.E. degree in Electrical and Electronics Engineering, in 1983 from AU College of Engineering Waltair, and the M.Tech. degree in Electrical Machines and Industrial Drives, in 1986 from the Regional Engineering College Warangal, and Ph. D. degree in Reliability Studies of HVDC Converters, in 1996 from Jawaharlal Nehru Technological University Hyderabad, A. P., INDIA. He is currently a Professor and Registrar, Jawaharlal Nehru Technological University Kakinada, Kakinada, A. P., INDIA. His research interests include Power Electronics, Power Semiconductor controlled electric drives, Resonant Converters, Multilevel Converters, Flexible AC Transmission Systems (FACTS), Power Quality and Solar PV Cell Technologies. He published over 200 scientific papers in international journals and conferences.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)