# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 6 Issue: III Month of publication: March 2018

DOI: http://doi.org/10.22214/ijraset.2018.3164

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue III, March 2018- Available at www.ijraset.com

### **Design of Parallel Self-Timed Adder**

M. Swathi<sup>1</sup>, Ravi Tiwari<sup>2</sup>

1, 2Dept. of Electronics and Telecommunication, SSGI Bhilai, CSVTU

Abstract: Adders being core building blocks in several VLSI circuits like microprocessors, ALU's etc. performance of adder circuit extremely affects the capability of the system. during this paper we tend to present the design and performance of Parallel Self-Timed Adder. it's supported a algorithmic formulation for acting multibit binary addition. The operation is parallel for those bits that don't would like any carry chain propagation. A sensible implementation is provided in conjunction with a completion detection unit. The implementation is regular and doesn't have any sensible limitations of high fanouts. The planned work principally geared toward minimizing the amount of transistors and estimation of varied parameters viz., area, power, delay for pasta. we've got conjointly designed four bit pasta as an example of planned approach. Simulations are performed exploitation MICROWIND three.1software and DSCH tool in 45nm CMOS technology that verify the utility and superiority of the planned approach over existing asynchronous adders.

Keywords: Binary adders, Parallel Adders, Asynchronous circuits, CMOS design.

#### I. INTRODUCTION

Addition is that the most typical and sometimes used mathematical process in silicon chip, digital signal processor, particularly digital computers. Also, it is a building blocks for synthesis all alternative arithmetic operations, so performance of any circuit is principally determined by speed of adder circuit. Circuits are also classified as synchronous or asynchronous. Synchronous circuits ar supported clock pulse whereas associate asynchronous circuit, or self-timed circuit, isn't ruled by a clock circuit or world clock instead, they usually use signals that indicate completion of operations [1] [6]. Such a system tends to own higher noise and magnetic attraction compatibility properties than synchronous systems because of the absence of a worldwide clock reference [4]. operation by itself doesn't imply low power, however usually suggests low power opportunities supported the observation that asynchronous circuits consume power only it's active. The synchronous adders perform slowly because of its progressive nature of operation and thus it's not counseled for quick and parallel adders, the essential building block of combinative digital adders may be a single bit adder, the only single bit adder may be a 0.5 adder (HA), the total adders (FA) ar single bit adders with the carry input and output, the total adders ar primarily product of 2 0.5 adders in terms of space, interconnection and time complexness. This paper proposes the planning of parallel self regular adder (PASTA), the planning of alimentary paste is regular and uses 0.5 adders at the side of multiplexers with minimum interconnection demand. The interconnection and space demand is linear that makes it possible to fabricate during a VLSI chip, the planning operates during a parallel manner for those bits that don't need any carry propagation. it's self regular, which implies that as presently because the addition is finished, it'll signal the completion of addition thereby overcoming the duration limitations.

#### II. SELF-TIMED ADDERS

Self-planned alludes to principle circuits that trust upon temporal order suppositions for the proper operation. Self- coordinated adders will presumably run speedier found the center of for component info, as early fulfillment police work will maintain a strategic distance from the need for the foremost pessimistic state of affairs prepacked defer element of synchronous circuits.

#### III. PARALLEL SELF TIMED ADDERS

In this space, the engineering and hypothesis behind pasta is displayed. The viper 1st acknowledges 2 data operands to perform half increases for each piece. on these lines, it emphasizes utilizing previous created convey and totals to perform halfincreases quite once till all convey bits are devoured and settled at zero level.

#### IV. PROPOSED WORK

#### A. Design Of Pasta

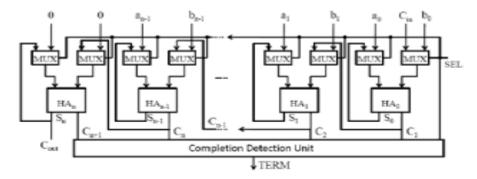

The design and theory behind pasta is given during this section. A] design of pasta the overall block diagram of the PArallel Self-Timed Adder (PASTA) is given in Fig.1. Multi bit adders are typically made from single bit adders using combinable and consecutive circuits for asynchronous or synchronous style.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue III, March 2018- Available at www.ijraset.com

Fig-1: General block diagram of Parallel Self-Timed Adder

The selection input for two-input multiplexers corresponds to the Req acknowledgment signal and can be one zero to one transition denoted by SEL. it'll ab initio choose the particular operands throughout SEL = zero and can switch to feedback/carry methods for resulting iterations using SEL = one. The adder initial accepts 2 operands to perform half-additions for every bit. after, it iterates using earlier generated carry and sums to perform half-additions repeatedly till all carry bits area unit consumed and settled at zero level.

#### B. State Diagrams

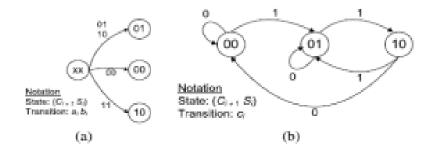

Fig-2: State diagrams for PASTA. (a) Initial phase. (b) Iterative phase.

In Fig.2, 2 state diagrams are drawn for the initial section and therefore the iterative section of the planned design. every state is described by (Ci+1 Si) try wherever Ci+1, Si represent perform and add values, severally, from the ith bit adder block. throughout the initial section, the circuit simply works as a combinatory ha operative in elementary mode. it's apparent that as a result of the employment of HAs rather than FAs, state (11) cannot seem. throughout the repetitive section (SEL = 1), the feedback path through multiplexer block is activated. The carry transitions (Ci) are allowed as over and over as needed to finish the recursion.

#### V. IMPLEMENTATION OF PASTA

In this section PASTA is implemented using CMOS technology. The general block diagram of Parallel Self-timed Adder includes following circuits modules:-

- 1) Half-Adder

- 2) Multiplexer

- 3) Completion detection circuit.

#### A. Bit Parallel Self-Timed Adder

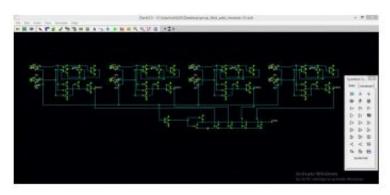

By using the proposed circuits discussed earlier we have designed a 4 bit parallel self-timed adder. The schematic of 4 bit PASTA is as shown in Fig3. The four bit PASTA module is formed by cascading the single bit adder module.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue III, March 2018- Available at www.ijraset.com

Fig-3:- Schematic of 4 bit PASTA

Fig-4:- Layout of 4 bit PASTA

#### VI. RESULTS & DISCUSSION

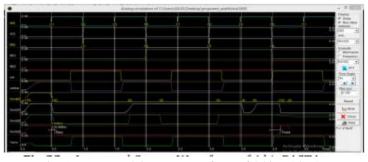

Simulation Results -The simulated results of enforced style for standard approach and projected approach of Parallel Self-Timed Adder are shown below. All the circuits are designed, simulated and also the performance is evaluated supported power, delay, frequency and area/size etc. Here for the planning using VLSI technology Microwind3.1 package is used

Fig-5: Input and Output Waveform of 4 bit PASTA

#### REFERENCES

- [1] Geer, "Is it time for clockless chips? [Asynchro-nous processorchips]," IEEE Comput., vol. 38, no. 3, pp. 18–19, Mar. 2005.

- $[2] \quad J. \ Spars\emptyset \ and \ S. \ Furber, Principles \ of \ Asynchronous \ Circuit \ Design. Boston, \ MA, \ USA: \ Kluwer \ Academic, 2001.$

- [3] P. Choudhury, S. Sahoo, and M. Chakraborty, "Im- plementation of basicarithmetic operations using cellular automaton," in Proc. ICIT, 2008,pp. 79–80.

- [4] M. Z. Rahman and L. Kleeman, "A delay matched approach forthe design of asynchronous sequential circuits," Dept. Comput.Syst.Technol., Univ. Malaya, Kuala Lumpur, Malaysia, Tech. Rep. 05042013,2013.

- [5] M. D. Riedel, "Cyclic combinational circuits," Ph.D. dissertation, Dept.Comput. Sci., California Inst. Tech-nol., Pasadena, CA, USA, May 2004.

- [6] R. F. Tinder, Asynchronous Sequential Machine Design and Analysis: A Comprehensive Development of the Design and Analysis of Clock-Independent State Machines and Systems. San Mateo, CA, USA: Morgan, 2009.

- [7] W. Liu, C. T. Gray, D. Fan, and W. J. Farlow, "A 250- MHz wavepipelined adder in 2-μm CMOS," IEEE J. Sol-id- State Circuits, vol. 29,no. 9, pp. 1117–1128, Sep. 1994.

- [8] F.-C. Cheng, S. H. Unger, and M. Theobald, "Selftimed carry-lookaheadadders," IEEE Trans. Comput., vol. 49, no. 7, pp. 659-672, Jul. 2000.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)