IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 6 Issue: IV Month of publication: April 2018

DOI: http://doi.org/10.22214/ijraset.2018.4173

### www.ijraset.com

Call: 🕥 08813907089 🔰 E-mail ID: ijraset@gmail.com

## Voltage Boosting using Modified Dickson Charge Pump VM Circuit

Ms. Shobana. D<sup>1</sup>, Rohini. G<sup>2</sup>, Sudha. A<sup>3</sup>, Suvetha. K<sup>4</sup>, Sweetlin. R<sup>5</sup> <sup>1, 2, 3, 4, 5</sup> *EEE*, *Panimalar Institute of Technology*

Abstract: DC converter with high voltage gain based on modified Dickson charge pump is proposed in this paper. The proposed converter has a two phase interleaved boost converter on its input side while having modified Dickson charge pump based voltage multiplier and inverter on its output side. This converter offers high voltage gain with the advantage of offering low voltage rating for the capacitors thereby reducing the capacitor size. Hence integration of renewable energy sources like solar panel to 400V DC bus can be made. The attached simulation results further explains the design and the component selection of the proposed converter. For instance, the converter outputs 240 V for an input of 12V

Keywords: Modified Dickson charge pump, interleaved boost converter, Voltage Multiplier(VM), high voltage gain, low voltage rating, solar panel.

#### I. INTRODUCTION

With the increase in energy demand, the renewable energy systems have gained popularity in both residential and commercial areas. Thus dc-dc converters have attracted the attention of many due to its capability of enhancing the voltage level and its tendency to act as an interface between low input source and distribution DC bus systems[1]-[4]. Currently, telecom centers, data centers and micro grids are among the emerging examples of dc distribution system[5]-[7]. It also finds its application in the HID lamps in automobiles, X-Ray power generators, Gas Discharge Tubes(GDT), UPS, etc., For achieving high voltage gains, conventional boost and buck-boost converters requires high duty ratios which results in high current stress in the switch thereby efficiency also reduces [8]-[11]. Due to the effect of power switches, rectifier diodes, and the equivalent series resistance of inductors and capacitors the step-up voltage gain is limited. Moreover, the extremely high duty-ratio operation will result in a serious reverse-recovery problem. Typically high-frequency transformers or coupled inductors are used to achieve high-voltage conversion ratios[12]-[18].But the transformer design is complicated and the leakage inductances increase for achieving larger gains, as it requires higher number of winding turns. This leads to voltage spikes across the switches and voltage clamping techniques are required to limit voltage stresses on the switches. Consequently, it makes the design more complicated. Villard voltage-doubler used to achieve high gain is a combination of the clamper and peak holder circuit[19]. It converts an input AC voltage to a doubled DC voltage across its output. Hence it requires an additional inverter to convert DC to AC which increases the complexity. One other method introduced by Cockcraft and Walton is a complex cascade voltage-doubler circuit which could produce a steady potential of about 700 kV which is about 3 times greater than the applied input voltage[20]. But it results in high coupling voltage drop due to the presence of series connected coupling capacitances which causes a small voltage gain for the circuit. To attain high-voltage conversion ratios, a new family of high-voltage-gain dc-dc power electronic converters that makes use of VM cells derived from Dickson charge pump circuit has been proposed[21]. The voltage rating of each VM cell capacitor is twice as that of its previous VM cell. Whenever even number of VM cells are used, the inductors ( $L_1$ ,  $L_2$ ) and switches ( $S_1$ ,  $S_2$ ) experience different current stresses whenever even number of VM cells are used.

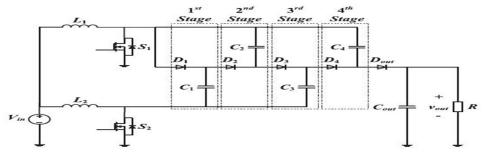

Fig.1. Proposed High-voltage-gain dc-dc converter in [19].

A high-voltage-gain dc-dc converter based on the modified Dickson charge pump VM circuit is introduced in this paper. This converter is capable of stepping up voltages as low as 20 to 400V. It can draw power from two independent dc sources as a multiport converter or one source in an interleaved manner. They draw continuous input current from both the input sources with low current ripple which is required in many applications, e.g., solar. In order to boost up the voltage several diode-capacitor stages are cascaded together which limits the voltage stresses on the switches, diodes, and capacitors. Due to the advantages listed above, these converters are good solutions to integrate solar panels into a dc micro grid. In conventional approaches, as the output voltage of PV panel is low, several panels are connected in series when connecting the PV array to the 400-V dc bus through conventional step-up converters. This results in reduced system reliability which can be addressed by connecting high-voltage-gain converter to each individual PV panel. In Section II the modified VM circuit based on Dickson charge pump has been discussed. The modes of operations have been discussed in Section III. In section IV the voltage gain for the propose dc converter has been derived. The component stress analysation and the supporting simulation results have been discussed in Section V. In section VI the comparative analysis of proposed converter and the converter shown in Fig. 1 is done. Finally the conclusion is discussed in Section VII.

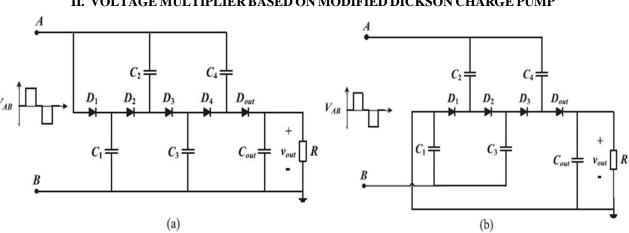

#### **II. VOLTAGE MULTIPLIER BASED ON MODIFIED DICKSON CHARGE PUMP**

The VM circuit based on Dickson charge pump [22], shown in Fig. 2(a), boosts the DC output voltage by the action of capacitors. The modified square wave voltage is applied as input to the circuit. The voltages multiplies in steps across each stage of the capacitors  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ . Their respective voltages are 80, 160, 240 and 320 V for an output voltage of  $V_{out}$  = 400 V. With a slight modification to the Dickson charge pump circuit, as shown in Fig. 2(b). For the same output voltage, the voltage stress across the capacitors in modified Dickson charge pump is reduced by mutually sharing the same. Also the inductors and switches has identical current stress which makes component selection process for the converter much easier. In comparison to the existing Dickson charge pump, the modified circuit has a diminution in the number of diodes One other added advantage is that due to the reduction in voltage stress across the capacitors its size reduces. In the proposed circuit, the voltage across the capacitors  $C_1, C_2, C_3$ , and  $C_4$  are 150, 50, 50, and 150 V respectively for an output voltage of  $V_{out} = 400$  V.

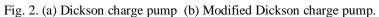

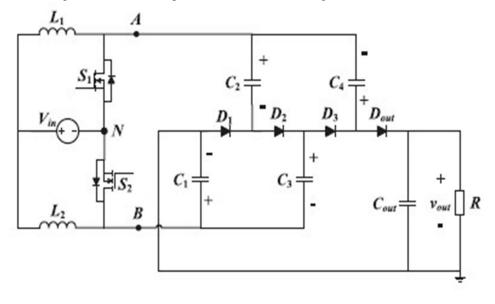

Fig. 3. Proposed high-voltage-gain dc-dc converter.

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue IV, April 2018- Available at www.ijraset.com

#### **III.OPERATION OF PROPOSED SYSTEM**

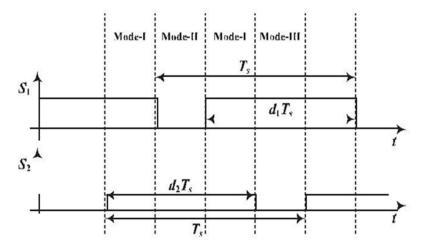

The converter proposed offers high voltage gain by means of using modified Dickson charge pump VM circuit and is made of two stages(see Fig. 3.). The first stage resembles a two phase interleaved boost converter which provides an MSW output across its terminals A and B. It is followed by the modified Dickson charge pump VM circuit which provides boosted voltage as output( $V_{out}$ ). The gating signals for switches  $S_1$  and  $S_2$  are shown. For the converter to operate normally switches  $S_1$  and  $S_2$  must have an overlap time such that both are ON and any one among them is ON at any instant. This can be achieved by means of using duty ratios greater than 50% for both switches and making one switch to operate 180° out of phase with other(see Fig 4). This results in three modes of operation as follows.

Fig. 4. Input boost converter switching signals for the proposed converter.

#### A. Mode I

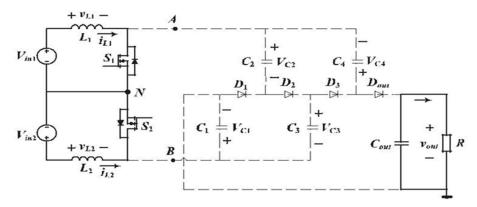

In mode I both the switches  $S_1$  and  $S_2$  are ON and the inductors  $L_1$  and  $L_2$  gets charged by means of input sources  $V_{in1}$  and  $V_{in2}$  respectively(see Fig. 5). Both the inductor current( $i_{L_1}$  and  $i_{L_2}$ ) increases linearly. Since all the diodes of the VM circuit are reverse-biased they are in OFF state. The voltages of the multiplier capacitors remain same and the output diode  $D_{out}$  is reverse biased. Hence, the load is supplied by the output capacitor.

Fig. 5. Proposed converter operation in mode I.

#### B. Mode II

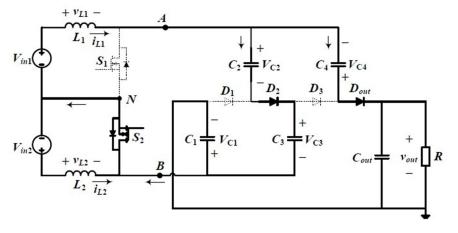

In this mode, switch  $S_1$  is OFF and switch  $S_2$  is ON. Diodes  $D_1$  and  $D_3$  are in OFF state as they are reverse biased, while diodes  $D_2$  and  $D_{out}$  are ON as they are forward biased (see Fig. 6). A part of inductor current  $i_{L_1}$  flows through capacitors  $C_2$  and  $C_3$ , thereby charging them. The remaining current flows through the capacitors  $C_4$  and  $C_1$ , discharging them to charge the output capacitor  $C_{out}$  and supply the load.

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue IV, April 2018- Available at www.ijraset.com

Fig. 6. Proposed converter operation in mode II.

#### C. Mode III

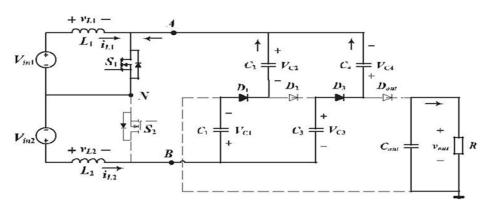

In this mode, switch  $S_1$  is ON and switch  $S_2$  is OFF. Diodes  $D_1$  and  $D_3$  are in ON state as they are forward biased, while diodes  $D_2$  and  $D_{out}$  are OFF as they are reverse biased(see fig. 7). Inductor current  $i_{L_2}$  flows through diode–capacitor VM cell capacitors  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ . Capacitors  $C_1$  and  $C_4$  are charged while discharging capacitors  $C_2$  and  $C_3$ . Here, the output capacitor supplies the load.

Fig. 7. Proposed converter operation in mode III

#### **IV. VOLTAGE GAIN OF THE CONVERTER**

In the proposed converter, the input power is transferred to the output by charging and discharging the VM circuit capacitors. For an ideal converter shown in Fig.3 the voltage gain of the converter can be derived as described later. For inductors  $L_1$  and  $L_2$ , the average voltage across the inductors according to volt–second balance can be written

$$V_{L_1} = V_{L_2} = 0 \tag{1}$$

Based on mode II, the volt-second balance of inductor  $L_1$  can be written as

$$V_{AN} = V_{C_2} + V_{C_3} = V_{out} - \left(V_{C_1} + V_{C_4}\right) = \frac{V_{in1}}{(1-d_1)}$$

(2)

Where  $d_1$  is the duty cycle of switch  $S_1$ .

Based on mode III, the volt-second balance of inductor  $L_2$  can be written as

$$V_{BN} = V_{C_1} - V_{C_2} = V_{C_4} - V_{C_3} = \frac{V_{in2}}{(1-d_2)}$$

(3)

Assuming capacitors  $C_2$  and  $C_3$  as identical, then the voltage across them will be equal which can be written as

$$V_{C_2} = V_{C_3} = \frac{1}{2} \times \frac{V_{in1}}{(1-d_1)} \tag{4}$$

By substituting (4) in (3), the voltage across the capacitors  $V_{C_1}$  and  $V_{C_2}$  can be derived as

$$V_{C_1} = V_{C_4} = \frac{1}{2} \times \frac{V_{in1}}{(1-d_1)} + \frac{V_{in2}}{(1-d_2)}$$

(5)

Finally, by substituting equation (5) into (2), the output voltage can be derived as

$$V_{out} = 2 \times \frac{V_{in1}}{(1-d_1)} + 2 \times \frac{V_{in2}}{(1-d_2)}$$

(6)

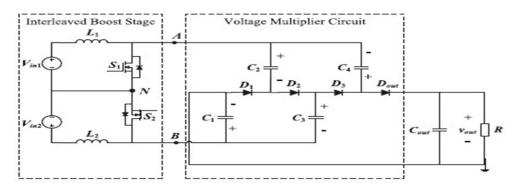

The proposed converter can be supplied from either two inputs (see Fig. 3) or only one input source. When a single input is used for the proposed converter, switches S1 and S2 have the same switching duty cycle d and are 180° out of phase from each other. The proposed converter with single source is shown in Fig. 8 and further the multiplier circuit capacitor voltages and the output voltage are simplified as shown below

$$V_{C_2} = V_{C_3} = \frac{1}{2} \times \frac{V_{in}}{(1-d)}$$

(7)

$$V_{C_1} = V_{C_4} = \frac{3}{2} \times \frac{V_{in}}{(1-d)}$$

(8)

$$V_{out} = 4 \times \frac{V_{in}}{(1-d)} \tag{9}$$

A 20-V input source at 80% switching duty cycle will generate an output voltage of 400 V using the proposed converter in Fig. 8. Capacitors *C*1 and *C*4 are charged to 150 V, and capacitors *C*2 and *C*3 are charged to 50 V.

Fig. 8. Proposed converter with single input source.

#### V. SIMULATION RESULTS OF THE PROPOSED CONVERTER

This part deals with the simulation waveforms during steady-state operation of the proposed converter and are purely based on the topology as shown in Fig.8, i.e., using a single voltage source to power the converter while operating both switches  $S_1$  and  $S_2$  of the two-phase interleaved boost stage at a fixed duty cycle d. using MATLAB the simulation model is built and the parameters used are shown in the below table.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue IV, April 2018- Available at www.ijraset.com

| TABLE I               |  |  |  |  |  |  |

|-----------------------|--|--|--|--|--|--|

| SIMULATION PARAMETERS |  |  |  |  |  |  |

| Parameter                        | Value  |  |  |

|----------------------------------|--------|--|--|

| Output Voltage                   | 400V   |  |  |

| Input Voltage                    | 20V    |  |  |

| Load Resistance                  | 800 Ω  |  |  |

| Duty cycle of switches S1 and S2 | 80%    |  |  |

| Switching frequency fsw          | 100kHZ |  |  |

| Boost inductors L1 and L2        | 100 μH |  |  |

| VM capacitors                    | 60 µF  |  |  |

| Output capacitor                 | 22 µF  |  |  |

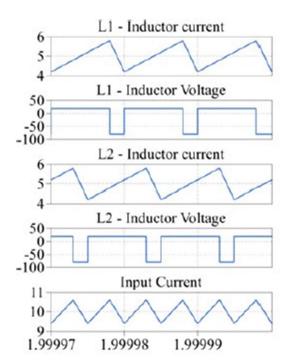

Fig. 9. Inductors *L*1 and *L*2 —current and voltage waveforms and input current.

A. Inductor

The inductor currents in both phases of the interleaved boost stages are similar. The average inductor currents can be calculated using (10). The rms value of the inductor currents used in the calculation of inductor copper losses can be calculated as shown in below equation

$$I_{L_1,avg} = I_{L_2,avg} = 2 \times \frac{I_{out}}{(1-d)}$$

(10)

$$I_{L_1,rms} = I_{L_2,rms} = \sqrt{\left(\frac{2 \times I_{out}}{(1-d)}\right)^2 + \left(\frac{V_{in} \times d}{2\sqrt{3} \times L \times f_{sw}}\right)^2}$$

(11)

The inductance required for a current ripple of  $\Delta I_L$  is given by

$$L_1 = L_2 = L = \frac{V_{in} \times d}{\Delta I_L \times f_{sw}}$$

(12)

From (10), (11), and (12), it is observed that both the inductors carry same amount of current and require same inductance for an assumed current ripple. Therefore, a similar inductor can be used for both  $L_1$  and  $L_2$ . Moreover as the rms currents of inductors  $L_1$  and  $L_2$  are equal, minimal conduction losses can be achieved in the inductors compared to other similar converters (see Fig. 1) having different values of currents flowing through their boost stage inductors. The inductor current and voltage waveforms obtained from PLECS MATLAB simulation are shown in Fig. 9. At 200W of output power, both the inductors carry a current of 5 A with a ripple of 1.6 A in each.

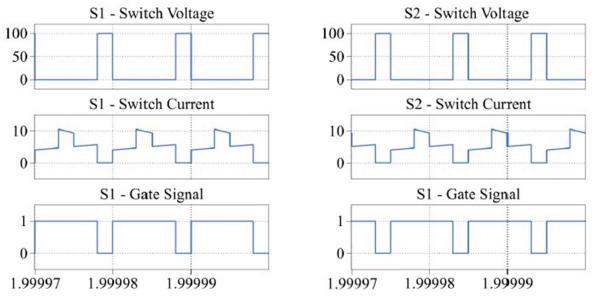

Fig. 10. Switch voltage, current, and gate signal waveforms: (a) switch *S*1 and (b) switch *S*2.

#### B. Input Current

A two-phase interleaved boost stage is supplied by an input source. Since on the input side it is a boost converter, the current is continuous. The input current ripple is even smaller because the two phases of the boost converter are  $180^{\circ}$  out of phase from each other which reduces the size of the input filter capacitor. The input current waveform of the proposed converter operating at 200W is shown in Fig. 9. It can be seen that the ripple of the input current is about 1.2 A even though inductor currents  $i_{L_1}$  and  $i_{L_2}$  have a ripple of 1.6 A each. The reason for this smaller input current ripple is both the boost switches being operated 180° out of phase from each other.

#### C. Switches

The maximum voltage observed across the switches in the proposed converter is equal to the output of its boost stage. This is a small number compared to the high output voltage of the proposed converter. The switch blocking voltages can be calculated using (13). As current in both the inductors is the same, the current stress on both switches is same as well. The average current in the switches can be calculated using (14)

$$V_{S_1} = V_{S_2} = \frac{V_{in}}{(1-d)}$$

(13)

$$I_{S_{1},avg} = I_{S_{2},avg} = 2 \times \frac{I_{out}}{(1-d)}$$

(14)

The waveforms of the switches in the proposed converter are shown in Fig. 10(a) and (b). Switches S1 and S2 have the same current and voltage stress as can be seen in the simulation waveforms. Since the converter in simulation is operating at 80% switching duty cycle with a 20 V input, the maximum voltage stress seen on both switches is only 100 V. Both switches  $S_1$  and  $S_2$  carry an average current of 5 A.

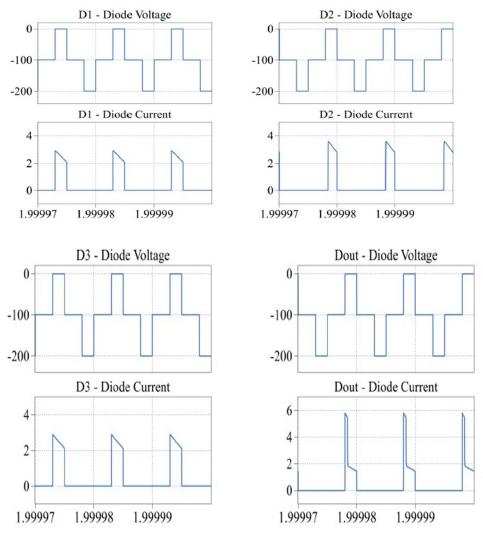

D. Diodes

Compared to the switches, the diodes experience two times higher blocking voltages as it depends on capacitor voltage of the VM circuit. But all the diodes experience the same blocking voltage and can be calculated using

$$V_{D_1} = V_{D_2} = V_{D_3} = V_{D_4} = V_{D_{out}} = \frac{2 \times V_{in}}{(1-d)}$$

(15)

The average current in the diode can be calculated using

$$I_{D_{1},avg} = I_{D_{2},avg} = I_{D_{3},avg} = I_{D_{out},avg} = I_{out}$$

(16)

The voltage and current waveforms of diodes  $D_{1}$ ,  $D_{2}$ ,  $D_{3}$  and  $D_{out}$  in the proposed converter are shown in Fig. 11. For the converter operating at 80% switching duty cycle and an input voltage of 20 V, the maximum blocking voltage seen by the diodes is 200 V. The diodes conduct either during mode II or during mode III of the converter operation. All the diodes carry an average current of 0.5 A, which is equal to the output current. Diodes  $D_{2}$  and  $D_{out}$  have different current waveforms. This is because of the voltage imbalance in the capacitors during the start of mode II. Only diode  $D_{out}$  initially conducts in order to charge the output capacitor and bring in a balance in the voltage. Once the voltage loops are balanced, then the current flowing through the diodes is dependent on the impedance of the capacitors.

Fig. 11. Diode voltage and current waveforms: (a) diode *D*1, (b) diode *D*2, (c) diode D3, and (d) output diode Dout.

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue IV, April 2018- Available at www.ijraset.com

VI. PROPOSED CONVERTER VERSUS HIGH VOLTAGE CONVERTERS USING BOOST STAGE AND VM CIRCUITS

In this section the comparison of the proposed converter with the other high voltage gain converter using boost stage and VM circuit is done. A comparison between the proposed converter and the converters from [8] to [11] has been made. The comparison is based on the voltage gain of the converters. With respect to the output voltage the voltage stresses on the components have been normalised to have a fair comparison. The comparison have been summarized in Table II.

| TOPOLOGY                              |                       | [8]              | [9]              | [10]                       | [11]                | PROPOSED         |

|---------------------------------------|-----------------------|------------------|------------------|----------------------------|---------------------|------------------|

|                                       |                       |                  |                  |                            |                     | CONVERTER        |

| V <sub>out</sub> / V <sub>in</sub>    | Cout                  | 3 - d            | 2                | 3 + d                      | 1                   | 4                |

|                                       | out                   | $\overline{1-d}$ | $\overline{1-d}$ | $\overline{1-d}$           | $\overline{d(1-d)}$ | $\overline{1-d}$ |

| V <sub>Switch</sub> /V <sub>Out</sub> | $S_1$                 | 1                | 1                | 1                          | 1-d                 | 1                |

|                                       |                       | $\overline{3-d}$ | 2                | $\overline{3+d}$           |                     | 4                |

|                                       | $S_2$                 | 1                | 1                | 1                          | 1-d                 | 1                |

|                                       |                       | $\overline{3-d}$ | 2                | $\overline{3+d}$           |                     | 4                |

| V <sub>diode</sub> /V <sub>Out</sub>  | <b>D</b> <sub>1</sub> | 1                | 1                | 2                          | 1-d                 | 1                |

|                                       |                       | $\overline{3-d}$ | 2                | $\frac{\overline{3+d}}{2}$ |                     | 2                |

|                                       | D <sub>2</sub>        | 1                | 1                | 2                          | d                   | 1                |

|                                       |                       | 3-d              | 2                | $\overline{3+d}$           |                     | 2                |

|                                       | D <sub>3</sub>        | 1                | -                | -                          | d                   | 1                |

|                                       |                       | $\overline{3-d}$ |                  |                            |                     | 2                |

|                                       | $D_4$                 | 1                | -                | -                          | -                   | -                |

|                                       |                       | 3 - d            |                  |                            |                     |                  |

|                                       | $D_0$                 | 1                | 1                | 2                          | -                   | 1                |

|                                       |                       | $\overline{3-d}$ | 2                | $\overline{3+d}$           |                     | 2                |

| V <sub>cap</sub> / V <sub>out</sub>   | C1                    | 1                | 1                | 1 + d                      | 1-d                 | 2<br>3<br>8      |

|                                       |                       | $\overline{3-d}$ | 2                | $\overline{3+d}$           |                     | 8                |

|                                       | C <sub>2</sub>        | 1                | 1                |                            | d                   | 1                |

|                                       |                       | $\overline{3-d}$ | 2                | $\overline{3+d}$           |                     | 8                |

|                                       | C <sub>3</sub>        | 1                | -                | 2                          | d                   | 1                |

|                                       |                       | $\overline{3-d}$ |                  | $\overline{3+d}$           |                     | 8<br>3<br>8      |

|                                       | $C_4$                 | 1                | -                | -                          | -                   | 3                |

|                                       |                       | $\overline{3-d}$ |                  |                            |                     | 8                |

|                                       |                       |                  |                  |                            |                     |                  |

Table Ii Comparison Of The Proposed Converter To Other High Voltage Gain Converters

From the table it is clear that the proposed converter has high voltage gain and less voltage stress on its switches and diodes. The real preferred standpoint with the proposed converter is the lesser voltage rating for its capacitors in contrast to the other converters. This incredibly adds to the cost and size reduction of the proposed converter. The proposed converter is likewise contrasted with a high voltage gain converter using Dickson charge pump VM cells [21]and is shown in table III. Both the converters are very similar in structure and operation. The high-voltage-gain converter utilizing the Dickson charge pump VM cells will be alluded to as reference converter in the accompanying sections of the paper. The two converters mainly differ in their component stresses. The comparison is in terms of component stress and size while the gain is 20 for both i.e, a 20 V input is stepped up to 400 v on the output side. In this comparison the converters supplied from single source is considered despite the fact that they can be supplied from dual input source.

Both converters accomplish a high voltage gain by means of charging and discharging the VM capacitors. They offer continuous input current, which can be owed to the two-phase interleaved boost topology on the input side. Since both the interleaved boost phases on the input side experiences same voltage and current stresses the proposed converter is symmetric. Additionally, a few of the capacitors in the VM circuit have similar voltage stress which reduces the effort and time during component selection of the system design. As the proposed converter offers slightly lower gain the switches have higher duty ratios. As a result the proposed converter has slightly higher voltage stress across the switches when compared to the reference converter.

| Component        | Parameter                         | Reference                                      | Proposed                                       |  |

|------------------|-----------------------------------|------------------------------------------------|------------------------------------------------|--|

| Component        | T arameter                        |                                                | converter                                      |  |

| T                |                                   | Converter[21]                                  |                                                |  |

| Input            | Current                           | Continuous                                     | Continuous                                     |  |

| Inductor         | Current                           | $i_{L_1} = 6 \text{ A}, i_{L_2} = 4 \text{ A}$ | $i_{L_1} = 5 \text{ A}, i_{L_2} = 5 \text{ A}$ |  |

| Switches         | itches Voltage V <sub>S</sub>     |                                                | $V_{S_1} = 100 \text{ V},$                     |  |

|                  |                                   | $V_{S_2} = 80 \text{ V}$                       | $V_{S_2} = 100 \text{ V}$                      |  |

|                  | Duty Cycle                        | $D_1 = D_2 = 75\%$                             | $D_1 = D_2 = 80\%$                             |  |

|                  | Current                           | $i_{S_1} = 6 \text{ A}, i_{S_2} = 4 \text{ A}$ | $i_{S_1} = 5 \text{ A}, i_{S_2} = 5 \text{ A}$ |  |

| VM capacitors    | Capacitance for                   | $C_1 = 12.5 \ \mu F,$                          | $C_1 = C_4 = 6.66 \mu\text{F},$                |  |

|                  | 1% voltage                        | $C_2 = 6.25 \ \mu F$ ,                         | $C_2 = C_3 = 20 \ \mu F$                       |  |

|                  | ripple                            | $C_3 = 4.17 \ \mu F$                           |                                                |  |

|                  |                                   | $C_4 = 3.125 \ \mu F$                          |                                                |  |

|                  | Voltage                           | $V_{C_1} = 80 \text{V},$                       | $V_{C_1} = V_{C_4} = 150$ V,                   |  |

|                  |                                   | $V_{C_2} = 160$ V,                             | $V_{C_2} = V_{C_3} = 50$ V                     |  |

|                  |                                   | $V_{C_3} = 240$ V, and                         |                                                |  |

|                  |                                   | $V_{C_4} = 320 \text{ V}$                      |                                                |  |

| Diodes           | Voltage                           | $V_{D_1} = 160 \text{ V},$                     | $V_{D_1} = 200 \text{ V},$                     |  |

|                  |                                   | $V_{D_2} = 160 \text{ V}$                      | $V_{D_2} = 200 \text{ V},$                     |  |

|                  |                                   | $V_{D_3} = 160$ V,                             | $V_{D_3} = 200$ V, and                         |  |

|                  |                                   | $V_{D_4} = 160$ V,                             | $V_{D_{out}} = 200 \text{ V}$                  |  |

|                  |                                   | and $V_{D_{out}} = 80V$                        |                                                |  |

| Output capacitor | Capacitance for 1% voltage ripple | $C_{out}$ = 1.875 $\mu$ F                      | $C_{out}$ = 1.875 $\mu$ F                      |  |

|                  | Voltage                           | $V_{Cout} = 400 \text{ V}$                     | $V_{C_{out}} = 400 \text{ V}$                  |  |

TABLE III Comparison Of Proposed And Reference Converter

The large-scale variance in the converters being compared is in their VM circuits. Both converters have four VM capacitors apart from the output capacitor. In the reference converter, the capacitor has linearly increasing voltage stress as observed from  $C_1$  to  $C_4$ . The voltages are 80,160, 240, and 320 V for capacitors  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$  respectively. The required capacitance for  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$  are 12.5, 6.25, 4.17, and 3.125 µF, respectively for a 1% ripple voltage in the VM capacitors. The proposed converter has littler voltage rating for the VM capacitors. Capacitors  $C_1$  and  $C_4$  have a voltage stress of 150 V and,  $C_2$ ,  $C_3$  have a voltage stress of 50 V. The required capacitance for  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$  are 6.66, 20, 20, and 6.66 µF, respectively for a 1% ripple voltage in the VM capacitors. Due to its VM circuit capacitors, the proposed converter has a smaller size compared to the reference topology. Ideally, this can be demonstrated by looking at the total energy of the VM capacitors, which can be calculated as follows:

$$E_{total} = \sum_{n=1}^{4} \frac{1}{2} \times C_n \times V_n^2$$

<sup>(17)</sup>

The VM capacitor of the reference converter has a total energy of 0.4 J whereas the proposed converter has 0.2 J. It is clear that when compared to the reference converter the capacitor of the proposed converter holds only 50% of the energy. Additionally the converter has one diode less in contrast to the reference converter. The same reverse blocking voltage of 200 V is experienced by all the diodes which is slightly greater than that of the diodes in the reference converter. This is because of slightly higher duty ratio of the proposed converter compared to the reference converter. The output capacitors of both the converters are the same as the output ratings are the same.

#### VII. CONCLUSION

A neoteric DC-DC converter with high voltage gain of 20 is being introduced here. The output will be 240V for a 12V input. This converter is suitable for renewable applications since it can draw power from more than one independent source. Thus, the proposed converter has two stages former is a interleaved boost converter while latter is a modified dickson charge pump. The

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue IV, April 2018- Available at www.ijraset.com

advantage is that the components present are exposed to same stress unlike in other boosters which puts design procedure at ease with components selection. The size of the voltage multiplier capacitor is comparatively very much reduced than that of normal Dickson charge pump voltage multiplier. The efficiency of this system is high about 96.8% which is far better when compared to boost converter or Dickson charge pump. This finds application in data centers, telecom centers, etc.,

#### REFERENCES

- V. A. K. Prabhala, P. Fajri, V. S. P. Gouribhatla, B. P. Baddipadiga, and M. Ferdowsi, "A DC–DC converter with high voltage gain and twoinput boost stages," IEEE Trans. Power Electron., vol. 31, no. 6, pp. 4206–4215, Jun. 2016

- [2] W. Hongfei, M. Tiantian, G. Hongjuan, and X. Yan, "Full-range softswitching- isolated buck-boost converters with integrated interleaved boost converter and phase-shifted control," IEEE Trans. Power Electron., vol. 31, no. 2, pp. 987–999, Feb. 2016

- [3] T. Kuo-Ching, H. Chi-Chih, and C. Chun-An, "A high step-up converter with voltage-multiplier modules for sustainable energy applications," IEEE J. Emerg. Sel. Topics Power Electron., vol. 3, no. 4, pp. 1100–1108, Dec. 2015

- [4] A. Ajami, H. Ardi, and A. Farakhor, "A novel high step-up DC/DC converter based on integrating coupled inductor and switched-capacitor techniques for renewable energy applications," IEEE Trans. Power Electron., vol. 30, no. 8, pp. 4255–4263, Aug. 2015

- [5] B. R. Marshall, M. M. Morys, and G. D. Durgin, "Parametric analysis and design guidelines of RF-to-DC Dickson charge pumps for RFID energy harvesting," in Proc. 2015 IEEE Int. Conf. RFID, pp. 32–3

- [6] W. Li, W. Li, X. Xiang, Y. Hu, and X. He, "High step-up interleaved converter with built-in transformer voltage multiplier cells for sustainable energy applications," IEEE Trans. Power Electron., vol. 29, no. 6, pp. 2829–2836, Jun. 2014

- [7] L. Wuhua, X. Chi, Y. Hongbing, G. Yunjie, and H. Xiangning, "Analysis, design and implementation of isolated bidirectional converter with winding-crosscoupled inductors for high step-up and high stepdown conversion system," IET Power Electron., vol. 7, pp. 67–77, 2014

- [8] X. Hu and C. Gong, "A high voltage gain DC-DC converter integrating coupled-inductor and diode-capacitor techniques," IEEE Trans. Power Electron., vol. 29, no. 2, pp. 789–800, Feb. 2014

- [9] R. Kadri, J.-P. Gaubert, and G. Champenois, "An improved maximum power point tracking for photovoltaic grid-connected inverter based on voltage-oriented control," IEEE Trans. Ind. Electron., vol. 58, no. 1, pp. 66–75, Jan. 2011. E. K. Sato, M. Kinoshita, Y. Yamamoto, and T. Amboh, "Redundant high density high-efficiency double-conversion uninterruptible power system,"IEEE Trans. Ind. Appl., vol. 46, no. 4, pp. 1525–1533, Jul./Aug. 2010.

- [10] S. V. Araujo, R. P. Torrico-Bascope, and G. V. Torrico-Bascope, "Highly efficient high step-up converter for fuel-cell power processing based on three-state commutation cell," IEEE Trans. Ind. Electron., vol. 57, no. 6, pp. 1987–1997, Jun. 2010

- [11] M. Berkhout and L. Dooper, "Class-D audio amplifiers in mobile applications,"IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 5, pp. 992–1002, May 2010

- [12] Z. Amjadi and S. S. Williamson, "Power-electronics-based solutions for plug-in hybrid electric vehicle energy storage and management systems," IEEE Trans. Ind. Electron., vol. 57, no. 2, pp. 608–616, Feb. 2010

- [13] L. G. Junior, M. A. G. Brito, L. P. Sampaio, and C. A. Canesin, "Integrated inverter topologies for low power photovoltaic systems," in Proc. Int.Conf.Ind. Appl., 2010, pp. 1–

- [14] A. Fukui, T. Takeda, K. Hirose, and M. Yamasaki, "HVDC power distribution systems for telecom sites and data centers," in Proc. 2010 Int. Power Electron. Conf., pp. 874–880

- [15] W. Li and X. He, "High step-up soft switching interleaved boost converters with cross-winding-coupled inductors and reduced auxiliary switch number," IET Power Electron., vol. 2, pp. 125–133, 2009

- [16] S. V. Araujo, R. P. Torrico-Bascope, G. V. Torrico-Bascope, and L. Menezes, "Step-up converter with high voltage gain employing three state switching cell and voltage multiplier," in Proc. Power Electron. Spec. Conf., 2008, pp. 2271–2277

- [17] R. A. da Camara, C. M. T. Cruz, and R. P. Torrico-Bascope, "Boost based on three-state switching cell for UPS applications," in Proc. Brazilian Power Electron. Conf., 2009, pp. 313–318

- [18] Nishanthi .V, Anitha Sampath Kumar ,"High Voltage DC-DC Converter Using Voltage Multiplier Cells (VMC)", IJSER ,vol . 02, no .3, Mar. 2014

- [19] Pankaj Bhutange, Nikita Hadke, Aditi Kathane, Anirudha Marothiya and Anurag Khergade, "Design and simulation of generation of high DC voltage using Cockraft Walton generator", IRJET, vol. 04, no. 3, Mar.2017.

- [20] X. G. Feng, J. J. Liu, and F. C. Lee, "Impedance specifications for stabledc distributed power systems," IEEE Trans. Power Electron., vol. 17, no. 2, pp. 157– 162, Mar. 2002

- [21] L. Huber and M. M. Jovanovic, "A design approach for server power supplies for networking," in Proc. Appl. Power Electron. Conf. Expo., 2000, pp. 1163– 1169

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)