IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 3 Issue: II Month of publication: February 2015 DOI:

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

# International Journal for Research in Applied Science & Engineering Technology (IJRASET) Low Power Design Techniques in CMOS Circuits

## : A Review

Agrakshi<sup>#1</sup>, Suman Rani<sup>#2</sup>

<sup>#</sup>Electronics and Communication Department, PPIMT Hisar, Haryana, India

*Abstract*— In the design of digital integrated circuits, power consumption is an important criterion. That indicates that low power circuits are now a days, emerging as an utmost priority in modern VLSI design. This is in contrast with the early 70s, when providing high speed operation with the least area was the main aim of design. But of course, other factors like area, propagation delay, leakage current etc. also can not be ignored in the design process. Out of these techniques, some are quite efficient in reducing static (leakage) power .This paper is prepared to review the available low power design techniques that are pivotal in designing various digital circuits.

Keywords— Leakage Power, Low Power, Power Dissipation, Power Management, Sleep Transistor

#### I. INTRODUCTION

Power consumption (dissipation) in digital circuits is a primary concern as it affects the chip life and circuit's efficiency due to overheating of circuit [27]. Thus there is a need to reduce the power dissipation as much as possible. There are different reasons for reducing power consumption depending upon a particular application. For instance, in the field of mobile communication, battery life needs to be maximized. This demands low power consumption by these devices. As the technologies are getting miniaturized ,power management has become a challenge. There are many techniques available today that help in achieving the aforementioned goal i.e. reducing power consumption. Some of them are power gating, clock gating while some are drain gating techniques. A review of some of these techniques as discussed in [3], [4], [8], [20], is done, mentioning their pros and cons.

#### **II. LOW POWER DESIGN TECHNIQUES**

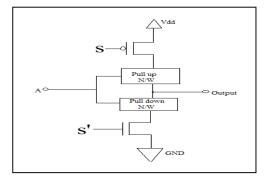

#### A. Sleep Transistor Technique

In the traditional sleep technique, additional 'sleep' transistors are inserted between power supply and ground. The 'sleep' pMOS transistor is placed between Vdd and the pull-up network of a circuit and an additional 'sleep' nMOS transistor is placed between the pull-down network of the circuit and GND. In idle mode, these sleep transistors turn off the circuit by cutting off the power rails thereby reducing the leakage power. In the active mode, however, these sleep transistors are turned on thereby providing a low resistance path and un-affecting the circuit performance.

#### Fig. 1 Sleep Transistor Circuit

1) Advantages: With a simple implementation, it is efficient in controlling leakage current.

2) *Disadvantages:* It is not suitable for state retention. It leads to floating output voltage in sleep state. Also, an increase in layout area and delay is observed. Moreover, it needs an additional control circuitry.

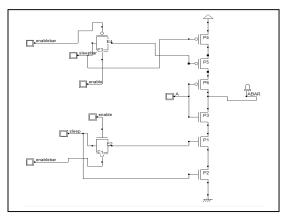

#### B. Power Gated Sleep Approach

A new approach is as discussed in [16], called power gated sleep method.

This method operates in 3 modes:

Active mode (AM).

Standby mode(SM).

Sleep to active mode transition (SAM).

In AM, logic '1' is applied to the sleep signal and both the sleep transistors E1, E2 remain ON. Then a low resistance path is offered by P1, P2 which makes the virtual ground (VGND) node potential, pulled down to the GND potential.

In SM, initially, the sleep signal is held at logic'1' and both the sleep transistors P1, P2 remain ON. Simultaneously, the control transistors E1 & E2 are switched OFF by giving logic'0'. In this case too, a low resistance path is offered by P1, P2 which makes the virtual ground (VGND) node potential, pulled down to the GND potential. As P1 and P2 are turned off, they produce a stacking effect thereby reducing the leakage current (power). The opposite occurs for the upper switch.

During SAM, P1 and P2 are turned ON after a small duration of time. That implies that the logic circuit is isolated from the ground for a short duration of time. During this duration the leakage current is reduced by the stacking effect.

Fig. 2 Power gated sleep method (for inverter)

1) Advantages: It takes the benefit of stack effect for reducing leakage current with appreciable performance without the need of a variable threshold device. It provides state retention.

2) Disadvantages: It increases the layout area and propagation delay.

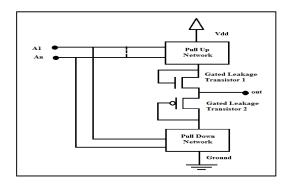

#### C. LECTOR Technique

Leakage Control Transistor (LECTOR) is another way to be used as a low power retention technique. In this approach, two extra LCTs: a pMOS and an nMOS are inserted within the circuit. It is a kind of drain gating technique. The gate terminal of each LCT is controlled by the source of the other. This effective stacking of transistors in the path from Vdd and GND helps in reducing leakage power and enhances the circuit performance. One of the LCT is always "near to its Cut-off" voltage region of operation regardless of any input combination.

1) Advantages: It utilizes both idle and active states of the circuit for leakage reduction. It uses stacking approach between the power supplies for leakage current reduction. Resistance path between the power rails is increased as one of the LCT is always in OFF state. No additional circuit is required for control. Exact logic state is maintained as it works in both the idle and active mode [15].

Fig. 3 LECTOR Technique.

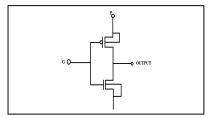

#### D. GALEOR Technique

It is another way of introducing stack effect in the logic gate to reduce leakage current. In this technique a gated leakage nMOS transistor is placed between output and pull up circuit and similarly a gated leakage pMOS transistor is placed between output and pulled down circuit [8].

GLTs used in this technique are high threshold voltage devices.

1) *Advantages:* It introduces stack effect between the power rails which helps in leakage control. With the introduction of variable threshold devices between the logic, it effectively reduces the leakage power.

2) *Disadvantages:* Its major disadvantage is that it reduces voltage swing at the output which further results in an increased propagation delay in the circuit.

Fig. 4 GALEOR Technique.

#### E. GDI (Gate Diffusion Input) Technique

GDI method is a highly efficient method that helps in reducing area, power and delay in digital circuits. It is based on the use of a simple cell as shown in Figure 8. A GDI cell consists of 3 inputs: G (common gate input of pMOS and nMOS), P (input to the source/drain of pMOS), and N (input to the source/drain of nMOS) [3].

#### Added features:

- The source of PMOS in a GDI cell is not connected to VDD and source of NMOS is not connected to GND. This increases the flexibility of circuit design with GDI cell.

- Bulks of both NMOS and PMOS are connected to N or P (respectively).

1) Advantages: It uses less number of devices as compared in CMOS and PTL. Also there is a significant reduction in power dissipation.

Complex logic functions can be easily 2-transistor implemented. Layout area occupied is less as compared to conventional techniques.

2) *Disadvantages:* It must be noticed that not all the functions are possible in standard P-Well CMOS process, but can be successfully implemented in Twin-Well CMOS technologies [3].

Fig. 5 Basic GDI Cell

TABLE I GDI Logic Functions

| S.  | Ν   | Р           | G | Output   | Function |

|-----|-----|-------------|---|----------|----------|

| No. |     |             |   |          |          |

| 1.  | В   | '1'         | Α | Abar+B   | Function |

|     |     |             |   |          | 1        |

| 2.  | ·0' | В           | Α | AbarB    | Function |

|     |     |             |   |          | 2        |

| 3.  | В   | <b>'</b> 0' | А | AB       | AND      |

| 4.  | '1' | В           | А | A+B      | OR       |

| 5.  | ,0, | '1'         | А | Abar     | NOT      |

| 6.  | C   | В           | А | AbarB+AC | MUX      |

#### F. AVL (Adaptive Voltage Level) Technique

An adaptive voltage level technique as described in [13], [20], [23], [24] can be used to control circuits either at the upper end of the cell (to bring down the supply voltage value) ,called AVLS Scheme; or at the lower end of the cell (to lift the potential of ground node ),called AVLG Scheme.

1) *AVLG Technique:* In this technique, two pMOS transistors and one nMOS transistor are connected in parallel. pMOS transistors are connected to ground while an input clock pulse is applied at the nMOS. This circuit is connected between pulled down network and ground. This increases the ground node potential. pMOS transistors are always in ON state since they are forward biased, while nMOS is switched between states. Thus leakage current flowing through nMOS of AVLG circuit is reduced and hence the power consumption is also reduced.

Fig. 6 AVLG Technique at Inverter Circuit

2) *AVLS Technique:* In this technique, two nMOS transistors and one pMOS transistor are connected in parallel. nMOS transistors are connected to supply voltage while an input clock pulse is applied at the pMOS. This circuit is connected between pulled up network and supply voltage. This reduces the supply node potential. nMOS transistors are always in ON state since they are forward biased, while pMOS is switched between states. Thus leakage current flowing through pMOS of AVLS circuit is reduced and hence the power consumption is also reduced.

Fig. 7 AVLS Technique at Inverter Circuit.

3) Advantages: This method is highly efficient in reducing both the leakage power and the dynamic power. It eliminates the use of variable threshold devices. This approach is highly advantageous for state retention.

4) Disadvantages: This method increases propagation delay. Also, the layout area increases.

#### **III. CONCLUSION**

Today, as the technology feature size is shrinking, it has become a challenge for the designers to maintain the power consumption in the tolerable limits without affecting much the other dependent parameters like area and delay overhead. In this paper, review of some of the commonly used low power design techniques is presented. Each of the discussed technique has its own merits and demerits. The designers may wisely select the one that best fits their requirement and design criteria.

#### **IV. ACKNOWLEDGMENT**

The authors feel privileged to thank their department and the concerned authorities for their constant guidance and support.

#### REFERENCES

- A.P. Chandrakasan, et al.,"Low-power CMOS digital design", *The IEEE Journal of Solid-State Circuits*, Volume: 27, Issue: 4, DOI: 10.1109/4.126534, Page(s): 473 484, April 1992.

- [2] Wei Liqiong, Chen Zhanping, M. Johnson, K. Roy and V. De, "Design and optimisation of low voltage high performance dual threshold CMOS circuit", *IEEE, Design Automation Conference, 1998*, Page(s): 489-494, 1998.

- [3] A. Morgenshtein, and A. Fish, "Gate-diffusion input (GDI) a technique for low power design of digital circuits: analysis and characterization", Circuits and Systems, 2002. ISCAS 2002. IEEE, Volume 1, DOI:10.1109/ISCAS.2002.1009881, Page(s): I 477 - I 480, 2002.

- [4] Narender Hanchate and Nagarajan Ranganathan, "LECTOR: A technique for leakage reduction in CMOS circuits", IEEE Transactions on a very Large Scale Integration(VLSI) Systems, Vol. 12, No. 2, Feb. 2004.

- [5] E.R. Menendez, D.K. Maduike, et al, "CMOS comparators for high-speed and low-power applications", *IEEE, Computer Design, ICCD 2006. International Conference*, Page(s): 76 – 81, 2006.

- [6] Behnam Amelifard, Farzan Fallah, et al., "Low-power fanout optimization using MTCMOS and multi-Vt techniques", IEEE, Low Power Electronics and Design, 2006. ISLPED '06., Page(s): 334-337, 2006.

- [7] M.S. Islam, M.S. Nasrin, N. Mansur, and N. Tasneem, "Dual stack method: A novel approach to low leakage and speed power product VLSI design", IEEE, Electrical and Computer Engineering (ICECE), 2010, Page(s), 89-92, Dec 2010.

- [8] I.S. Rao, D. Srinivas, B.R. Paramesh, and V.M. Rao, "Leakage current reduction 'Galeor & Lector' techniques", IJCEA, Vol. 2, Issue 02, May 2011.

- [9] A. Jalan, M. Khosla, et al., "Analysis of leakage reduction techniques in digital circuits", IEEE, India Conference (INDICON), Page(s): 1-4, Dec. 2011.

- [10] T. Izma, P. Barua, M.R. Rahman, P. Sengupta and M.S. Islam, "Novel approaches to low leakage and area efficient VLSI design", *IEEE*, Informatics, Electronics & Vision (ICIEV), 2012, Page(s) 316-319, May 2012.

- [11] S.K. Jaiswal, K. Verma, G. Singh and N. Pratihar, "Design of 8 bit comparator for low power application", IEEE, Computational Intelligence and Communication Networks (CICN), 2012, Page(s): 480-482, Nov. 2012.

- [12] A.J. Chowdhury, et.al, "A new leakage reduction method for ultra low power VLSI design for portable devices", IEEE- Power, Control and Embedded Systems (ICPCES), 2nd International Conference, Page(s): 1-4, Dec 2012.

- [13] S.Akashe, G. Sharma, V. Rajak and R.Pandey, "Implementation of high performance and low leakage half subtractor circuit using AVL Technique", IEEE, Information and Communication Technologies (WICT), Page(s): 27-31, 2012.

- [14] B. Dilip, P. Surya Prasad and R. S. G. Bhavani, "Leakage power reduction in CMOS circuits using leakage control transistor technique in nanoscale technology", *International Journal of Electronics Signals and Systems (IJESS)* ISSN: 2231- 5969, Vol-2 Issue-1, 2012.

- [15] A. Nagda, R. Prasad, T.N. Sasamal and N.K Vyas, "Leakage power reduction technique: A new approach", *IJERA*, Vol. 2, Issue 2, Page(s): 308-312, 2012.

- [16] C. Jagadeesh, R. Nagendra and Neelima Koppala, "Design & analysis of different types of sleepy methods for future technologies", (*IJETT*) Volume4, Issue 4, April 2013.

- [17] Laxmi Kumre, Ajay Somkuwar, and Ganga Agnihotri, "Design of low power 8 bit GDI magnitude comparator", *IASIR- IJETCAS, 4(1)*, Page(s): 102-108, March-May 2013

- [18] Vandana Choudhary, et al., "2 bit comparator using different logic style of full adder", IJSCE, Vol. 3, Issue 2, Page(s): 277-279, May 2013.

- [19] S. Ram, and R.R. Ahamed, "Comparison and analysis of combinational circuits using different logic styles", *IEEE, Computing, Communications and Networking Technologies (ICCCNT)*, 2013, Page(s): 1-6, July 2013.

- [20] D.K. Gautam, Dr. S.R.P. Sinha, and Er. Y.K. Verma, "Design a low power half subtractor using AVL technique based on 65nm CMOS technology", *IJARCET*, Vol. 2, Issue 2, Nov. 2013.

- [21] S.K. Mahammad Akram, et al., "Implementation of low leakage and high performance 8 bit ALU for low power digital circuits", IJCA, Vol. 82, No. 18, Page(s): 24-28, Nov 2013

- [22] M. Amala, and G.S.S. Prasad, "Design of low power 12-bit magnitude comparator", IJTEL, Vol. 2, No. 6, Dec. 2013.

- [23] T. Sood, and R. Mehra, "Design of low power half subtractor using 90µm CMOS technology", IOSR-JVSP, Vol. 2, Issue 3, Page(s): 51-56, 2013.

- [24] D.K. Gautam, Dr. S.R.P. Sinha, and Er. Y.K.Verma, "Design of a low power high speed full adder using AVL technique based on CMOS nanotechnology", *IOSR-JECE*, Page(s) 19-26, Vol. 8, Issue 1, 2013.

- [25] K. Linet, et. al, "Modified 4-bit comparator using sleep technique", IJCSET, Vol. 5, No. 05, May 2014.

- [26] Vijaya Shekhawat, Tripti Sharma and K. G. Sharma," Low power magnitude comparator circuit design, IJCA (0975 8887) Volume 94 No 1, May 2014.

- [27] Narendra Rawat, and Rakesh Jain, "Power reduction approach in combinational circuit(half and full subtractor)", *IJSR*, Volume 3, Issue 7, July 2014, Page(s): 1104-1108.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)