IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 6 Issue: V Month of publication: May 2018

DOI: http://doi.org/10.22214/ijraset.2018.5450

### www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

## Modified SEPIC Convertor based Induction Motor Drive

Ms.Soshya.c<sup>1</sup>, Mr. V. Jethose<sup>2</sup>

<sup>1</sup>*M.E Power Electronics &Drives*<sup>#1</sup> *JCT college of Engineering & Technology Pichanur, Coimbatore, Tamil Nadu* <sup>2</sup>*Professor & Head, EEE Department*<sup>#2</sup> *JCT College of Engineering & Technology Pichanur, Coimbatore, Tamil Nadu*

Abstract: The request for developing power quality of the AC system has drawn excessive interest during the recent years. The increased usage of power electronic devices, such as variable speed drives, uncontrolled rectifiers and other switching devices, affects the power quality of the utility grid significantly. The SEPIC converter is selected because of its numerous advantages over buck, boost and buck-boost converter. The bridgeless SEPIC converter has numerous advantages compared to the ordinary bridge converter. It reduces the complexity of the control circuit, can be easily implemented. The SEPIC converter operating in continuous conduction mode is explained in this paper. This SEPIC converter is capable of giving high power factor and low harmonic distortion. The implementation of this Bridgeless model in the SEPIC converter operating in Discontinuous conduction mode is the main outcome of my project and how it works. Applications: Balanced three phase equipment and single phase equipment, portable power tools, All lighting equipment, single phase (below 600W).

Keywords: Discontinuous conduction mode (DCM), Pulse width modulation (PWM), Voltage source inverter (VSI), Simulation

I.

#### INTRODUCTION

Development in the field of POWER ELECTRONICS is quick and appreciable. These developments have increased the nonlinearity of the electrical system. With increasing quantities of non-linear loads being added to the electrical systems, it has become necessary to maintain the power quality. The problems related power quality becomes an issue of concern. If electrical equipment operates correctly and reliably without being damaged or stressed, then the electrical power is of good quality. Power quality determines how efficiently the power is utilized by the consumer devices. Poor power quality can be described as any event related to the electrical network that ultimately results in a financial loss and reduce the life of the appliance connected to the supply of poor quality.

The induction motors are the commonly used motor in household appliances because of its rugged construction and low cost. The major problem associated with the induction motors are the low power factor and the high harmonic distortion. The power factor was found to be 0.667 and a huge amount of power is being wasted up and this affects the quality of power. The main objective of the project is to improve power factor and to reduce ripples in the input current and also to provide an efficient speed control method.

The proposed system is used for the single phase induction motor in ceiling fan or refrigerator. Normally the speed control of the single phase induction motor is done using triac. This is not an energy efficient technique as huge amount of energy is wasted in the speed control of induction machine. The above mentioned problem is overcome by means of a PFC SEPIC converter which operating in DCM and a PWM control technique is used for the smooth speed control of the induction machine. As a result the problem related to power factor and harmonic distortions were solved.

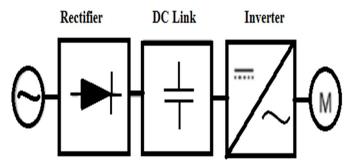

Fig 1 Block diagram of variable frequency drive

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue V, May 2018- Available at www.ijraset.com

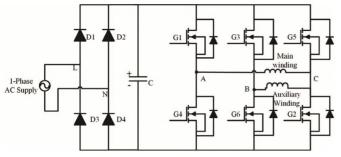

Fig.2 variable frequency drive for an induction motor

The fig 2 shows a variable frequency drive for a single phase induction motor. It consists of a DBR (diode bridge rectifier) a DClink Capacitor, inverter and the motor. The AC supply given is rectified by means of a bridge rectifier. The DC voltage is then stored in a DC link Capacitor. The DC voltage is then fed to a sine PWM inverter. The motor connection is shown in the figure. Out of three legs of the inverter, the main winding is connected between the leg A and leg C. The auxiliary winding is connected between the leg B and leg C. The modulating waveforms of switches in legs 'A' and 'B' are 180 degree out of phase and modulating waveform of leg 'C' has 90 degree phase difference with both 'A' and 'B' waveforms.

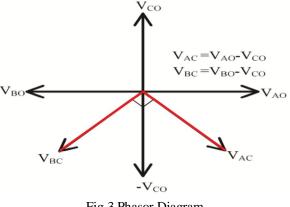

The resultant output voltage-phasor (fundamental component) will be as shown in Fig.3 Point 'O' is the hypothetical mid-point potential of the dc bus voltage. VAO, VBO and VCO are the inverter's pole voltages measured with respect to this hypothetical mid-point potential. From the voltage phasor diagram it is clear that the voltage across main winding ('VAC') is 90 degree phase shifted from the voltage across the auxiliary winding ('VBC'). The direction of rotation can be reversed by interchanging the main and auxiliary winding connection at legs 'A' and 'B'.

Fig.3 Phasor Diagram

The existing V/F technique provides efficient speed control and better efficiency, but power factor is very low and a huge amount of energy is wasted out. In order to rectify this problem a new topology is proposed, which is a PFC converter after the bridge rectifier.

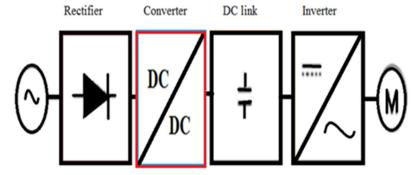

Fig.4 Block Diagram of Modified Sepic Converter

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue V, May 2018- Available at www.ijraset.com

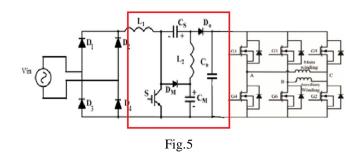

In the figure 5 a DC-DC SEPIC converter operating in DCM is added which will improve the power factor and reduces the harmonic distortion of the circuit. The efficiency of the total system is improved by the VFD. In normal cases a huge amount of power is wasted in the speed control of induction machine but by using variable frequency drive the power loss can be limited to some extent.

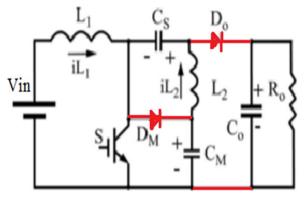

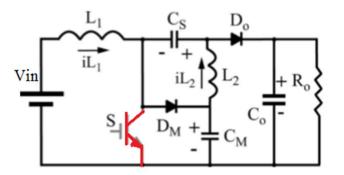

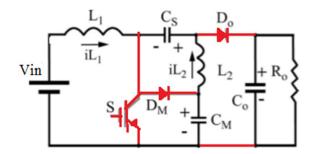

#### III. MODES OF OPERATION OF SEPIC PFC CONVERTER

The modified SEPIC dc–dc converter operating in DCM presents three operation stages. The steady state operation is considered and all the components are assumed to be ideal. The voltages across all capacitors are considered constant during a switching period, as an ideal voltage source. In DCM operation when the power switch is turned off the currents in all diodes of the circuit are zero. Therefore, the DCM operation occurs when  $D_O$  and  $D_M$  diodes are blocked before the switch turn-on. Considering the operation at steady state, the average voltage across the inductors  $L_1$  and  $L_2$  are zero and the sum of the input voltage  $V_{in}$  and capacitor  $C_S$  voltage is equal to the capacitor  $C_M$  voltage.

The three operation stages of Modified SEPIC in DCM are presented as follows:

#### $V_{C_M} = V_{in} + V_{C_S}$

Mode 1: When the switch is turned ON the full voltage comes across the input inductor. The voltage across the inductor L2 is equal to the voltage of the  $C_M$  Capacitor minus the  $C_S$  Capacitor. Both the inductor stores energy and have the same voltage across them. The two diodes are blocked during this stage.

Fig.6. First operating stage

| $V_{L_1} = V_{L_2} = V_{in}$                            | (7) |

|---------------------------------------------------------|-----|

| $\Delta i_{L_1} = \frac{V_{in} \times D}{L_1 \times f}$ | (8) |

| $\Delta i_{L_2} = \frac{V_{in} \times D}{L_2 \times f}$ | (9) |

Mode 2: The power switch is turned off at the instant  $t = t_1$ . The energy stored in the inductor  $L_1$  is transferred to the output through the capacitor  $C_S$  and the diode Do. There is also energy transfer to the capacitor  $C_M$  and diode  $D_M$ . The switch voltage is reduced to the capacitor voltage. The stored energy in the inductor  $L_2$  is transferred to the output and the capacitor  $C_M$  through the diodes  $D_O$ and  $D_M$ . The period  $(t_2-t_1)$  is defined as td and it is the transference period of the energy stored in the inductors  $L_1$  and  $L_2$  through the diodes  $D_O$  and  $D_M$ . The current through the diodes do and dm becomes zero at the end of this operating stage.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue V, May 2018- Available at www.ijraset.com

Fig.7. Second operating stage

| $V_{L_1} = V_{L2} = -V_{C_S}$                              | (10) |

|------------------------------------------------------------|------|

| $-\Delta i_{L_1} = \frac{-V_{C_S} \times D}{L_1 \times f}$ | (11) |

| $-\Delta i_{L_2} = \frac{-V_{C_S} \times D}{L_2 \times f}$ | (12) |

| Where $D_{td} = \frac{t_d}{T}$                             | (13) |

Mode 3: The current through the diode  $D_M$  and  $D_O$  are zero at this instant and the voltages across the inductors are zero. The current through them presents the same value. The mode 3 operation is finished when the power switch is turned on.

Fig.8. Third operating stage

| $V_{L_1} = V_{L_2} = 0$               | (14) |

|---------------------------------------|------|

| $\Delta i_{L_1} = \Delta i_{L_2} = 0$ | (15) |

The main theoretical waveforms are presented in Fig..8. The switch turn-on occurs with ZCS such as a classical dc–dc converter operating in DCM and the diodes do not present reverse recovery current. The maximum switch voltage is equal to the capacitor  $C_M$  voltage, and this voltage is lower than the output voltage. The  $L_1$  inductor average current is equal to the input current and the  $L_2$  inductor average current is equal to the output current. The average current in the capacitors  $C_S$  and  $C_M$  are null at steady state; thus, the average current of diodes  $D_M$  and  $D_o$  are equal to the output current.

#### A. Mathematical Analysis Operating as a DC DC Converters

The main equations of the modified SEPIC converter, operating in DCM with constant input voltage  $V_{in}$  are presented. A design procedure operating as pre-regulator with ac input voltage is presented based on the obtained equations.

#### B. Converter Static Gain and the Capacitors $C_S$ and $C_M$ Voltages

The output voltage is equal to the sum of the  $C_S$  and  $C_M$  capacitors voltages, as observed at the second operation stage presented in Fig. 6 and the  $C_M$  voltage is calculated as follows:

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 6 Issue V, May 2018- Available at www.ijraset.com

$$V_{C_M} = V_o - V_{C_S}$$

(16)

Replacing (6) in (16), the voltage across the capacitor  $C_S$  is obtained and presented as follows:

$$V_{C_S} = \frac{V_o - V_{in}}{2} \tag{17}$$

Replacing (6) in (13), the voltage across the capacitor CM is obtained and presented as follows:

$$V_{\mathcal{C}_M} = \frac{V_o + V_{in}}{2}.$$

(18)

The maximum switch voltage of the modified SEPIC converter is equal to the voltage across the CM capacitor calculated by (18). The voltage obtained from (18) for the modified SEPIC converter is always lower than the switch voltage of the classical boost and SEPIC converters because the input voltage is always lower than the output voltage in the modified SEPIC converter. Considering the operation at steady state and the average voltage across the inductors is equal to zero, the theoretical waveforms presented in Fig.3.8 shows that the positive area of the inductor voltage must be equal to the negative area as presented in (19) for the inductorL<sub>1</sub>. The converter duty cycle is equal to D and D<sub>td</sub> is the ratio between the diodes  $D_M$  and  $D_o$  conduction period  $t_d$  and the switching period T, as presented in (13)

$$V_{in} \times D \times T = (V_{C_M} - V_{in}) \times D_{td}$$

<sup>(19)</sup>

The voltage across the  $C_M$  capacitor is obtained from (19)

$$\frac{V_{C_M}}{V_{in}} = 1 + \frac{D}{D_{td}}$$

(20)

Replacing (18) in (20), the converter static gain is obtained as

$$\frac{V_o}{V_{in}} = 1 + \frac{2D}{D_{td}}.$$

(21)

The Cs capacitor voltage is obtained from (17) and (21)

$$\frac{V_{C_S}}{V_{in}} = \frac{D}{D_{td}}$$

(22)

The conduction period of the diodes  $t_d$  and the parameter  $D_{td}$  must be calculated for the static gain determination. As presented in Fig. 3.8, the currents through the diodes  $D_M$  and  $D_o$  are equal and the average value of this current is equal to the output current  $I_o$ . The current  $I_o$  can be calculated by (23), where  $I_{Dpk}$  is the peak value of the current through the diodes  $D_M$  and  $D_o$ .

$$I_o = \frac{I_{D_{pk} \times D_{td}}}{2} \tag{23}$$

The peak current at the output diode is equal to half of the sum of the inductors  $L_1$  and  $L_2$  current ripple, calculated as follows:

$$I_{D_{pk}} = \frac{\Delta i_{L_1} + \Delta i_{L_2}}{2} \tag{24}$$

Replacing (8) and (9) in (24), the output diode peak current is equal to

$$I_{D_{pk}} = \frac{1}{2} \left( \frac{V_{in} \times D}{L_1 \times f} + \frac{V_{in} \times D}{L_2 \times f} \right)$$

$$I_{D_{pk}} = \frac{V_{in} \times D}{2L_{eq} \times f}$$

(25)

(26)

$$L_{eq} = \frac{L_1 \times L_2}{L_1 + L_2} \tag{27}$$

Replacing (26) in (23), the conduction period of the output diode is obtained:

$$D_{td} = \frac{4I_0 \times L_{eq} \times f}{V_{in} \times D}$$

(28)

Considering

$$K = \frac{4 \times I_0 \times L_{eq} \times f}{V_{in}}$$

(29)

The conduction period of the output diode is equal to

$$D_{td} = \frac{\kappa}{D} \tag{30}$$

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue V, May 2018- Available at www.ijraset.com

Hence, the static gain and the voltage across the capacitors  $C_M$  and  $C_S$  are calculated by (31), (32), and (33)

$$\frac{V_o}{V_{in}} = 1 + \frac{2D^2}{K}$$

(31)

$$\frac{V_{C_M}}{V_{in}} = 1 + \frac{D^2}{K}$$

(32)

$$\frac{V_{C_S}}{V_{in}} = \frac{D^2}{K}$$

(33)

The design procedure of the converter must ensure the operation only in DCM for any line voltage angle and in all operation conditions in order to maintain the HPF operation. The operation in CCM without current-control loop results in input current distortion increasing the total harmonic distortion (THD). The conduction period of the power switch is represented by the interval  $(t_1 - t_0)$  in Fig.3.8 and also by the converter duty cycle (D·T). The conduction period of the output diode is defined by the interval  $(t_2 - t_1)$  and by the parameter ( $D_{td} \times T$ ). The limit for the DCM operation occurs when the sum of the switch conduction period and the diode conduction period is equal to the switching period (T), shown as follows:

$$D + D_{td} \le 1 \tag{34}$$

Replacing the parameter Dtd from (22) in (34), the maximum duty cycle for the DCM operation is obtained and presented as follows:

$$D \le \frac{v_{C_S}}{v_{C_S} + v_{in}}.$$

(35)

Also, considering the voltage across the capacitor  $C_s$  calculated by (17) and replacing in (35), the maximum switch duty cycle as a function of the input and output voltage is obtained

$$D \le \frac{V_o - V_{in}}{V_o + V_{in}} \tag{36}$$

The static gain of the modified SEPIC converter operating in CCM (q<sub>CCM</sub>) is calculated by

$$q_{\rm CCM} = \frac{V_o}{V_{in}} = \frac{1+D}{1-D}$$

(37)

The duty cycle obtained from (36) is equal to the value calculated by (37) because at the boundary of the conduction modes, the static gain obtained with the converter operating in DCM presents the same value obtained with the CCM equation. The value of the equivalent inductance ( $L_{eqcrit}$ ) for the boundary of CCM and DCM operation is obtained replacing (28) in (34) and is presented in (38) using the duty cycle calculated by (36). This inductance can also be calculated by (40) as a function of the input and output voltage, replacing (36) in (38)

$$L_{eqcrit} = \frac{(1-D) \times D \times V_{in}}{4f_o}$$

$$L_{eqcrit} = \frac{(V_o - V_{in})V_{in}^2 \times 1}{(V_o + V_{in})^2 2f_o}$$

(38)

#### IV. CONCLUSION

The use of a Variable Speed Drive for a speed control application usually offers an energy efficient and environmentally friendly solution. The best opportunities for energy savings, with subsequent economic savings, arise through the laws which govern the operation of centrifugal fans and pumps. Simple and straight forward VSD's, such as the PWM inverter drives, are available for applications where the speed control accuracy is not critical. The variable speed drive with variable frequency control method will offer new, low-cost solutions for light commercial and consumer applications. In this circuit at the input side a power factor controller circuit is used which improves the power factor of the total system. The total harmonic distortion was less. By using this technique we can save the money and utilize the power in an efficient manner. By using the variable frequency drive the losses associated with speed control can be reduced.

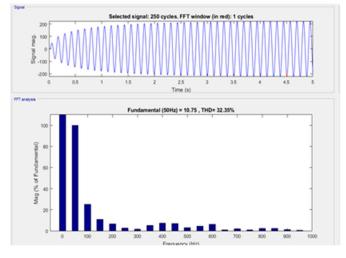

#### V. RESULTS AND DISCUSSION

The power factor was improved to 0.99 and the harmonic distortion was reduced from 88% to 5%. Using variable frequency drive the efficient speed control was possible. Thus the power loss in the speed control of induction motor was reduced by means of the

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 6 Issue V, May 2018- Available at www.ijraset.com

VFD. The input current waveform attains pure sinusoidal shape. This improved the power factor and has reduced the harmonic distortion.

#### VI. FUTURE SCOPE

Future work or the application can be done using the SEPIC in conduction mode. The power, switching losses and harmonic distortion can be reduced. Proposed converter presents a low input current ripple operating in DCM, and the switch voltage is lower than the output voltage. The switch voltage reduction increases the converter reliability. The hardware implementations can be made easier using these SEPIC converters.

#### REFERENCES

- [1] S. Ba-thunya, R. Khopkar, Kexin Wei, H.A.Toliyat (2001), "Single phase induction motor drives-a literature survey," proc. of IEEE International Electric Machines and Drives Conference 1)

- [2] Carlos Gabriel Bianchin, Roger Gules(2005), Member, IEEE, Alceu Andr'e Badin, Member, IEEE, and Eduardo F'elix Ribeiro Romaneli High-Power-Factor Rectifier Using the Modified SEPIC Converter Operating in Discontinuous Conduction mod

- [3] D. Jang and G. Choe(1995), "Improvement of Input Power Factor in ac Choppers using Asymmetrical PWM Technique," IEEE Transactions on Industrial Electronics, Vol. 42. 1)

- [4] D S Henderson,(2004) "Variable Speed Electric Drives Characteristics and Applications" Adjustable Frequency Control (Inverters) fundamentals application Consideration", Bulletin C870A.

- [5] D. S. L. Simonetti, J. Sebastiain, and J. Uceda(2003), "A small signal model for SEPIC, CUK and flyback converters as power factor preregulators in discontinuous conduction mode,"

- [6] E. H. Ismail(2009), "Bridgeless SEPIC rectifier with unity power factor and reduced conduction losses," IEEE Trans. Ind. Electron., vol. 56, no. 4, pp. 1147–1157

- [7] Liu,T.H., Wu, H.Ch. and Lin, M.T. (1997) "A Single phase induction motor drive with efficiency and torque improvement," proc. of IEEE International Symposium on Industrial Electronics, Vol.2, pp. 637-642.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)