# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 7 Issue: VIII Month of publication: August 2019

DOI: http://doi.org/10.22214/ijraset.2019.8016

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177

Volume 7 Issue VIII, Aug 2019- Available at www.ijraset.com

### Implementation of Inter-Integrated Circuit (I2C) Multiple Bus Controller on FPGA using VHDL

Mrs. Jaya Malviya<sup>1</sup>, Mr. Arif Mohammad<sup>2</sup>

<sup>1</sup>M Tech (VLSI Design), Gyan Ganga Institute of Technology and Sciences, Jabalpur, Madhya Pradesh <sup>2</sup>Dept. of Electronics and Communications Gyan Ganga Institute of Technology and Sciences Jabalpur, Madhya Pradesh

Abstract: The Inter - Integrated Circuit bus commonly called as I2C (I squared C) or I2C bus is a serial bus invented by Philips Semiconductors during early 80's for interconnecting integrated circuits. In this paper, the design and implementation of a I2C Multiple Bus Controller (IICMB) core is presented.

Keywords: I2CMB, I2C Protocol, Avalon Memory mapped Interfaces, I2C Communication (key words)

### I. INTRODUCTION

I2C bus was developed by Philips Semiconductors during 1980's for connecting computer peripherals together using a common protocol .This specification defines the architecture, hardware interface and parameterization options for the I2C Multiple Bus Controller (IICMB) core.

The IICMB core provides a low-speed, two-wire, bidirectionall serial bus interfaces compliant to industry standard I2C protocol. The key feature of the core is its ability to control several connected I2C buses effectively reducing complexity of system.

At any given moment the IICMB core works with a single I2C bus chosen from the range of connected buses (throughout this document such bus is called *selected bus*). When work with a particular selected bus is finished, user can switch to another one to continue configuring other peripherals. Every connected I2C bus is recognized by its number, or *bus ID*.

$Note: \ \, \text{The } \ \, \text{current} \ \, \text{version } \ \, \text{of the } \ \, \text{core } \ \, \text{supports master only functionality. Slave mode is under development.}$

### **Proposed Features**

- 1) Compatible with Philips I2C standard

- 2) Works with up to 16 distinct I2C buses

- 3) Statically configurable system bus clock frequency

- 4) Statically configurable desired clock frequencies of I2C buses

- 5) Multi-master clock synchronization

- 6) Multi-master arbitration

- 7) Clock stretching

- 8) Digital filtering of SCL and SDA inputs

- 9) Standard (up to 100 kHz) and Fast (up to 400 kHz) mode operation

- 10) Connects as 8-bit slave on Wishbone bus

- 11) Connects as 32-bit slave on Avalon-MM bus

### A. Architecture

The core is provided with three examples of its top level (iicmb\_m\_wb.vhd, iicmb\_m\_av.vhd and iic\_m\_sq.vhd). Two of them are designed for Wishbone and Avalon-MM buses, while third version is a sequencer based one for deeply embedded applications without any system bus at all.

In the center of the IICMB core is iicmb\_m.vhd module which integrates byte- and bit level master mode FSMs together with I2C bus multiplexer functionality. It is controlled with byte-level commands sent through the so-called Generic Interface.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue VIII, Aug 2019- Available at www.ijraset.com

interrupt

Fig. Block diagram of the Wishbone version of the top level

The wishbone vhd module connects Wishbone bus to register block (regblock vhd), which converts system bus accesses to byte-level commands of the Generic Interface. SCL and SDA inputs are digitally filtered to suppress unwanted spikes and to cope with long rising time of the I2C bus signals. The bus\_state.vhd modules independently monitor busy states of all connected buses.

The conditioner\_mux.vhd module, controlled by bus\_id input, performs switching between connected I2C buses. The mbit.vhd and mbyte.vhd implement bit-level and byte-level FSMs, generating appropriate SCL and SDA waveforms in accordance to I2C Bus Specification

### B. Operation

Some of the basic features on which have been implemented are as follows.

- Implementation of IICMB core which provides low-speed, two-wire, bidirectional serial bus interfaces compliant to industry standard I2C protocol.

- 2) "Manchester encoded UART" which enables running small peripherals with parasitic power derived from the TXD line, and allowing large clock differences typical of RC oscillators.

- 3) The key feature of the core is its ability to effectively reducing complexity of the system and control several connected I2C buses.

| Signal Name     | I/O    | Description                         |  |

|-----------------|--------|-------------------------------------|--|

| Clk             | Input  | Avalon-MM clock. Main clock fo      |  |

|                 |        | the controller                      |  |

| s_rst           | Input  | Synchronous reset. Active high.     |  |

| waitrequest     | Output | Wait request.                       |  |

| readdata[31:0]  | Output | Data output.                        |  |

| readdatavalid   | Output | Data validity indication.           |  |

| writedata[31:0] | Input  | Data input.                         |  |

| Write           | Input  | Indicates a write transfer.         |  |

| Read            | Input  | Indicates a read transfer.          |  |

| byteenable[3:0] | Input  | Enables specific byte lane(s) durin |  |

|                 |        | σ                                   |  |

Keeping in mind all the above specifications the key features of our design are

- 4) Works with up to 16 distinct I2C buses

- 5) Statically configurable system bus clock frequency

- 6) Statically configurable desired clock frequencies of I2C buses

- 7) Multi-master clock synchronization

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue VIII, Aug 2019- Available at www.ijraset.com

- A Company Resident

- 8) Multi-master arbitration

- 9) Clock stretching

- 10) Digital filtering of SCL and SDA inputs

- 11) Standard (up to 100 kHz) and Fast (up to 400 kHz) mode operation

- 12) Example connection as 32-bit slave on Avalon-MM bus

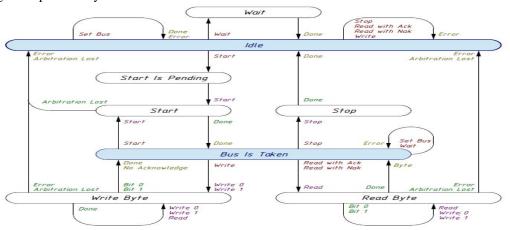

### C. Byte-level FSM

The byte-level FSM module (mbyte.vhd) communicates with upper level through so called Generic Interface. It accepts several byte-level commands listed in the Table 1 below.

After completion, each command is answered with an appropriate response. The main responsibility of the mbyte.vhd module is to translate byte-level commands to one or more commands for bit-level FSM (mbit.vhd).

Reception of a response is a mark of completion of the previously issued command. It is an error to send next command before previous command is responded. Such a command is ignored.

| Comma nd      | Code  | Para meter       | Description                                                                                                                  |  |  |

|---------------|-------|------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| Start         | "100" | _                | If bus is not captured yet: issue Start Condition and capture selected bus. If bus captured: issue Repeated Start Condition. |  |  |

| Stop          | "101" | _                | Issue Stop Condition and free selected bus.                                                                                  |  |  |

| Read With Ack | "010" | _                | Receive a byte with acknowledge.                                                                                             |  |  |

| Read With Nak | "011" | _                | Receive a byte with not-acknowledge.                                                                                         |  |  |

| Write         | "001" | Byte of data     | Transmit the byte given as a parameter.                                                                                      |  |  |

| Set Bus       | "110" | Bus numbe r (ID) | Connect to the specified bus (select bus).                                                                                   |  |  |

| Wait          | "000" | Millise<br>conds | Do nothing for specified amount of time.                                                                                     |  |  |

Byte-level commands

| Respons<br>e          | Code  | Para<br>mete<br>r  | Description                                                                 |

|-----------------------|-------|--------------------|-----------------------------------------------------------------------------|

| Done                  | "000" | _                  | Command completed.                                                          |

| Arbitrati<br>on Lost  | "010" | _                  | Arbitration lost. Selected bus is freed, FSMs are set to their idle states. |

| No<br>Acknow<br>ledge | "001" | _                  | Byte written got no acknowledge.                                            |

| Byte                  | "100" | Byte<br>of<br>data | Byte of data received.                                                      |

| Error                 | "011" | _                  | Something went wrong.                                                       |

Byte-level responses

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue VIII, Aug 2019- Available at www.ijraset.com

The following diagram depicts the byte-level FSM

Byte-level FSM

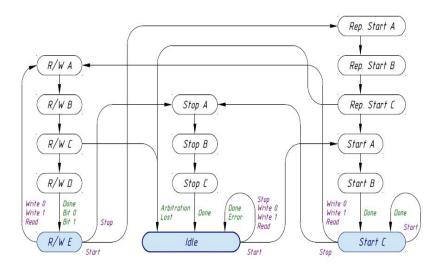

### D. Bit-level FSM

Bit-level commands and responses are hidden from the user of the core, but listed here for better understanding of how the two FSMs interact with each other.

Bit-level commands and responses have no parameters.

Level FSM

### II. IMPLEMENTATION RESULTS

### A. Setup 1

Top level module: iicmb\_m\_wb. vhd. Number of I2C buses  $(g_num_bus) = 1$ . System clock frequency  $(g_fck) = 100$  MHz. I2C bus clock frequency  $(g_fscl_0) = 100$  kHz.

Device Utilization Summary

| Family   | Device                | F <sub>max</sub> | Registe | Logics |

|----------|-----------------------|------------------|---------|--------|

| Virtex-6 | xc6vcx75t-<br>2-ff484 | 290MHz           | 649     | 757    |

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue VIII, Aug 2019- Available at www.ijraset.com

B. Setup 2

Top level module: iicmb\_m\_wb.vhd. Number of I2C buses (g\_num\_bus) = 16. System clock frequency (g\_f\_clk) = 100 MHz. I2C bus clock frequencies: g\_f\_scl\_0 = 100 kHz, g\_f\_scl\_1 = 120 kHz, g\_f\_scl\_2 = 130 kHz, g\_f\_scl\_3 = 200 kHz, g\_f\_scl\_4 = 50 kHz, others = 30 kHz.

| Family   | Device             | Fmax   | Registe | Logics |

|----------|--------------------|--------|---------|--------|

| Virtex-6 | xc6vcx75t- 2-ff484 | 325MHz | 154     | 264LUT |

### III. HIERARCHY OF MODULES

Hierarchy of modules with Avalon-MM top level

- A. iicmb\_pkg.vhd

- B. iicmb\_int\_pkg.vhd

- C. iicmb\_m\_av.vhd

- 1) avalon\_mm.vhd

- 2) regblock.vhd

- 3) iicmb\_m.vhd

- a) mbyte.vhd

- b) mbit. vhd

- c) conditioner\_mux.vhd

- d) conditioner.vhd

- i) filter. vhd

- *ii*) bus\_state.vhd

### Device Utilization Summary

| De vice etilization parimial y      |      |           |             |  |  |  |

|-------------------------------------|------|-----------|-------------|--|--|--|

| Slice Logic Utilization             | Used | Available | Utilization |  |  |  |

| Number of Slice Registers           | 182  | 12,480    | 1%          |  |  |  |

| Number used as Flip Flops           | 182  |           |             |  |  |  |

| Number of Slice LUTs                | 318  | 12,480    | 2%          |  |  |  |

| Number used as logic                | 307  | 12,480    | 2%          |  |  |  |

| Number using O6 output only         | 280  |           |             |  |  |  |

| Number using O5 output only         | 7    |           |             |  |  |  |

| Number using O5 and O6              | 20   |           |             |  |  |  |

| Number used as exclusive route-thru | 11   |           |             |  |  |  |

| Number of route-thrus               | 18   |           |             |  |  |  |

| Number using O6 output only         | 17   |           |             |  |  |  |

| Number using O5 and O6              | 1    |           |             |  |  |  |

| Number of occupied Slices           | 147  | 3,120     | 4%          |  |  |  |

| Number of LUT Flip Flop pairs used  | 375  |           |             |  |  |  |

| Number with an unused Flip Flop     | 193  | 375       | 51%         |  |  |  |

| Number with an unused LUT           | 57   | 375       | 15%         |  |  |  |

| Number of fully used LUT-FF pairs   | 125  | 375       | 33%         |  |  |  |

| Number of unique control sets       | 15   |           |             |  |  |  |

| Number of slice register sites lost | 22   | 12,480    | 1%          |  |  |  |

| to control set restrictions         |      |           |             |  |  |  |

| Number of bonded IOBs               | 59   | 172       | 34%         |  |  |  |

| IOB Flip Flops                      | 1    |           |             |  |  |  |

| Number of BUFG/BUFGCTRLs            | 1    | 32        | 3%          |  |  |  |

| Number used as BUFGs                | 1    |           |             |  |  |  |

| Average Fanout of Non-Clock Nets    | 4.36 |           |             |  |  |  |

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue VIII, Aug 2019- Available at www.ijraset.com

### IV. CONCLUSION

In this project work, the multi-master facility of I2C protocol is implemented successfully. Address resolution is the major concern while using multiple masters in I2C bus. Arbitration procedure must be perfect for the bus to work properly when dual masters are present. A dual master I2C bus controller system with an EEPROM 24CXX series as the slave devices has been developed for realizing both the read and write cycles of the I2C bus and tested. The design has got successfully implemented in Spartan 3A FPGA and the outputs are verified. Also DS1307 RTC is connected as the slave device and performed the WRITE and READ operations following I2C protocol. This design can be used in systems where multiple devices needs to be interconnected by ensuring with low complexity and efficient resource utilization.

### REFERENCES

- [1] I2C Bus Specification, Philips Semiconductor, version 2.1, January 2000.

- [2] DS1307 64 x 8, Serial, I2C Real Time Clock, Maxim integrated, 2008.

- [3] E. Allier, G. Sicard, L. Fesquet, and M. Renaudin, "A new class of asynchronous A/D converters based on time quantization," in Proceedings of International Symposium on Asynchronous Circuits and Systems, May 2003, pp. 196–205...

- [4] Prototyping of Dual Master I2C Bus Controller, Anagha A , M. Mathurakani, International Conference on Communication and Signal Processing, April 6-8, 2016, India.

- [5] Prof. Jai Karan Singh et al "Design and Implementation of I2C master controller on FPGA using VHDL," IJET, Aug-Sep 2012.

- [6] Raj Kamal, "Devices and Communication Buses for Devices Network," in Embedded system: Architecture programming and Design, Shalini Jha Ed. New Delhi, India: Tata McGraw-Hill Education, 2008, pp.160-165.

- [7] Implementation of I2C Master Bus Controller on FPGA, Bollam Eswari, N.Ponmagal, K.Preethi, S.G.Sreejeesh, International conference on Communication and Signal Processing, April 3-5, 2013, India

- [8] I2C Hardware Master Serial Interface for Asynchronous ADCs. Wojciech Andrysiewicz, Dariusz Ko'scielnik, Marek Mi'skowicz AGH University of Science and Technology. 2015 IEEE.

- [9] A.P.Godse, D.A.Godse, "Bus Standards," in Microprocessors and its Applications, 3rd Ed. Pune, India: Technical publications, 2008.

- [10] Systems with PIC Microcontrollers: Principles and Applications, 2nd Ed. Burlinton: Newnes, 2009, pp.307-327.

- [11] Spartan-3A/3AN FPGA Starter Kit Board User Guide, Xilinx, version1.1, 2008.

- [12] Vincent Himpe, "Historical background of I2C," in Mastering the I2C Bus, Aachen, Germany: Elektor Verlag publications, 2011.

- [13] Interfacing of digital TPH sensors with FPGA using I2C interface. Muhammed Raees PC, Anand Lokapure, Saraf Mandar N, B.Satyanarayana. 2016 IEEE Bombay Section Symposium.

- [14] BMP280 Digital Pressure Sensor Data sheet, Bosch Sensortec, October 15th, 2015.

- [15] AN10216-01 I2C Manual, PhilipsSemiconductor, March 2003.

- [16] Frank Vahid, "Hard ware Description Language," in Digital Design with RTL Design, Verilog and VHDL, 2nd Ed. Katie Singleton Ed. Hoboken, New Jersey: VP and Executive publisher, 2010, pp 487-532.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)