# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 3 Issue: IV Month of publication: April 2015

DOI:

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

### A 4-Dimensional Parity based Data Decoding Scheme for EDAC in Communication Systems

Vijay Tawar<sup>#1</sup>, Rajani Gupta<sup>\*2</sup>

\*Electronics and Communication Department, KNPCST, RGPV Bhopal, India

Abstract— The applications and use of hardware in wireless communication is increasing day by day. Portability of systems with data integrity during communication is the basic need of the systems in communication technology. This is a great force for the development of low power systems architectures. The wireless communication medium has various signals that can affect the low power communication signals of any system. So in wireless systems that operate on low power signals a good technique of data encoding and decoding is always preferred to use to transmit data through the medium. An effective data decoder is capable of identifying the changes that are caused in the transmitted data in the communication path and also capable to correct the data. Such an encoding-decoding technique is called as Error Detection and Correction (EDAC) Coding Technique. One of such technique that is most commonly used in the communication systems is based on the concept of Parity Encoding and Decoding. In the proposed work a 4-dimensional parity based encoding-decoding algorithm is presented. In this algorithm the error detection and correction logic is implemented by calculating parity of a data set in a matrix arrangement. The parity is calculated in the directions: horizontal, vertical, forward diagonal and backward diagonal. This algorithm is a low-complex hardware implementation design of error detection and correction code. The present work presents the hardware resource utilization on Xilinx FPGA devices.

Keywords - EDAC Code, Even Parity Encoder, FPGA, Hardware Resource Utilization, HVD Parity, Odd Parity, Xilinx

#### I. INTRODUCTION

In the modern communication systems wireless technology is emerging as a potential part of the systems. With the development of user application devices the amount of data transfer is also increasing tremendously. The data transfer among user devices is also increasing due to freely available software based user applications. This offers a greater possibility of portability and system up-gradation with the advancing system technologies. The wireless systems are more likely to be affected by the reception of noise signals by the receiving system antenna due to presence of wide complex signals in the communication environment. So an effective error identification scheme is required by the systems that perform control operations by using the received signal information. A better technique over the error detection technique also performs the correction in the received data when an error is detected in it. The change in the received data can be checked at the receiver end by using the received information that was added by the transmitter in the original data prior to its transmission. This extra information data is called as redundant data. One of the technique that offers a low complex hardware for implementing an effective error detection and correction algorithm is a multi-dimensional parity based scheme. In the proposed work a four dimensional parity based scheme is implemented on Xilinx field programmable gate array device to analyse its performance for multiple bit error detection and correction. The paper is organized as follows: Section-II presents the previous work review. Section-III presents the working of the proposed encoder and decoder with the help of the flow chart of the encoder and decoder. Section-IV presents the experimental and simulation results of the proposed encoder and the decoder with the help of waveform simulation diagram. Hardware utilization of the proposed design on Xilinx FPGA device is also summarized in Section-IV. Section-V presents the conclusion of the proposed work. Acknowledgement and References are presented after Section-V.

#### II. PREVIOUS WORK

A low complexity hardware design implementation is always preferred in the communication devices that have error detection and correction hardware. An implementation of a limited number of error detection and correction techniques is the Horizontal-Vertical-Diagonal Algorithm. This algorithm has an advantage of implementing effectively at both hardware and software level for detection and correction of errors. An implementation of multi-dimensional parity scheme is proposed in [2], [3], [4] and [5]

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

with multiple bit error detection and correction technique. A time redundancy based error detection and correcting circuit with reduced number of inputs and outputs in combinational circuit is presented in [6 and 7]. Similar work is presented in [8] for satellite applications. A software decision based method using 4-dimensional parity coding scheme is proposed in [9, 10 and 11]. A 3-bit error detection and correction method is proposed in [12]. A soft-decision based error correction code for NAND Flash Memory is presented in [13]. A HVD based error protection scheme is presented in [14]. An effective adjacent error correction scheme on matrix-based codes is presented in [15]. Cache and memory error detection, correction and reduction techniques for terrestrial servers and workstations is presented in [16].

#### III.PROPOSED H-V-D ENCODING-DECODING SCHEME

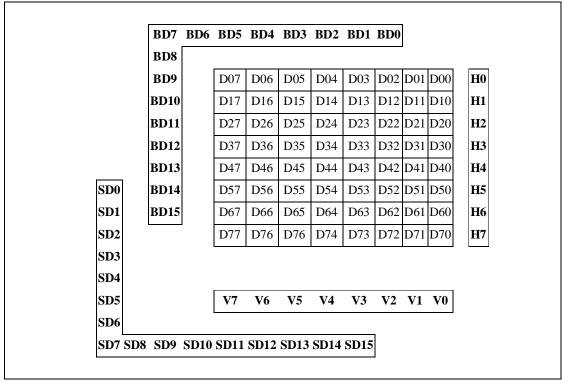

The parity encoder logic is the basic concept of the proposed design scheme. In a parity encoder a fixed length of input or a precalculated number of bits are taken as the input data. One redundant bit is added in the initial data and the logic value of the redundant bit depends on the type of parity encoding. For example, in even-bit parity encoding, if the number of logic-1 bits in a data sequence of length 8-bits is an odd number then the redundant bit is assigned a logic-1 value. Whereas, if the number of logic-1 bits in a data sequence of length 8-bits is an even number then the redundant bit is assigned a logic-0 value. In the 4-D parity scheme the data sequence is arranged in a matrix architecture. The encoded parity bit is generated in these four directions: horizontal, vertical, forward diagonal (slash diagonal) and backward diagonal (back slash diagonal). In the present work, the data set of 64-bits is first arranged in a matrix of size 8X8. This is shown in Fig-1. The H-V-D Parity bits are shown in Table-I. The presented scheme has 8-bits of parity in horizontal direction, 8-bits of parity in vertical direction, 15-bits of parity in slash diagonal direction and 15-bits of parity in back-slash diagonal direction. For a matrix of size "m x n", a total of bits that are generated in the four directions is (m) + (n) + (m+n-1) + (m+n-1) = 2 ( 2 (m+n) - 1).

Fig. 1 HVD Parity Scheme in 8X8 data matrix

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

#### TABLE I

LIST OF OUTPUT PARITY BITS IN PROPOSED HVD ENCODER

| HVD Parity Bits in the proposed Encoder |                                                                                      |  |  |  |  |  |  |

|-----------------------------------------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Horizontal Parity Bits                  | H0, H1, H2, H3, H4, H5, H6, H7                                                       |  |  |  |  |  |  |

| Vertical Parity Bits                    | V0, V1, V2, V3, V4, V5, V6, V7                                                       |  |  |  |  |  |  |

| Slash Diagonal Parity<br>Bits           | SD0, SD1, SD2, SD3, SD4, SD5, SD6, SD7, SD8, SD9, SD10, SD11, SD12, SD13, SD14, SD15 |  |  |  |  |  |  |

| Back Diagonal Parity<br>Bits            | BD0, BD1, BD2, BD3, BD4, BD5, BD6, BD7, BD8, BD9, BD10, BD11, BD12, BD13, BD14, BD15 |  |  |  |  |  |  |

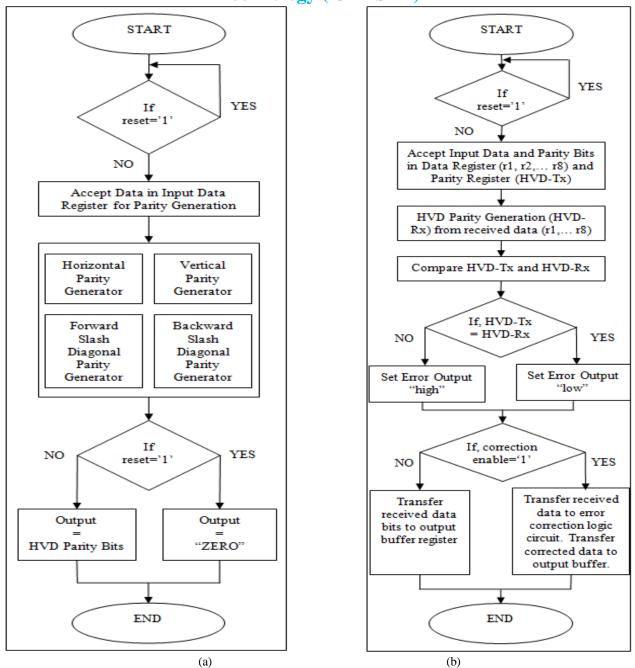

The proposed encoder is a clock synchronous hardware with a master reset input. The encoder operates to generate the 4-dimensional parity data on a logic low reset control input. If the reset input is logic high then the encoder sets all the internal registers and the output of the encoder to logic low value. The encoder involves four parallel hardware blocks to generate the parity bits. Each parity generator block is dedicated to generate particular directional parity bits. The Horizontal Parity Generator block generates horizontal parity bits "hp\_tx". The Vertical Parity Generator block generates vertical parity bits "hp\_tx". The Forward Slash Diagonal Parity Generator block generates slash diagonal parity bits "sd\_tx". The Backward Slash Diagonal Parity Generator block generates backward-slash diagonal parity bits "bd\_tx". The operational flow chart of the proposed encoder is shown in Fig-2(a).

The proposed decoder is also a clock synchronous hardware design with a master reset control input. The operational flow chart of the proposed decoder is shown in Fig-2(b). The decoder operates on the received data and the parity bits on a logic low reset control input. If the reset input is logic high then the decoder sets all the internal registers and the output of the decoder to logic low value. When enabled to operate, the decoder first utilizes the received data bits to generate the horizontal, vertical, slash diagonal and back-slash diagonal parity bits. Then the decoder compares the received parity bits with the generated parity bits. If the two sets of parity are found unequal an error indicator output is set to logic-high value otherwise it is set to logic-low value. If the error correction control input is enabled then transfer the data to error correction logic block. If the error correction enable input is set to logic low value the error correction will not be performed on the received data. In this condition only an information regarding presence or absence of error will be transferred by the previous block to the output using the error indicator output.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Figure 2: Operational Flow Chart (a) Proposed Encoder (b) Proposed Decoder

#### IV. EXPERIMENTAL RESULTS

The proposed design is simulated on Xilinx ISE Tool and the hardware design is modelled using VHDL language platform. The schematic block diagrams of the proposed Encoder and the Decoder are shown in Fig-3(a) and Fig-3(b) respectively.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig. 3 Schematic Block Diagram (a) Proposed Encoder (b) Proposed Decoder

The hardware synthesis of the proposed design is performed using Xilinx Synthesis Tool on Xilinx FPGA Device XC3S500E-4FG320. The hardware utilization summary of the Encoder and Decoder designs are presented in Table-II.

TABLE III

HARDWARE UTILIZATION OF PROPOSED ENCODER AND DECODER

| Hardwar       |       | Enc      | oder | Decoder |     |  |

|---------------|-------|----------|------|---------|-----|--|

| e<br>Resource | Total | Use<br>d | %    | Used    | 0/0 |  |

| Slices        | 4656  | 47       | 1    | 227     | 4   |  |

| Flipflops     | 9312  | 68       | 1    | 184     | 1   |  |

| LUTs          | 9312  | 90       | 1    | 329     | 3   |  |

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

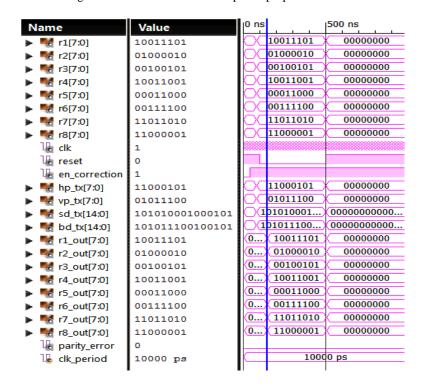

The simulation input and output of the proposed HVD Encoder are presented in Table-III. The data inputs of the proposed Decoder simulation for different conditions are given in Table-IV. The error bits are highlighted in the table. The test-bench based simulation result proposed encoder is shown in Fig-4. The test-bench based simulation result of proposed decoder for the three cases, with reference to Table-3, are shown in Fig-5, Fig-6(a) and Fig-6(b).

TABLE IIIII

SIMULATION INPUTS AND OUTPUTS OF PROPOSED ENCODER

| Direction    | Data Symbol<br>Abbreviation | Data Value<br>(Binary) |

|--------------|-----------------------------|------------------------|

|              | r1                          | 10011101               |

|              | r2                          | 01000010               |

|              | r3                          | 00100101               |

| Data In most | r4                          | 10011001               |

| Data Input   | r5                          | 00011000               |

|              | r6                          | 00111100               |

|              | r7                          | 11011010               |

|              | r8                          | 11000001               |

|              | hp_tx                       | 11000101               |

| Parity       | vp_tx                       | 01011100               |

| Output       | sd_tx                       | 101010001000101        |

|              | bd_tx                       | 101011100100101        |

TABLE IVV

SIMULATION INPUTS OF PROPOSED DECODER

| Decoder | Case-I   | Case-II            | Case-III          |  |  |  |

|---------|----------|--------------------|-------------------|--|--|--|

| 200000  | (without | (with              | (with             |  |  |  |

| Input   | error)   | error)             | error)            |  |  |  |

| r1      | 10011101 | 1 <b>11</b> 111111 | 10011101          |  |  |  |

| r2      | 01000010 | 01000010           | 01000010          |  |  |  |

| r3      | 00100101 | 00100101           | 00100101          |  |  |  |

| r4      | 10011001 | 10011001           | 10011001          |  |  |  |

| r5      | 00011000 | 00011000           | 00011000          |  |  |  |

| r6      | 00111100 | 00111100           | 00111100          |  |  |  |

| r7      | 11011010 | 11011010           | 11 <b>1</b> 11010 |  |  |  |

| r8      | 11000001 | 11000001           | 110 <b>1</b> 0001 |  |  |  |

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

| Name                          | Value           | 0 ns                                    | 1,,,,    | 200 ns       | 400 ns |

|-------------------------------|-----------------|-----------------------------------------|----------|--------------|--------|

| ▶ 🧏 r1[7:0]                   | 10011101        | 00                                      | 10011101 | 00000000     | )      |

| ▶ 🥦 r2[7:0]                   | 01000010        | 00                                      | 01000010 | 0000000      | )      |

| ▶ 🧲 r3[7:0]                   | 00100101        | 00                                      | 0010010  | 0000000      | )      |

| ▶ 🦷 r4[7:0]                   | 10011001        | 00                                      | 1001100  | 0000000      | )      |

| ▶ 🧲 r5[7:0]                   | 00011000        | 00                                      | 00011000 | 0000000      | )      |

| ▶ 🧲 r6[7:0]                   | 00111100        | 00                                      | 00111100 | 0000000      | )      |

| ▶ 🧲 r7[7:0]                   | 11011010        | 00                                      | 11011010 | 0000000      | •      |

| ▶ 🦷 r8[7:0]                   | 11000001        | 00                                      | 1100000  | 0000000      | •      |

| Ū₀ clk                        | 1               | ווווווווווווווווווווווווווווווווווווווו |          |              |        |

| 🖟 reset                       | 0               |                                         |          |              |        |

| Mp_tx[7:0]                    | 11000101        | 00                                      | 11000    | 00000000     |        |

| vp_tx[7:0]                    | 01011100        | 00                                      | 01011    | 00000000     |        |

| sd_tx[14:0]                   | 101010001000101 | 00                                      | 10101    | 000000000000 | 0000   |

| ▶ \$\frac{1}{8}\$ bd_tx[14:0] | 101011100100101 | 00                                      | 10101    | 000000000000 | 0000   |

| 🌡 clk_period                  | 10000 ps        |                                         | 1        | 0000 ps      |        |

|                               |                 |                                         |          |              |        |

Fig. 4 Waveform Simulation Output of proposed Decoder

Fig. 5 Waveform Simulation Output of proposed Decoder without error in received data (CASE-I)

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

| Name                                   | Value           | 0 ns                |           | 500 ns      | Nam        | ne /          | Value  |           | 0 ns                |           | 500 ns      |

|----------------------------------------|-----------------|---------------------|-----------|-------------|------------|---------------|--------|-----------|---------------------|-----------|-------------|

|                                        | 11111111        | $\overline{\alpha}$ | 111111111 | 00000000    |            | r1[7:0]       | 100111 |           | $\overline{\alpha}$ | 10011101  | 00000000    |

| r2[7:0]                                | 01000010 error  | ΚX                  | 01000010  | 00000000    | <b>▶</b> ■ |               | 110000 |           | ŎΖ                  | 11000010  | 00000000    |

| ▶ <b>™</b> r3[7:0]                     | 00100101        | ŌĊ                  | 00100101  | 00000000    | <b>▶</b> ■ |               | 001001 |           | ŌŌ                  | 00100101  | 00000000    |

| ▶ <b>™</b> r4[7:0]                     | 10011001        | $ \infty $          | 10011001  | 00000000    | ▶ 🥦        |               | 100110 | 01        | $\infty$            | 10011001  | 00000000    |

| ▶ 🦬 r5[7:0]                            | 00011000        | OC.                 | 00011000  | 00000000    | ▶ 🥦        | r5[7:0]       | 000110 | 00        | $\infty$            | 00011000  | 00000000    |

| ▶ 🦷 r6[7:0]                            | 00111100        | OC.                 | 00111100  | 00000000    | ▶ 🥦        | r6[7:0]       | 001111 | .00       | $\infty$            | 00111100  | 00000000    |

| ▶ 🧏 r7[7:0]                            | 11011010        | (XX                 | 11011010  | 00000000    | ▶ 🥦        | r7[7:0]       | 111110 | 10        | $\infty$            | 11111010  | 00000000    |

| ▶ 🧲 r8[7:0]                            | 11000001        | $  \propto$         | 11000001  | 00000000    | ▶ 🥦        | r8[7:0]       | 110100 | 01        | $\infty$            | 11010001  | 00000000    |

| Ū₀ clk                                 | 1               |                     |           |             | 16         | clk           | 1      | errors    |                     |           |             |

| 🌡 reset                                | 0               |                     |           |             | 16         | reset         | 0      |           |                     |           |             |

| len_correction                         | 1               |                     |           |             | 16         | en_correction | 1      |           |                     |           |             |

| hp_tx[7:0]                             | 11000101        | $ \infty $          | 11000101  | 00000000    | ▶ 🥦        | hp_tx[7:0]    | 110001 | .01       | $\infty$            | 11000101  | 00000000    |

| vp_tx[7:0]                             | 01011100        |                     | 01011100  | 00000000    | ▶ 🥦        | vp_tx[7:0]    | 010111 | .00       | $\infty$            | 01011100  | 00000000    |

| \$\bigs\frac{1}{8} \text{ sd_tx[14:0]} | 101010001000101 | $\bigcirc$ (1       | 01010001  | 00000000000 | ▶ 🥦        | sd_tx[14:0]   | 101010 | 001000101 | $\bigcirc$ (1       | 01010001) | 00000000000 |

| bd_tx[14:0]                            | 101011100100101 | $\bigcirc$ (1       | 01011100  | 00000000000 | ▶ 🥦        | bd_tx[14:0]   | 101011 | 100100101 | $\bigcirc$ (1       | 01011100) | 00000000000 |

| ¶ r1_out[7:0]                          | 10011101        | 0                   | 10011101  | 00000000    | ▶ 🥦        | r1_out[7:0]   | 100111 | .01       | 0                   | 10011101  | 00000000    |

| # r2_out[7:0]                          | 01000010        | 0                   | 01000010  | 00000000    | ▶ 🥦        | r2_out[7:0]   | 010000 | 10        | 0                   | 01000010  | 00000000    |

| # r3_out[7:0]                          | 00100101        | 0                   | 00100101  | 00000000    | ▶ 🥦        | r3_out[7:0]   | 001001 | .01       | 0                   | 00100101  | 00000000    |

| r4_out[7:0]                            | 10011001        | 0                   | 10011001  | 00000000    | ▶ 🥦        | r4_out[7:0]   | 100110 | 01        | 0                   | 10011001  | 00000000    |

| ¶ r5_out[7:0]                          | 00011000        | 0                   | 00011000  | 00000000    | ▶ 🥦        | r5_out[7:0]   | 000110 | 00        | 0                   | 00011000  | 00000000    |

| ¶ r6_out[7:0]                          | 00111100        | 0                   | 00111100  | 00000000    | ▶ 🥦        | r6_out[7:0]   | 001111 | .00       | (0)                 | 00111100  | 00000000    |

| ¶ r7_out[7:0]                          | 11011010        | 0                   | 11011010  | 00000000    | ▶ 🥦        | r7_out[7:0]   | 110110 | 10        | (O)                 | 11011010  | 00000000    |

| ¶ r8_out[7:0]                          | 11000001        | 0                   | 11000001  | 00000000    | ▶ 🥦        | r8_out[7:0]   | 110000 | 01        | 0                   | 11000001  | 00000000    |

| Vaparity_error                         | 1               | ш                   |           |             | 16         | parity_error  | 1      |           |                     |           |             |

| 🖟 clk_period                           | 10000 ps        |                     | 1000      | 0 ps        | 1.         | clk_period    | 10000  | ps        |                     | 1000      | 0 ps        |

|                                        | l I             | II                  | I         | I           |            |               | ı      |           | II .                |           |             |

|                                        |                 |                     |           |             |            |               |        |           |                     |           |             |

|                                        | (a)             |                     |           |             |            |               |        | (         | b)                  |           |             |

|                                        |                 |                     |           |             |            |               |        |           |                     |           |             |

Fig. 6 Waveform Simulation Output of proposed Decoder with error detection and correction: (a) CASE-II (b) CASE-III

#### V. CONCLUSIONS

In this paper a method is proposed for error correction and detection. The scheme detects and corrects all 2-bit errors and few cases of 3-bit and 4-bit errors. The proposed implementation also generates an output signal with an error indicator. This output enables the interface circuit to take a decision regarding the acceptance or rejection of the received data. In the future this algorithm can be improved to correct all the cases of errors with 3-bits and 4-bits.

#### VI.ACKNOWLEDGMENT

The author wish to thank Mr. Shailesh Raghuwanshi (Principal, KNPCST, RGTU, Bhopal) and Mr. Piyush Jain (Innovative Technology Design and Training Center, Bhopal) for sharing their views in line with the present work.

#### REFERENCES

- [1] www.xilinx.com

- [2] Vijay Tawar and Rajani Gupta, "FPGA Implementation of 4D-Parity based Data Coding Technique", IJRET, March 2015.

- [3] E. Yaakobi and T. Etzion, "High dimensional error-correcting codes", IEEE International Symposium on proceedings in Information Theory, 2010.

- [4] M. Rubinoff, "N-dimensional codes for detecting and correcting multiple errors", Communications of the ACM, Volume-4, Number-12, pp. 545-551, 1961.

- [5] T. F. Wong and J.M. Shea, "Multi-dimensional parity check codes for bursty channels", IEEE International Symposium on proceedings in Information Theory, 2001.

- [6] Fernanda Lima, Luigi Carro, Ricardo Reis, "Designing Fault Tolerant Systems into SRAM-based FPGAs", DAC Anaheim, California, June 2-6, 2003.

- [7] C. Argyrides, H. R. Zarndi, D K Pradhan, "Multiple upsets tolerance in SRAM Memory", International Symposium on Circuits and Systems, New Orleans, 2007.

- [8] Y. Bentoutou, "Program Memories Error Detection and Correction On-board Earth Observation Satellites", World Academy of Science, Engineering and Technology, 2010.

- [9] M. Kishani, H.R. Zarandi, H. Pedram, A. Tajary, M. Raji and B. Ghavami, "HVD: Horizontal-Vertical-Diagonal error detecting and correcting code to protect against the soft errors", Design Automation for Embedded Systems, Volume-15, No 3-4, 2011.

- [10] M. Imran, Z. Al-Ars and G. N. Gaydadjiev, "Improving Soft Error correction capability of 4-Dimensional parity codes", 14th IEEE European Test

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Symposium, 2009.

- [11] S. Sharma and P. Vijayakumar, "", International conference on Proceedings in Devices, Circuits and Systems (ICDCS), 2012.

- [12] N.B. Anne, U. Thirunavukkarasu, and S. Latifi, "", International Conference on Proceedings in Information Technology: Coding and Computing (ITCC), 2004.

- [13] Guiqiang Dong, Ningde Xie and Tong Zhang, "Enabling NAND Flash Memory use Soft-Decision Error Correction Codes at Minimal Read Latency Overhead", IEEE Transactions on Circuits and Systems, Vol. 60, September 2013.

- [14] Mostafa Kishani, Hamid R. Zarandi, Hossein Pedram, Alireza Tajary, Mohsen Raji and Behnam Ghavami, "HVD: Horizontal-Vertical-Diagonal Error Detecting and correcting code to protect against soft errors", April 2011.

- [15] Costas A Argyrides, Pedro Reviriego, Dhiraj K Pradhan and Juan Antonio Maestro, "Matrix-based Codes for Adjacent Error Correction", IEEE Transaction on Nuclear Science, Vol. 4, August 2010.

- [16] A Charles W. Slayman, "Cache and Memory Error Detection, Correction and Reduction Techniques for Terrestrial Servers and Workstations", IEEE Transactions on Device and Material Reliability, Vol 5, September 2005

10.22214/IJRASET

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)