IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 7 Issue: IV Month of publication: April 2019 DOI: https://doi.org/10.22214/ijraset.2019.4205

www.ijraset.com

Call: 🕥 08813907089 🔰 E-mail ID: ijraset@gmail.com

# Performance of Cascaded MLI Fed Induction Motor Drive using SPWM technique

Lavanya Komma<sup>1</sup>, Gowtham Vasupalli<sup>2</sup>, Jagadeesh Kumar Thoota<sup>3</sup>, Shanmukha Prema Kumar Bailapudi<sup>4</sup> <sup>1</sup> Dept. of EEE, Assistant Professor, ANITS, Sangivalasa, Visakhapatnam, AP, India-531162 <sup>2, 3, 4</sup> Dept. of EEE, Student, ANITS.

Abstract: This paper presents performance of induction motor for five-level and seven-level inverter using cascaded H-bridge topology.

Mathematical model of asynchronous motor in d-q reference frame and analysis of five and seven level inverter is done. In this paper the THD values of line and phase voltages of five and seven level inverter and the speed and torque characteristics of induction motor using cascaded H bridge inverters is obtained .Sine PWM technique is used to control the performance of induction motor.

The main goal here is to implement the SEVEN level and FIVE level cascade H bridge inverters with less number of switches compared to other topologies. Using this scheme, we can control the speed and reduces the torque ripples of Induction motor. In this paper software implementation is performed by using MATLAB SIMULINK software.

Keywords: THD, Induction Motor, Cascaded H Bridge, Five and Seven level inverter.

# I. INTRODUCTION

Pulse width modulation inverters have been gained importance in high performance applications without requiring high ratings on individual devices as static variable compensators, drives and active power filters. Multilevel converters can be applied to utility interface systems and motor drives.

A Multilevel inverter divides the dc rail directly or indirectly, so that the output of the leg can be more than two discrete levels. As both amplitude modulation and pulse width modulation are used in this the quality of the output waveform gets improved with low distortion. The advantages of multilevel inverter are good power quality, low switching losses, reduced output and high voltage capability. Increasing the number of voltage levels in the inverter increases the power rating. The pulse width modulation schemes of multilevel inverters are classified into two types:

- *A.* Multicarrier sub-harmonic pulse width modulation (MC-SHPWM)

- B. Multicarrier switching frequency optimal pulse width modulation (MC-SFOPWM)

The MC-SHPWM diode clamped multilevel inverter strategy reduced total harmonic distortion and the MC-SFOPWM technique for multilevel inverter strategy enhances the fundamental output voltage. The Three main topologies of multilevel inverters are :

- 1) Neutral point clamped or Diode clamped

- 2) Flying capacitors

- *3)* Cascaded H Bridge

Among these cascaded H bridge multilevel inverter topology is the most attractive as they got a higher level of The aim is to increase the level number of the H bridge inverter such that the harmonic contents can be reduced as much as possible while keeping low switching frequencies and switching loses. Several identical H bridge cells are cascaded in series as per the requirements constitute a cascade H bridge this type of topologies are used for high power applications. Cascaded H Bridge is further classified into two types, they are 1. Symmetrical, 2.Asymmetrical. For symmetrical inverter the input dc voltages are equal in all the cascaded power cells and for asymmetrical inverter the input dc voltages are unequal. Advantages of multilevel inverters are:

- *a)* They are suitable for high-voltage and high current applications.

- b) They have higher efficiency since the devices can be switched at a low frequency.

- c) Power factor is close to unity for multilevel inverters

- d) No Electromagnetic Interference (EMI) problem exist

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 7 Issue IV, Apr 2019- Available at www.ijraset.com

## II. INDUCTION MOTOR DRIVE

AC asynchronous motor, also called as induction motor has become the most widespread electrical motor in use today. These facts are due to the induction motors advantages over the rest of the motors. The main advantage they do not need any mechanical commutator, leading to the fact that they are maintenance free motors. Induction motors also have low weight and inertia, high efficiency and a high overload capability. Therefore, they are cheaper and more robust, and less proves to any failure at high speeds. Furthermore, the motor can work in explosive environments because no sparks are produced. However, mechanical energy is more than often required at producing an infinitely variable induction motor speed drive is to supply the induction motor with the three phase voltages of variable frequency and variable amplitude. A variable frequency is required because the rotor speed depends on the speed of the rotating magnetic field provided by the stator. A variable voltage is required because the motor impedance reduces at low frequencies and consequently the current has to be limited by means of reducing the supply voltages.

#### III. MATHEMATICAL MODELING OF INDUCTION MOTOR

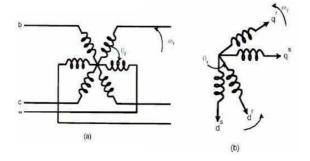

Fig.1.Induction Motor Stator and rotor windings

Three phase induction motor voltage equations in three phases and two phase axis are expressed as:

$$\begin{bmatrix} v_{qs}^{*} \\ v_{ds}^{*} \\ v_{ds}^{*} \\ v_{ds}^{*} \end{bmatrix} = \frac{2}{3} \begin{bmatrix} \cos(\theta) & \cos(\theta - 120^{\circ}) & \cos(\theta + 120^{\circ}) \\ \sin(\theta) & \sin(\theta - 120^{\circ}) & \sin(\theta + 120^{\circ}) \\ 0.5 & 0.5 & 0.5 \end{bmatrix} \begin{bmatrix} v_{qs}^{*} \\ v_{bs} \\ v_{cs} \end{bmatrix}$$

$$v_{as} = v_{qs}^{*}$$

$$v_{bs} = \frac{1}{2} v_{qs}^{*} - \frac{\sqrt{3}}{2} v_{ds}^{*}$$

$$v_{cs} = -\frac{1}{2} v_{qs}^{*} + \frac{\sqrt{3}}{2} v_{ds}^{*}$$

The inverse relation for the above is:

Applied 25 fight to the second second

$$v_{qs}^{s} = R_{s}i_{qs}^{s} + \frac{d}{dt}\Psi_{qs}^{s} \qquad v_{qs}^{s} = R_{s}i_{qs}^{s} + \frac{d}{dt}\Psi_{qs}^{s} \qquad zs$$

$$v_{ds}^{s} = R_{s}i_{ds}^{s} + \frac{d}{dt}\Psi_{ds}^{s} \qquad v_{ds}^{s} = R_{s}i_{ds}^{s} + \frac{d}{dt}\Psi_{ds}^{s}$$

=

$$v_{qs}^{s} = R_{s}i_{qs}^{s} + \frac{d}{dt}\Psi_{qs}^{s}$$

$$v_{ds}^{s} = R_{s}i_{ds}^{s} + \frac{d}{dt}\Psi_{ds}^{s}$$

The two phase ds-qs winding are transformed into the hypothetical winding mounted on de- qe axes. The voltages on ds-qs axes can be transformed into  $d_e$ -qe frame by following equations,

$$v_{qs} = R_s i_{qs} + \frac{d}{dt} \Psi_{qs} + \omega_e \Psi_{ds}$$

For rotor circuit,

$$v_{qr} = R_r i_{qr} + \frac{d\Psi_{qr}}{dt} + \left(\omega_e - \omega_r\right)\Psi_{dr}$$

$$v_{dr} = R_r i_{dr} + \frac{d\Psi_{dr}}{dt} - \left(\omega_e - \omega_r\right)\Psi_{qr}$$

Three Phase Induction Motor torque balance and developed torque equations are written as:

$$T_e = T_L + J \frac{d}{dt} \omega_m = T_L + \frac{2}{p} J \frac{d\omega_r}{dt}$$

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 7 Issue IV, Apr 2019- Available at www.ijraset.com

$$T_{e} = \frac{3}{2} \left(\frac{P}{2}\right) \left(\Psi_{dm} i_{qs} - \Psi_{qm} i_{ds}\right)$$

$$T_{e} = \frac{3}{2} \left(\frac{P}{2}\right) \left(\Psi_{ds} i_{qs} - \Psi_{qs} i_{ds}\right)$$

$$T_{e} = \frac{3}{2} \left(\frac{P}{2}\right) L_{m} \left(i_{qs} i_{dr} - i_{ds} i_{qr}\right)$$

$$T_{e} = \frac{3}{2} \left(\frac{P}{2}\right) \left(\Psi_{dr} i_{qr} - \Psi_{qr} i_{dr}\right)$$

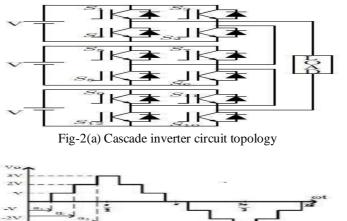

#### IV. ANALYSIS OF SEVEN LEVEL CASCADED H BRIDGE INVERTER

A cascaded multilevel inverter consists of a series of single-phase full bridge inverter units. Each separate DC source is connected to a full bridge inverter. The cascaded multilevel inverter does not require any voltage clamping diodes or voltage balancing capacitors like other two topologies. The seven-level multilevel inverter is obtained by cascading three full bridge inverter circuits. The three full bridge inverters are connected in series and a single-phase output is taken. Each full bridge is fed from separate DC source. The number of output levels m in each phase is related to number of full bridge inverter unit's n by, m/2n+1. Here the number of levels is seven, hence number of inverter circuits connected in series is three. The single phase seven-level topology of cascaded H bridge multilevel inverter is shown in Fig. 2(a) Each H-bridge is fed with the same value of DC voltage hence it can be called as symmetrical cascaded multilevel inverter. Each full bridge inverter can generate three different voltage outputs: +Vdc, 0, and -Vdc. The output voltage is synthesized by sum of three inverter outputs are at three angles. These three angles are used for giving pulses to twelve switches. The switching pattern for single phase seven-level topology of cascaded H-bridge multilevel inverter is shown in Table.

Fig. 2 (b) Seven-level output waveform

| 6               |    |     |     |   | 8  |     |     |  |

|-----------------|----|-----|-----|---|----|-----|-----|--|

| V <sub>0</sub>  | +V | +2V | +3V | 0 | -V | -2V | -3V |  |

| S <sub>1</sub>  | 1  | 1   | 1   | 0 | 0  | 0   | 0   |  |

| S <sub>2</sub>  | 1  | 1   | 1   | 1 | 0  | 0   | 0   |  |

| S <sub>3</sub>  | 0  | 0   | 0   | 0 | 1  | 1   | 1   |  |

| S <sub>4</sub>  | 0  | 0   | 0   | 1 | 1  | 1   | 1   |  |

| S <sub>5</sub>  | 0  | 1   | 1   | 0 | 0  | 0   | 0   |  |

| S <sub>6</sub>  | 1  | 1   | 1   | 1 | 1  | 0   | 0   |  |

| S7              | 0  | 0   | 0   | 0 | 0  | 1   | 1   |  |

| S <sub>8</sub>  | 1  | 0   | 0   | 1 | 1  | 1   | 1   |  |

| So              | 0  | 0   | 1   | 0 | 0  | 0   | 0   |  |

| S10             | 1  | 1   | 1   | 1 | 1  | 1   | 0   |  |

| S11             | 0  | 0   | 0   | 0 | 0  | 0   | 1   |  |

| S <sub>12</sub> | 1  | 1   | 0   | 1 | 1  | 0   | 1   |  |

|                 |    |     |     |   |    |     |     |  |

Table 1.Switching States for a seven level cascaded H Bridge inverter

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 7 Issue IV, Apr 2019- Available at www.ijraset.com

- A. Advantages

- 1) The number of possible output voltage levels is more than twice the number of DC sources (m = 2s + 1).

- 2) The series of H-bridges makes for modularized layout and packaging. This will enable the manufacturing process to be done more quickly and cheaply.

- 3) Possibility to implement soft-switching.

- B. Disadvantages

- 1) Separate DC sources are required for each of the H bridges. This will limit its application to products that already have multiple SDCSs readily available.

- 2) No common DC-bus.

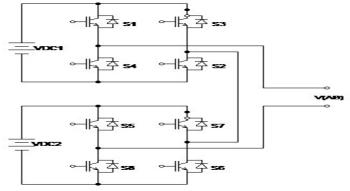

## V. ANALYSIS OF FIVE LEVEL CASCADED H BRIDGE MULTILEVEL INVERTER

Conventional cascaded multilevel inverters are one of the most important topologies in the family of multilevel and multi-pulse inverters. The cascade topology allows the use of several levels of DC voltages to synthesize a desired AC voltage. The DC levels are considered to be identical since all of them are fuel cells or photovoltaic, batteries, etc. [20]. It requires least number of components compared to diode-clamped and flying capacitors type multilevel inverters and no specially designed transformer is needed as compared to multi pulse inverter. Since this topology consist of series power conversion cells, the voltage and power level may be easily scaled. The concept of this inverter is based on connecting H-bridge inverters in series to get a sinusoidal voltage output. The output voltage is the sum of the voltage that is generated by each cell. The number of output voltage levels are 2n+1, where n is the number of cells. The switching angles can be chosen in such a way that the total harmonic distortion is minimized. An n level cascaded H bridge multilevel inverter needs 2(n-1) switching devices where n is the number of the output voltage level.

Fig3: Five Level Cascaded H Bridge

Cascade topology proposed in uses multiple dc levels, which instead of being identical in value are multiples of each other. It also uses a combination of fundamental frequency switching for some of the levels and PWM switching for part of the levels to achieve the output voltage waveform. This approach enables a wider diversity of output voltage magnitudes; however, it also results in unequal voltage and current ratings for each of the levels and loses the advantage of being able to use identical, modular units for each level.

| Table 2.Switching States for a | Five-level cascaded H Bridge inverter |

|--------------------------------|---------------------------------------|

|--------------------------------|---------------------------------------|

| Switches Turn On | Voltage Level |

|------------------|---------------|

| S1, S2           | +Vdc          |

| \$1,\$2,\$5, \$6 | +2Vdc         |

| S4,D2,S8,D6      | 0             |

| \$3,\$4          | -Vdc          |

| \$3,\$4,\$7,\$8  | -2Vdc         |

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 7 Issue IV, Apr 2019- Available at www.ijraset.com

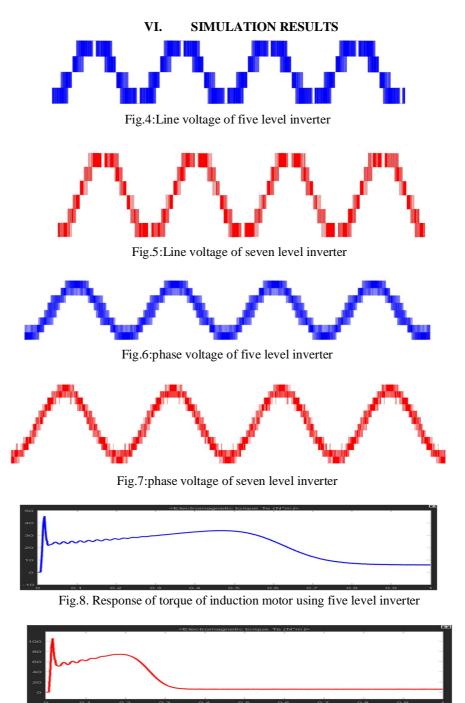

Fig.9: Response of torque of induction motor using seven level inverter

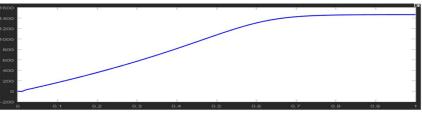

Fig.10: speed of motor using five level inverter

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 7 Issue IV, Apr 2019- Available at www.ijraset.com

Fig11: speed of motor using seven level inverter

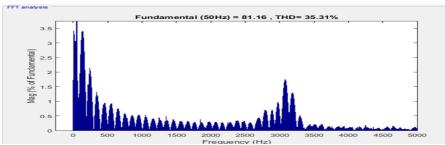

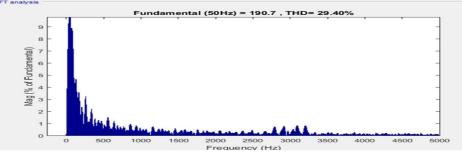

Fig 12: THD of line voltage using five-level inverter

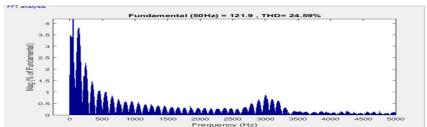

Fig13: THD of line voltage using seven-level inverter

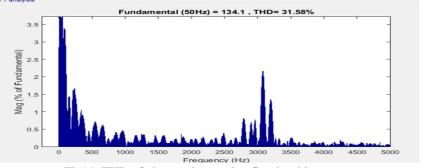

Fig14: THD of phase voltage using five-level inverter

Fig.15: THD of phase voltage using seven-level inverter

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887 Volume 7 Issue IV, Apr 2019- Available at www.ijraset.com

#### VII. CONCLUSION

In this paper, Sinusoidal PWM inverter fed induction motor has been analyzed and simulated using MATLAB/SIMULINK. This paper has provided a brief summary and comparison of Five-level and Seven-level multilevel inverter Cascaded H Bridge inverter circuit topologies. The THD using FFT analysis was compared in this paper. Simulation results of Five-level and Seven-level inverter fed three phase Induction motor topologies are discussed. Also this paper concludes that when the number of levels increasing, harmonics are reduced for same technique. This paper shows the steady state response of speed and electromagnetic torque of three phase induction motor using Sinusoidal PWM technique.

#### REFERENCES

- [1] Dr. P.S. Bimbhra, Power Electronics by Khanna Publishers, 3rd Edition, New Delhi, 2003.

- [2] Holmes, G.D. and Lipo, T.A. "Pulse Width Modulation for Power Converters Principles and Practice, IEEE Press Series on Power Eng., John Wiley and Sons, Piscataway, NJ, USA, 2003."

- [3] M.H. Rashid , Power Electronics Handbook by. Academic Press 2001

- [4] B. K. Bose, "Power Electronics and Variable Frequency Drives: Technology and Applications," IEEE Press, 1997

- [5] Rodriguez, Jose, Jih-Sheng Lai, and Fang Zheng Peng. 2002 Multilevel inverters: a survey of topologies, controls, and applications Industrial Electronics, IEEE Transactions 49.pp.724-738.

- [6] Ebrahim Babaei, Sara laali, Somayeh 2014 Cascaded Multilevel Inverter With Series Connection of Novel H-Bridge Basic Units IEEE Transactions on Industrial Electronics 61, Issue: 12, pp- 6664 - 6671,

- [7] Amarendra Edpuganti and Akshay K. Rathore 2015 Optimal Low Switching Frequency Pulse width Modulation of Nine-Level Cascade Inverter IEEE Transactions on Power Electronics 30, pp -482 – 495.

- [8] S Usha, C Subramani, A Geetha, 2018, "Performance Analysis of H-bridge and T-Bridge Multilevel Inverters for Harmonics Reduction" International Journal of Power Electronics and Drive Systems, 9 (1), pp:231-239.

- [9] J. Pereda and J. Dixon, "High-frequency link: A solution for using only one dc source in asymmetric cascaded multilevel inverters," IEEE Transactions on Industrial Electronics, vol. 58, no. 9, pp. 3884–3892, Sept 2011.

#### **AUTHOR'S BIOGRAPHY**

Mrs. K. Lavanya is currently working as an assistant Professor in the Department of Electrical and Electronics Engineering at ANITS, Sangivalasa, Bheemili mandal, Visakhapatnam, A.P. India. She received BE degree in Electrical and Electronics Engineering from TPIST, bobbili mandal, India, M.Tech in Power Electronics from JNTU Hyderabad, Aurora Engineering College, A.P., India and pursuing Ph.D in JNTUK, Kakinada. She has 13 years of teaching experience. Her research interests include Control System applications to Power Electronics and Machine Drives.

Gowtham Vasupalli was pursing Bachelor degree in E.E.E from ANITS Engineering College, Visakhapatnam, India. Jagadeesh Kumar Thoota was pursing Bachelor degree in E.E.E from ANITS Engineering College, Visakhapatnam, India. Shanmukha Prema Kumar was pursing Bachelor degree in E.E.E from ANITS Engineering College, Visakhapatnam, India.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)