IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 7 Issue: IV Month of publication: April 2019 DOI: https://doi.org/10.22214/ijraset.2019.4647

www.ijraset.com

Call: 🕥 08813907089 🔰 E-mail ID: ijraset@gmail.com

## **Optimal Design of Reconfigurable Arbiter Algorithm used in On-Chip S.O.C.**

D.Keerthi Vardhan<sup>1</sup>, Dr.S.Thulai Prasad<sup>2</sup>

<sup>1</sup>PG.Scholar, <sup>2</sup>Associate Professor Depatrment of ECE(VLSISD), Vidya Jyothi Institute of Technology, Hyderabad, India.

Abstract: This paper presents reconfigurable arbiter is placed in arbitration to the enhancement of the data transfer and reduce delay, latency and bandwidth b/w master core and slave cores. It provides high performance in real-time application on-chip S.O.C. The performance of arbitration in individual process was the earlier stages of the arbitration technique. In the processing of arbitration technique in a single step-by-step process the transfer of data from one multiple master to multiple core's causes delays. The simulations were done using XILINX 14.5.

Keywords: Arbiter, Technique, Cyclic, S.O.C., Reconfigurable, Xilinx Tool 14.5 version.

## I. INTRODUCTION

The reconfigurable arbiter is important and plays a major role in the performance and execution of multiple tasks at a partial interval of time. Arbiter is a component to which multiple master and multiple slaves are connected. Nowadays developing silicon chip industry has entered in multi-million gate chips. The 5th generation process is over-a-head of industries to design chips in multi-functionalities on one board. The multiple functionalities are nothing but the execution of applications in a single processors w/o any interruption in on system-on-chip (SOC). This generation has great handling of multiple tasks at a short interval of time. The multiple tasks mean having a number of i/p (inputs) slots to assign to o/p (outputs) slots in b/w single arbiter controls the whole process and work simultaneously on them. The topologies of previously shared buses are (1) static priority, (2)time division multiple access, (3)Round Robin, (4)lottery bus architectures. These topologies executing order is step-by-step manner. The data which request by the master is to travel along and reach its own path which is suitable to it. Till that annual time process of execution increases bandwidth, latency, delay, and area. The main reason for the proposal of reconfigurable arbitration is co-ordination of topologies in a single arbiter. These arbitration technique helps to increase rapidly data transfer by selecting a suitable topology by priority selection based method. By this method, the area, bandwidth, latency, and delay will be reduced. This runs automatically by arbitration technique. The Group of topologies present in arbiter has importance to each other. We describe it one by one.

| Selection<br>Method | Arbitration     |

|---------------------|-----------------|

| 00                  | Static Priority |

| 01                  | T.D.M.A         |

| 10                  | Round Robin     |

| 11                  | Lottery Bus     |

TABLE 1: Priority selection method.

The priority selection based method arbitration is a scheduling mechanism. Each arbitration is assigned to a priority value.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue IV, Apr 2019- Available at www.ijraset.com

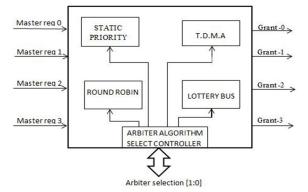

#### II. BLOCK DIAGRAM

Block diagram of a Reconfigurable Arbiter architecture representation is shown in Fig 1. Here a Block Diagram is the design that is an integrated circuit design functional block. The main important factor is priority selection method used for data transfer.

Fig 1: Reconfigurable arbiter architecture.

#### III. LITERATURE REVIEW

We have discussed some of the issues related to the design of S.O.C with regard to the inter process communication of Various bus architectures and protocols have been review[1]. Currently, on-chip communication networks are mostly implemented using shared interconnects like buses [2]. Hence in the future research, it is focused to design an arbiter that dynamically schedules the requests by various masters occurring simultaneously and thus improving the performance of a multiprocessor with respect to latency and bandwidth[3]. If some masters make little use of the bus it also provides a more fair distribution of bandwidth to the remaining masters[4]. The bandwidth regulator utilized to dynamically monitor the bus communication and thus can precisely control the bandwidth allocation[5]. A multi-processor system-on-chip includes embedded processors, digital logic and mixed-signal circuits combined into a heterogeneous multiprocessor[6]. This mix of technologies creates a major challenge for MPSOC design teams[7].

#### IV. RELATED WORK

Arbitration: it is a mechanism is to ensure one master request to access one slave at one time.

#### A. Static Fixed Priority Algorithm

The static fixed priority based arbitration is common to schedule.it will select the highest priority grant will be executed. If this process continues in this way its lead to starvation of lowest priority elements. The advantages of this technique are implantation easy and low area. Disadvantage if masters with high priority request frequently it will lead to starvation [1].

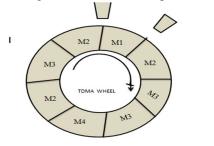

#### B. Time Division Multiple Access (T.D.M.A)

The Time division is an arbitration technique which has a cyclic (round) wheel in which every slot is placed in a particular bit in a wheel. It divides wheel into no of timing slots. The request made by the master to particular M1slot is reserved and to move next slots until all sequential slots are completed. If it does not wait for any slot request it moves to next slot in a wheel. TDMA lend its time with the lowest priority only during idle time. The advantage of this to implement a few execution requests in a particular time [2]. The disadvantage of this misleads of data transfer instead of reserved slots moves to other slots and low bandwidth. If request opts by the master it granting occurs after travelling all the time slots completed and returns to its previous position.

## International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177

Volume 7 Issue IV, Apr 2019- Available at www.ijraset.com

Fig.2: T.D.M.A Architecture.

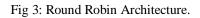

## C. Round Robin Algorithm

This type of algorithms works fast in data transfer. RR has a more efficient way of handling of random traffic in arbitration technique [3]. It can reallocate slots which were incomplete and keep forwarding request which is ready to take.it gradually decreases time and starvation among slots. The transfer length is short in RR and reduces delay, latency in a transfer of data. Among all the 3(three) algorithms R.R works more effectively. The fair arbitration has done in this algorithm. The request from the master core to slave core granting takes place with maximum access time and equal bandwidth achieved with limited transfer length. It doesn't wait for any slot whenever turn ends either unused or used moves to other components [4].

## ROUND ROBBIN

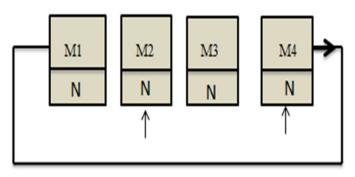

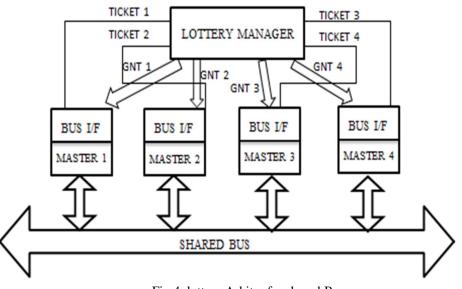

## D. Loterry Bus Algorithm

The algorithm depends upon lottery manager in which the number of the request is taken from masters such as r0,r1,r2,r3,r4 and they allot tickets to the requests such as t0,t1,0t2,t3,t4. The processing of ticketing which-ever it picks is granted from the slaves to master to transfer data [5]. which owned by lottery manager. It is a random number is generated which response to one of its ticket or almost near to ticket is having the highest priority to be granted likely. It is totally probability based distributions. It reduces delay (starvation) between master and slave [6]. The addition of request and tickets are done in random based generation method and granting is applied to it. The advantage of this algorithm FIFO (first-in-first-out) method which comes first serves to it [7].

Fig 4: lottery Arbiter for shared Bus.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue IV, Apr 2019- Available at www.ijraset.com

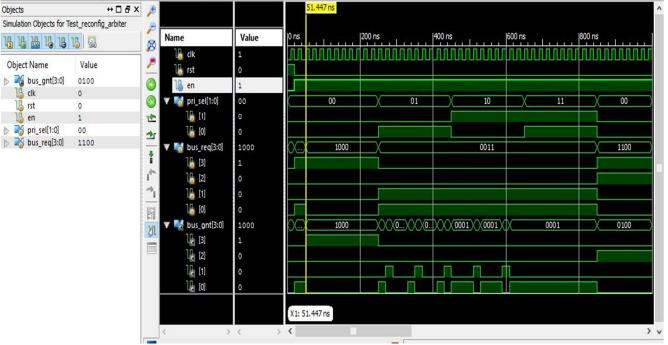

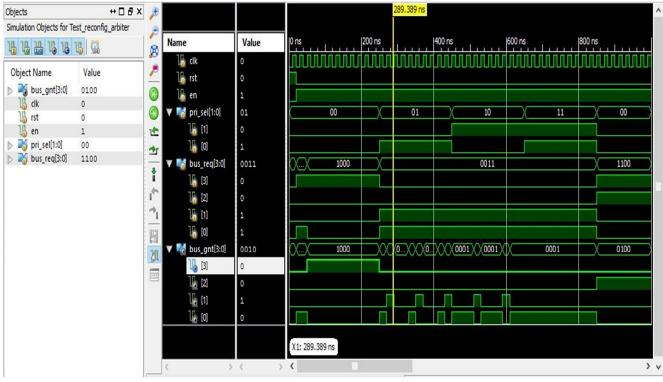

### V. SIMULATION AND RESULTS:

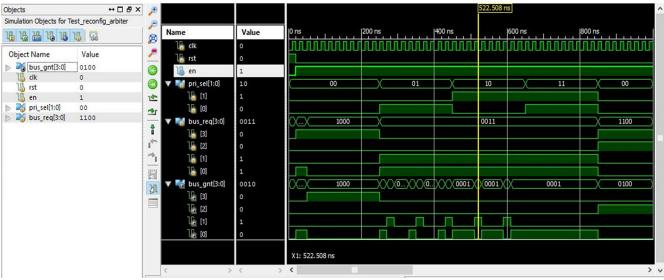

The Reconfigurable arbitration proposed in this work is implemented using Verilog on Xilinx ISE tool of version 14.5. The simulation wave form results of arbitration is shown in the below waveforms.

Fig.5: simulation waveforms for static priority.

Fig.6: simulation waveforms for T.D.M.A.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue IV, Apr 2019- Available at www.ijraset.com

Fig.7: simulation waveforms for a round robin.

| Objects                   | ↔□♂×                 | ج ا             |                  |       | 709.003 ns                           |

|---------------------------|----------------------|-----------------|------------------|-------|--------------------------------------|

| Simulation Objects for To | est_reconfig_arbiter |                 |                  |       |                                      |

| 14 14 14 16 18            | 16 63                | 8               | Name             | Value | 0 ns  200 ns  400 ns  600 ns  800 ns |

| Object Name               | Value                | 1               | 🔚 clk            | 0     |                                      |

|                           |                      | _               | 76 rst           | 0     |                                      |

| bus_gnt[3:0]              | 0100                 |                 | 16 en            | 1     |                                      |

| l clk<br>L rst            | 0                    | 6               | V 📷 pri_sel[1:0] | 11    | 00 χ 01 χ 10 χ 11 χ 00               |

| 16 en                     | 1                    | 14              | ٦ᡖ [1]           | 1     |                                      |

| pri_sel[1:0]              | 00                   | -tr             | 1 <u>6</u> [0]   | 1     |                                      |

| bus_req[3:0]              | 1100                 | -               | 🔻 📷 bus_req[3:0] | 0011  | (\\ 1000 \(\\) 0011 (\\) 1100        |

|                           |                      | ł               | 1.6 [3]          | 0     |                                      |

|                           |                      | 5               | 16 [2]           | 0     |                                      |

|                           |                      | 1               | 16 [1]           | 1     |                                      |

|                           |                      | E               | 1 <u>6</u> [0]   | 1     |                                      |

|                           |                      | · provide state | 🔻 駴 bus_gnt[3:0] | 0001  |                                      |

|                           |                      | žı              | 16 [3]           | 0     |                                      |

|                           |                      |                 | 16 [2]           | 0     |                                      |

|                           |                      |                 | Un [1]           | 0     |                                      |

|                           |                      |                 |                  |       |                                      |

|                           |                      |                 | lia (o)          | 1     |                                      |

|                           |                      |                 |                  |       | V4. 200.002                          |

|                           |                      |                 |                  |       | X1: 709.003 ns                       |

Fig 8: simulation waveforms for lottery bus.

| TABLE 2: Area and delay for | different techniques comparing | with the reconfigurable arbiter |

|-----------------------------|--------------------------------|---------------------------------|

| 243d                        |                                |                                 |

| PARAMETRES                       |                   |                    |            |                  |           |

|----------------------------------|-------------------|--------------------|------------|------------------|-----------|

|                                  | No of<br>slices   | No ofLUT'S         | No of IO'S | No of<br>IOB'S   | DELAY(ns) |

| Static priority                  | 2 OUT OF<br>8672  | 3 OUT OF<br>17344  | 8          | 8 OUT OF<br>190  | 6.376     |

| Time division<br>multiple access | 3 OUT OF<br>17344 | 6 OUT OF<br>17344  | 11         | 11 OUT<br>OF 250 | 6.458     |

| Round robin                      | 7 OUT OF<br>8672  | 15 OUT OF<br>17344 | 11         | 11 OUT<br>OF 250 | 3.590     |

| Lottery bus                      | 14 OUT OF<br>8672 | 27 OUT OF<br>17344 | 10         | 10 OUT<br>OF 250 | 9.138     |

| Reconfigurable<br>arbiter        | 27 OUT OF<br>8672 | 52 OUT OF<br>17344 | 13         | 13 OUT<br>OF 250 | 2.905     |

As we observed from the following table that reconfigurable arbiter has less delay and area.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue IV, Apr 2019- Available at www.ijraset.com

## VI. CONCLUSION

In this, we have come to know about reconfigurable arbiter and it uses. How effectively utilization of bus speed of data transfer. It's performances and it's working among critical traffic cyclic period. Handling of data to be transferred to it through priority selection method. And also compare the performance with various arbitration. I hope future work and research may depend upon various arbitrations that must reach requirements of the User and various techniques are obtained to be calculated.

### REFERENCES

- [1] Hardwick shah, Rabbe, Knoll, Priority division: A rapid shared-memory transport assertion with limited inactivity In 2011 EDAA.

- [2] Shanthi R.Amutha Performance Analysis of On-Chip Communication Architecture in MPSoC In Proceedings of IEEE, ICETECT 2011.

- [3] Dinesh Padole, P.R.Bajaj, et.all, "Dynamic Lottery Bus Arbiter for Shared Bus System on-chip: A Design Approach with VHDL"First universal gathering on Emerging Trends Engineering and Technology, 2008 IEEE.

- [4] "Progressed microcontroller transport design (amba)." [Online]. Accessible: http://www.arm.com.

- [5] "Center interface transport engineering." [Online]. Accessible: http://www.IBM.com//

- [6] Bu-Chung Lin Geeng-Wei Lee, Junin DarHuang and JingYang Jou, A Precise Bandwidth Control Arbitration Algorithm for Hard Real-Time SOC Busses", DAC 2007.

- [7] Prakash Srinivasan, Ali Ahmadinia Ahmet, T Erdogan Tughrul Arslan"Power Evaluation of the Arbitration arrangement for various On-Chip Bus base SoC stage", IEEE SOC Conference, Taiwan, Volume, Issue, 26-29 Sept. 2007.

- [8] Ahmed Amine Jerraya, Wayne Wolf, Multiprocessor Systems-on-Chips [M], Morgan Kaufmanns Publishers Inc. San Francisco, 2005.

- [9] R. Ho, K. W. Mai, and M.A. Horowitz, "The fate of wires," Proc IEEE, vol. 89, no. 4, pp. 490-504, April. 2001.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)