IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 7 Issue: V Month of publication: May 2019

DOI: https://doi.org/10.22214/ijraset.2019.5026

www.ijraset.com

Call: 🕥 08813907089 🔰 E-mail ID: ijraset@gmail.com

# **AMBA AHB Design: A Review**

Varnita Saini<sup>1</sup>, Geetanjali Pandove<sup>2</sup>

<sup>1, 2</sup>Department of Electronics and Communication Engineering, Deenbandhu Chhotu Ram University of Science and Technology, Murthal, Haryana, India

Abstract: In this paper, verification environment of AMBA AHB is presented by using system verilog. To replace complex bridges with the specific protocol block interface in SoC design AMBA protocol family is used. AMBA AHB is the communication bus protocol for a System on chip. AMBA AHB can be used in high clock frequency system modules. It acts as the high-performance system backbone bus. AMBA is basically single layer bus. The single layer AMBA AHB design has all the AMBA AHB signals or specifications. The paper also introduced various arbitration techniques of AMBA AHB. Keywords: AMBA, TDMA, SoC, AMBA AHB

#### I. INTRODUCTION

An SOC may be a system that is taken into account as a collection of elements and interconnects among them. A SOC may include different Intellectual Property like memory, I/O peripherals and processors with different functionalities. These may vary in their speed and interconnection of these IP's will be important and it is done using SOC bus. The advanced microcontroller bus architecture was introduced by ARM Ltd in 1996.

As the level of style quality has become higher, SoC design requires a system bus with high bandwidth to perform the multiple operations in parallel. AMBA was given by ARM which provides different kinds of buses to be used in microcontrollers, SOC's and ASIC's. Due to high bandwidth AMBA protocol is best suited protocol for today's system. AMBA protocol is an open standard so that it can be tailored to any system's requirements. It is widely used in network interconnect chip, RAM controller, DMA controller, level 2 cache controller etc.

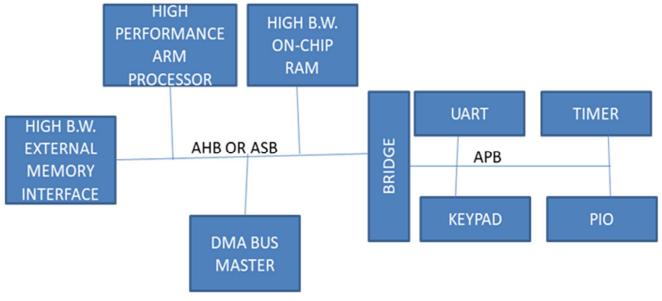

Fig 1. AMBA

#### A. AMBA AHB Features

- 1) High performance

- 2) Burst Transfer

- 3) Single edge clock operation

- 4) Address decoding

- 5) Large data bus width

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue V, May 2019- Available at www.ijraset.com

Fig 2.AMBA AHB Block Diagram

Ac

This paper is organized as follows. We discuss the comparison of various methodology of AMBA AHB. Next we explain the multichannel AHB. We also present the different arbitration techniques of AMBA AHB. Finally discuss the arbitration techniques in conclusion

| В.                 | Comparison | of Various | Methodology | of AMBA AHB |

|--------------------|------------|------------|-------------|-------------|

| $\boldsymbol{D}$ . | Comparison | of various | moundation  |             |

| Sr. | Authors             | Paper Title                  | Proposed Methodology       | Research Prospects                           |

|-----|---------------------|------------------------------|----------------------------|----------------------------------------------|

| No. |                     |                              |                            |                                              |

| 1   | Han Ke, Deng        | Verification of AMBA bus     | Designing of reference     | A references model is used to verify SRAM    |

|     | Zhongliang, Shu     | model using system verilog   | model to dynamically       | and Flash controller. This model reduces the |

|     | Qiong               |                              | predict the DUT            | time consumption.                            |

|     |                     |                              | behaviour.                 |                                              |

| 2   | Shraddha Divekar,   | Multichannel AMBA AHB        | Xilinx software is used to | It provide interconnection scheme between    |

|     | Archana Tiwari      | with multiple arbitration    | design AMBA AHB bus        | multiple masters and slave. Interconnection  |

|     |                     | techniques                   | arbitration techniques and | busmatrix gives increase in bus bandwidth    |

|     |                     |                              | implementing by VHDL       | and flexibility.                             |

|     |                     |                              | language using FPGA.       |                                              |

| 3   | Anurag Shrivastava, | Performance Comparison of    | Case study of different    | Compare different AMBA protocols with        |

|     | G.S. Tomar,         | AMBA Bus based SoC           | AMBA SoC bus               | their features and performance matrices.     |

|     | Ashutosh Kumar      | communication protocol       | protocol.                  |                                              |

|     | Singh               |                              |                            |                                              |

| 4   | Massimo Conti,      | Performance analysis of      | Describe AMBA AHB by       | It give the system C and VHDL clock          |

|     | Marco Caldari,      | different arbitration        | SystemC 2.0                | accurate model. This model is use to         |

|     | Giovanni B. Vece,   | algorithms of the AMBA       | SOFTWARE.                  | evaluate performance of the bus. It give     |

|     | Simone Orcioni      | AHB bus                      |                            | result in reduction in power dissipation.    |

|     |                     |                              |                            |                                              |

| 5   | Marco Bertola, Guy  | A methodology for the design | State machine is design    | It gives the different steps for master      |

|     | Bois                | of AHB bus master wrappers   | by Mentor Graphics HDL     | wrapper and these steps or methodology can   |

|     |                     |                              | Pro tool and simulation    | apply for other protocols                    |

|     |                     |                              | was done by Seamless       |                                              |

|     |                     |                              | CVE co-verification tool.  |                                              |

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue V, May 2019- Available at www.ijraset.com

| 6  | Rinku, Pawan Kumar                | Advance high performance      | Defining the AMBA          | Comparison of techniques gives that round          |

|----|-----------------------------------|-------------------------------|----------------------------|----------------------------------------------------|

|    | Dahiya                            | bus arbitration techniques: A | protocol with arbitration  | robin arbitration technique is much better         |

|    |                                   | state of the art review       | protocol.                  | than the fixed priority and weighted round         |

|    |                                   |                               |                            | robin techniques.                                  |

| 7  | Wang Zhonghai, YE                 | Designing AHB/PCI bridge      | RTL of AMBA bridge.        | This describe model of AHB/PCI bridge at           |

|    | Yizheng                           |                               |                            | RTL level which is synthesized by synopsis         |

|    |                                   |                               |                            | software                                           |

| 0  | Youngwoo Kim,                     | AMBA based multiprocessor     |                            | It proposed no multiprocessing capabilities        |

| 8  | Kyong Park,                       | system                        | Dual ARM processor         | bus architecture. The bus architecture using       |

|    | Myungjoon Kim                     |                               | cores with 0.18um.         | dual ARM processor core with standard cell         |

| 9  | Prakash Srinivasan.               | Power Analysis of arbitration | Using TDM and priority     | process.<br>It uses multi master under arbitration |

| 9  | Adeoye Olugbon, Ali               | techniques for AMBA AHB       | scheme of arbitration      | policies which gives the different features of     |

|    | Adeoye Olugboli, Ali<br>Ahmdinia, | based reconfigurable SoC      | power is analysed.         | each policy and strong correlation between         |

|    | Annunna,                          | based reconfigurable Soc      | power is analysed.         | power and effectiveness.                           |

| 10 | Prince Gurha, R.R.                | SV assertion based            | To bind the assertion      | According to assertion based verification of       |

| 10 | Khandelwal                        | verification of AMBA-AHB      | module uses BIND SV        | AMBA AHB any one master can transfer               |

|    |                                   |                               | feature.                   | the data at any one clock cycle.                   |

| 11 | Sreehari S, Jaison                | AHB DDR SDRAM                 | Use Icarus verilog tool to | To perform read and write operation                |

|    | Jacob                             | enhanced memory controller    | synthesized.               | necessary address and control signals are          |

|    |                                   |                               |                            | provided by memory controller. There is no         |

|    |                                   |                               |                            | loss of data. Using memory controller data         |

|    |                                   |                               |                            | and commands are transferred successfully.         |

| 12 | Abhik                             | Using formal techniques to    | To detect a potential bus  | It represents experience in verification of        |

|    | Roychoudhary,                     | debug the AMBA SoC bus        | starvation scenario SMV    | SoC bus protocol. These use verification           |

|    | Tulika Mitra, S.R.                | protocol                      | model checker is used.     | techniques which is useful in automatically        |

| 10 | Karri                             |                               |                            | detecting cases in protocol detection.             |

| 13 | Soo-Yun Hwang,                    | An improved implementation    | Removal of input stage     | Verification techniques in the protocol            |

|    | Kyoung-Sun Jhang                  | method of AHB bus matrix      | improved method of         | specification as model checking are useful         |

|    |                                   |                               | ML-AHB bus matrix is       | in automatically detecting suitable corner         |

|    |                                   |                               | presented.                 | cases                                              |

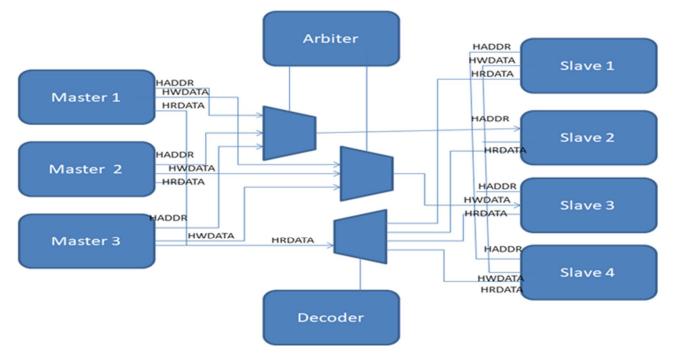

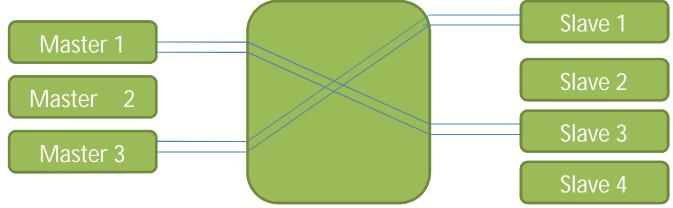

#### C. Multi-channel AHB

The multi-layer/multi-channel AHB bus matrix is an interdependence scheme which is based on AMBA AHB protocol in which multiple masters and slave has parallel access path for data transaction. The multi-layer AHB uses slave side arbitration. Slave facet arbitration is completely different from master facet arbitration. After master provides a signal to the slave it wait for the response of the slave regarding the status for processing the data. Thus, AHB bus matrix has transferred based arbitration strategy only. Because of the arbitration strategy limitless of AHB bus matrix it may lead to system performance degradation. Several studies for the high performance bus has been recommended such as look up table based on cross bar arbitration, token ring arbitration etc.

Fig 3. Block Diagram of Basic Multi-channel concepts

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.177 Volume 7 Issue V, May 2019- Available at www.ijraset.com

- D. Arbitration Techniques

- Round Robin Technique: In this mechanism the master who wants to send the data to slave first request to the arbiter for getting the access of the bus. The transfer of data with the highest priority changes in circulates fashion. If any masters do not want to access the bus then priority is transfer to the next priority master. So, in round robin technique access of the bus depend upon priority.

- 2) *Fixed Priority Technique:* In this technique all the master has fixed priority. If several masters are trying to access the same slave at same time then access of the bus is given to the highest priority master. It has low area cost, more flexibility and faster arbitration time.

- *3) Dynamic Arbitration:* This mechanism is also depend upon priority level but after getting the access of the bus the master priority is reduced by 1.

- *4) TDMA:* In this approach all the masters are given fixed time frames for transfer of data. If any master want more bandwidth can be given more time frame.

| Parameter       | Round Robin      | Fixed Priority | Dynamic      | TDMA                     |  |  |

|-----------------|------------------|----------------|--------------|--------------------------|--|--|

| Simplicity      | Moderate         | High           | Low          | Moderate                 |  |  |

| Cost            | Moderate         | Low            | High         | Moderate                 |  |  |

| Architecture    | All masters have | Shared Bus     | Require more | Require high and fixed   |  |  |

| equal bandwidth |                  |                | bandwidth    | bandwidth to all masters |  |  |

| Performance     | Moderate         | High           | Low          | High                     |  |  |

| Table 1 | .Comp | arison | of T | Techniq | ues |

|---------|-------|--------|------|---------|-----|

|---------|-------|--------|------|---------|-----|

#### II. CONCLUSION

This paper gives the discussion on design of AMBA AHB. The presented model is synthesized by QuestaSim and EDA tools software. For all transaction AMBA AHB uses rising clock edge. We analyze impact on power of the bus by different numbers of masters with different arbitration policies. Table 1 gives the comparison between arbitration policies.

#### REFERENCES

- [1] Roychoudhury, T. Mitra, S.R. Karri "Using formal techniques to Debug the AMBA System-on-Chip Bus Protocol", Design, Automation and Test in Europe Conference and Exhibition, pp 1530-1591,2003 H. Ke, D. Zhongliang, S.Qiong "Verification of AMBA Bus Model Using SystemVerilog", The IEEE Eighth International Conference on Electronic Measurement and Instruments, pp 776-780, Aug. 2007

- [2] A. Shrivastava, G.S. Tomar, A.K. Singh "Performance Comparison of AMBA Bus-Based System-On-Chip Communication Protocol", Proc. IEEE International Conference on Communication Systems and Network Technologies, pp 449-454, June 2011

- [3] H. Ke, D. Zhongliang, S.Qiong "Verification of AMBA Bus Model Using SystemVerilog", The IEEE Eighth International Conference on Electronic Measurement and Instruments, pp 776-780, Aug. 2007

- [4] J. Jalley, J. Abellay, E. Quinonesy, L. Fossati, M. Zulianello, F.J. Cazorla "AHRB: A High-Performance Time-Composable AMBA AHB Bus", IEEE 19th Real-Time and Embedded Technology and Applications Symposium, pp 225-235, April 2014

- [5] K.A.R. Rao, M Divya "AHB Design and Verification AMBA 2.0 using System Verilog", International Journal of Advance Research, Ideas and Innovations in Technology, vol. 4, Issue 3, pp 1389-1391, 2018.

- [6] M. Conti, M. Caldari, G.B Vece, S. Orcioni, C.Turchetti "Performance Analysis of Different Arbitration Algorithms of the AMBA AMB Bus", IEEE, pp 618-621, May 200

- [7] M. Bertola, G. Bois "A methodology for the design of AHB bus master wrappers", IEEE Euromicro Symposium on Digital System Design, Sep. 2003

- [8] P. Srinivasan, A, Olugbon, A. Ahmadinia, A.T. Erdogan, T. Arslan "Power Analysis of Arbitration Techniques for AMBA AHB based Reconfigurable System-on -Chip", IEEE, pp 227-230, Nov. 2006

- [9] P. Gurha, R. R. Khandelwal "System Verilog Assertion Based Verification of AMBA-AHB", IEEE International Conference on Micro-Electronics and Telecommunication Engineering, pp 641-645, June 2016

- [10] Rinku, P.K. Dahiya "Advance High Performance Bus Arbitration Techniques (AHB): A State-of-the-Art Review", IOSR Journal of VLSI and Signal Processing (IOSR-JVSP), Vol. 7, Issue 4,pp 51-56, Aug. 2017

- [11] S. Divekar, A. Tiwari "Multichannel AMBA AHB with Multiple Arbitration Technique", IEEE International Conference on Communication and Signal Processing, pp1854-1858, April 2014

- [12] S.Y.Hwang, K.Y.Jhang "An improved implementation method of AHB busmatrix", IEEE International SOC Conference.pp 211-214, Sep. 2005

- [13] Sreehari S, J. Jacob "AHB DDR SDRAM Enhanced Memory Controller", IEEE International Conference on Advanced Computing and Communication Systems, Dec. 2013

- [14] S.I. Narendrappa, S.Y. RadhaSwamy, L.He "Performance Verification of Multi-Master AHB Bus System", IEEE Proceedings of the World Congress on Engineering, Vol.1, July 2018

- [15] W. Zhonghai, Y. Yizheng, W. Jinxiang, W. Mingyan "Designing AHB/PCI bridge", IEEE International Conference on ASIC Proceedings, pp 578-580, Oct. 2001

- [16] Y. Kim, K. Park, and M. Kim "AMBA Based Multiprocessor System", IEEE International Symposium on System-on-Chip, pp 41-42, Nov. 2003

- [17] Y. Godhal, K.Chatterjee, T.A. Henzinger "Synthesis of AMBA AHB from formal specification: a case study", International Journal on Software Tools For Technology Transfer, Vol.15, Issue 5-6, pp 585-60, October 2013

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)