# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 3 Issue: VI Month of publication: June 2015

DOI:

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

## Design and Implementation of ASIC Based Dual Data Rate SDRAM Memory Controller

V.Suresh<sup>1</sup>, Y.Murali<sup>2</sup>, M.Tech

2 <sup>nd</sup> Year M.TechVLSI, Assistant Professor

Department of ECE, Audisankara College of Engineering & Technology, gudur, (Autonomous)

Abstract- A Dedicated Memory Controller is of prime importance in applications that do not contain microprocessors (high-end applications). The Memory Controller provides command signals for memory refresh, read and write operation and initialization of SDRAM. Our work will focus on ASIC Design methodology of Double Data Rate (DDR) SDRAM Controller that is located between the DDR SDRAM and Bus Master. The Controller simplifies the SDRAM command interface to standard system read/write interface and also optimizes the access time of read/write cycle. Double Data Rate (DDR) SDRAM Controller is implemented using Xilinx 14.3.

Keywords: DDR SDRAM Controller, Read/Write Data path.

#### I. INTRODUCTION

We found memory devices in almost all systems and now a days high speed and high performance memories are having great demand. For better throughput and speed, the controllers are to be designed with clock frequency in the range of megahertz. As the clock speed of the controller is increasing, the design challenges are also becoming complex. Therefore the next generation memory devices require very high speed controllers like double data rate and quad data rate memory controllers. In this paper, the double data rate SDRAM Controller is implemented using ASIC methodology.

Synchronous Dynamic RAM (SDRAM) is preferred in embedded system memory design because of its speed and pipelining capability. In high-end applications, like microprocessors there will be specific built in peripherals to provide the interface to the SDRAM. But for other applications, the system designer must design a specific memory controller to provide command signals for memory refresh, read and write operation and initialization of SDRAM.

In this paper, the SDRAM controller, located in between the SDRAM and the Bus master, minimizes the effort to deal with the SDRAM memory by providing a simple system to interact with the bus master.

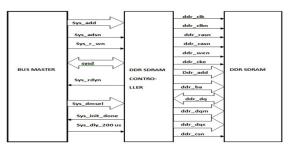

Figure 1 is the block diagram of the DDR SDRAM Memory Controller that is connected between the bus master and SDRAM . SDRAM's are classified based on their data transfer rates.

- A. Single Data Rate SDRAM's

- B. Double Data Rate SDRAM's

In Single data rate SDRAM, the data is transferred on every rising edge of the clock whereas in double data rate (DDR) SDRAM's the data is transferred on every rising edge and every falling edge of the clock and as a result the throughput is increased. DDR SDRAM Controllers are faster and efficient than its counterparts. They allow data transfer at a faster rate without much increase in clock frequency and bus width.

Fig. 1. DDR SDRAM controller system

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

#### II. IMPLEMENTATION METHODOLODY

The DDR SDRAM Controller architecture is implemented using Verilog HDL. The methodology followed is ASIC design flow. The basic steps that an ASIC design must go through are Design entry and Analysis, Technology Optimization and Floor planning, Design Verification, Layout . The RTL Synthesis and Simulations are performed using Xilinx 14.3.

#### III. DDR SDRAM CONTROLLER ARCHITECTURE

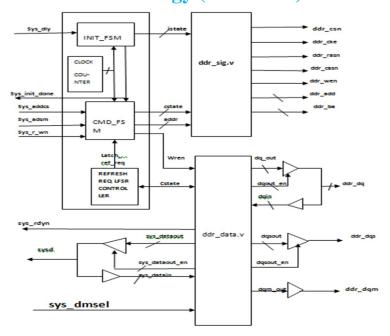

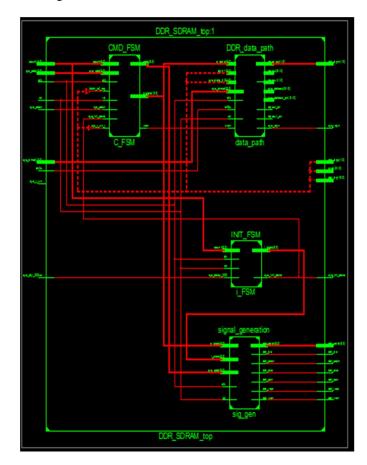

DDR SDRAM Controller module receives the addresses and control signals from the BUS Master. The Controller generates command signals and based on these signals the data is either read or written to a particular memory location. The DDR SDRAM Controller architecture is shown in Figure 2. It consists of three modules:

- A. Main Control Module

- B. Signal Generation Module

- C. Data Path Module.

The main control module has two state machines and a refresh counter. The two state machines are for initialization of the SDRAM and for generating the commands to the SDRAM. They generate iState and cState outputs according to the system interface control signals. The signal generation module now generates the address and command signals depending upon the iState and cState. The data path module performs the read and write operations between the bus master and DDR.

Following are some of the important features of DDR SDRAM Controller:

- 1) The DDR SDRAM Read and Write operations are simplified by the controller.

- 2) For initializing the DDR SDRAM controller, separate state machines are designed internally.

- 3) The access time for read and the write cycle is minimised based on the CAS latency and burst length of the DDR SDRAM.

- 4) The auto refresh for the DDR SDRAM is done by the controller.

The main control module consists of three sub modules: 1.Initialization FSM module (INIT\_FSM).

Command FSM module (CMD FSM)

Counter module.

#### A. Main Control Module

The DDR SDRAM Controller has to undergo an initialization process by a sequence of command signals before the normal memory access. The initialization finite state machine in the main control module is responsible for the initialization of the DDR SDRAM controller. Figure 3 shows the state diagram of

the initialization FSM (INIT\_FSM).

Whenever reset signal is high, the initialization FSM will switch to i\_IDLE state. Once the reset signal goes low, the controller has to wait for 200us clock stabilization delay. This is constantly checked by sys\_dly\_200us signal and a high on the sys\_dly\_200us will indicate that the clock stabilization delay is complete. The DDR initialization sequence will begin immediately after the clock/power stabilization is complete and then the INIT\_FSM will change its state from i\_IDLE to i\_NOP state. From the i\_NOP state, the initialization FSM will switch to the i\_PRE state on the next clock cycle. In the i\_PRE state, the main control module will generate the PRECHARGE command. The PRECHARGE command generated during this state will be applied to all the banks in the device. Once the PRECHARGE command is generated by the initialization FSM, it will switch to the next state. The next state in the design of initialization FSM is two AUTO REFRESH commands. These refresh commands are generated to refresh the DRAM memory. After the two refresh state, the initialization FSM will switch to i\_MRS state. During this state LOAD MODE REGISTER command is generated to configure the DDR SDRAM to a specific mode of operation.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig.2. Functional block diagram of DDR SDRAM controller.

After satisfying the i\_tMRD timing delay the initialization FSM will switch to i\_ready state. The initialization FSM will remain in the i\_ready state for normal memory access. And also, when the initialization FSM switches to i\_ready state signal sys\_INIT\_DONE is set to high to indicate that DDR SDRAM controller initialization is completed. The *i\_PRE*, *i\_AR1*, *i\_AR2*, *i\_EMRS* and *i\_MRS* states are used for issuing DDR commands.

CMD\_FSM handles the read, write and refresh of the SDRAM. The CMD\_FSM state machine is initialized to *c\_IDLE* during reset. After reset, CMD\_FSM stays in *c\_IDLE* as long as *sys\_INIT\_DONE* is low which indicates the SDRAM initialization sequence is not yet completed. When the sys\_INIT\_DONE is high, it indicates the system initialization is complete. The controller will now wait for *latch\_ref\_req*, *sys\_INIT\_DONE* signals and will enter auto refresh, read and write mode depending upon these signals.

When the initialization is complete and when the *latch\_ref\_req* goes high the controller will refresh by entering into refresh state. After the refresh is complete, when the *latch\_ref\_req* and *sys\_ADSn* signal goes low, the controller will go to active state. The ACTIVE command will be issued for each read or write access to open the row.

Fig.3. DDR SDRAM Initialization FSM (INIT FSM) state diagram.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

After a specified delay is satisfied, READ or WRITE commands will be issued. Read or write is determined by the  $sys_R_Wn$  signal. If logic high is sampled, the state machine switches to  $c_READA$ . If a logic low is sampled, the state machine switches to  $c_READA$  to  $c_READA$

After the data is transferred, it switches back to c\_IDLE. For write cycles, the state machine switches from c\_WRITEA to c\_wdata for transferring data from bus master to SDRAM, and then switches to c\_tDAL. After writing the data, it switches back to c\_IDLE state.

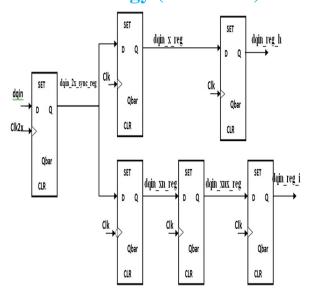

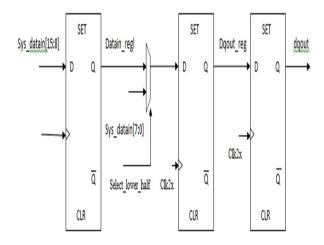

#### B. Data Path Module

The DDR SDRAM Controller design interfaces between the 8-bit data bus, and the bus master with a 16-bit data bus. The data path module for read and write are shown in figure. The data path module depends on cState for its read/write operation. The cState is generated by the CMD\_FSM present in the Main Control module.

Fig.4. DDR SDRAM command FSM (CMD\_FSM).

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig.5. Read data path for DDR SDRAM Controller.

Fig.6. Write data path for DDR SDRAM Controller

#### C. Signal Generation Module

The DDR SDRAM Signal generation module should generate the command signals to the DDR SDRAM. The command signals include ddr\_add; for generating addresses, ddr\_casn and ddr\_rasn; for selecting particular column and row address. These signals are generated based on the iState and cState received from the CMD\_FSM and INIT\_FSM present in the Main Control module.

#### IV. EXPERIMENTAL RESULTS

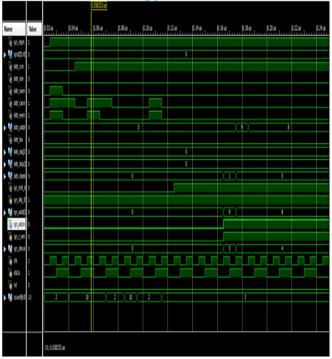

The Design is simulated using Xilinx 14.3. The Controller is designed using Verilog HDL. Figures below shows the simulation results,RTL schematic and Technology schematics of DDR SDRAM Controller.

www.ijraset.com IC Value: 13.98

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig.7. Simulation results of DDR SDRAM controller

Fig.8. RTL Schematic of DDR SDRAM

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig.9. Technology Schematic of DDR SDRAM

#### V. CONCLUSION

ASIC Design methodology is opted for Double Data Rate (DDR) SDRAM Controller. The DDR SDRAM Controller architecture is implemented in Verilog HDL. The RTL Simulation and Synthesis results are obtained using Xilinx tool.

#### REFERENCES

- [1] DDR SDRAM Controller white paper, Lattice Semiconductor Corporation, Reference Design: RD1020, April 2004.

- [2] SDR SDRAM Controller white paper, Lattice Semiconductor Corporation, Reference Design: RD1010, April 2011.

- [3] Chen Shuang-yan, Wang Dong-hui, Shan Rui Hou Chao, "An Innovative design of DDR/DDR2 SDRAM Compatible Controller", ASICON International Conference, pp 62-66 24th Oct 2005.

- [4] Micron Technology, Micron's Synchronous DRAM (2002).

- [5] Michael John Sebastian Smith, "Application Specific Integrated Circuits", 2004.

#### **AUTHORS**

<sup>1</sup>V.Suresh received his B.TECH degree in Electronics and Communication Engineering from Sree Rama Engineering College, tirupati, Chithoor (Dist), affiliated to JNTU Anantapur. He is currently pursuing M.Tech VLSI in Audisankara college of Engineering and Technology, Gudur(Autonomous), Nellore (Dist), affiliated to JNTU Anantapur.

<sup>2</sup> Y.Murali received his M.Tech in VLSI from Vathsalya Institute of Science and Technology,Bhongir,Nalgonda(Dist). He has 6 years and 4 months teaching experience. He is presently working as Assistant Professor in the department of ECE Audisankara College of Engineering and Technology,Gudur (Autonomous), Affiliated to JNTU, Anantpur

10.22214/IJRASET

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)