# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 4 Issue: I Month of publication: January 2016

DOI:

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

www.ijraset.com Volume 4 Issue I, January 2016 IC Value: 13.98 ISSN: 2321-9653

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

### A Review of Efficient Low Power High Speed Flash ADC Design Techniques

Miss Pallavi Sawant<sup>1</sup>, Mrs. Prof. H. H. Kulkarni<sup>2</sup>

<sup>1</sup>ME Student, <sup>2</sup>Assistant Professor, Department of E&TC

G. E. S. R. H. Sapat College of Engineering, Nashik, Maharashtra, India

Abstract— Analog to digital converter is the important component in signal processing and communication system. It is a mixed system which converts the analog signals into the digital signals for transformation of sensor data. There are many types of ADC's available such as pipeline ADC, successive approximation ADC, delta sigma ADC etc. In present day CMOS technology the flash ADC is composed by utilising the dynamic method, it reduces the power, and delay. A flash ADC is extremely valuable for fastest speed operations when it is compared with the other ADC architectures. Comparator and Encoder are vital part of flash ADC. This paper presents review of Efficient Low Power High Speed Flash ADC Techniques. Keywords—ADC, Flash ADC, Resolution, Conversion rate, Comparator, Conversion speed, Encoder.

#### I. INTRODUCTION

The signals in the real world are analog in nature for example light, sound, video etc. In order to achieve digital signal, analog signal has to be converted into digital form by using a circuit called analog to digital converter. Whenever analog signal is needed back, digital to analog converter is required. Analog to digital converters are important block in many modern systems that require the integration of analog signals with digital systems.

#### II. FLASH ADC

The flash ADC is known for its fastest speed of operation compared to other ADC architectures. So it is used for high speed and very large bandwidth applications such as radar processing, optical communication links, digital oscilloscopes, high-density disk drives and so on. The flash ADC is also called as the parallel ADC because of its parallel architecture.

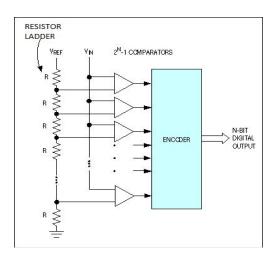

Fig. 1 Flash ADC.

Figure 1 shows Flash ADC architecture. It can be seen from the figure, that  $2^N$  - 1 comparators are required for "N" bit flash converter. The resistor ladder network is formed by  $2^N$  resistors, which is used to generates the +reference voltages for each of the comparators. Reference voltage for each and every comparator is 1 least significant bit which is less than the reference voltage for the comparator instantly above it. When the input voltage is above the reference voltage of comparator it will generate a "1" otherwise, the comparator output is "0". The comparators will generate a thermometer code of an input signal. This code is known as thermometer code because it is similar as mercury thermometer, where in the mercury column, the mercury rises to the suitable temperature and no mercury is above that temperature. This thermometer code will be then encoded into a binary form by thermometer to binary encoder [11].

Volume 4 Issue I, January 2016

www.ijraset.com IC Value: 13.98 ISSN: 2321-9653

### International Journal for Research in Applied Science & Engineering **Technology (IJRASET)**

### III. LITERATURE REVIEW

This paper gives survey on various techniques of Flash ADC design. Researchers have implemented flash ADC with different number of bits and different CMOS technologies.

Steven B. Kaplan et.al [1] proposed a complete transient digitizer system consisting of a superconductive flash ADC, on chip acquisition hardware, a room temperature interface and HYPRESS to digitally reconstruct the input signal. Transient digitizer with a near term performance of at least 6 effective bits at 10 GHz and 8 effective bits at 2.5GHz are obtained. The wide bandwidth of the digitizer front end has been demonstrated in beat-frequency tests up to 30 GHz.

Yun-Ti Wang et.al. [2] proposed an 8-Bit 150-MHz CMOS ADC with 0.6µm CMOS technology with 8 bits Resolution. An 8bit 150-MHz CMOS ADC has been described that incorporates sliding interpolation, distributed sampling, interleaving, clock edge reassignment, and punctured interpolation.

Siamak Mortezapour et.al. [3] proposed a 1-V, 8-Bit Successive Approximation ADC. The ADC consumes less than 0.34mW and has an ENOB of 7.9 for a 1-kHz input with close to rail-to-rail signal swing. This design demonstrates that low-voltage ADC with medium accuracy can be realized without requiring special enhancements to CMOS technology.

Conor Donovan et.al. [4] proposed a 6-bit prototype converter built in a standard 0.25µm digital CMOS process which dissipates 150mW from a 2.2-V supply at 400 MS/s. It occupies 1.2 mm<sup>2</sup> and describe a digital technique that can removes the accuracy constraints from the comparators.

Christoph Sandner et.al. [5] proposed a 6 bit flash ADC, large analog bandwidth and low power in 0.13 µm CMOS copper technology with 1.2GSps. This ADC attains to an effective resolution bandwidth (ERBW) of 700 MHz when working at 1.2 GSps requires 160mW power and at 600 MSps accomplishes an ERBW of 600MHz with just 90mW power consumption from 1.5V supply. The chip area is 0.12mm<sup>2</sup> and requirement for reference resistor step, implicit sample and hold operation, no edge impacts in the interpolation network when contrasted with resistive addition and input capacitance is low of just 400fF and because of that safely drivable analog converter can be interface. This configuration demonstrates the efficiency of the capacitive interpolation construction modelling with distributed sample and hold for flash ADC in GHz range.

Sunghyun Park et.al. [6] proposed 4-GS/s 4-bit Flash ADC in 0.18-um CMOS. It achieves a measured DNL and INL of less than one quarter LSB at 4 GS/s. The measured ENOB is 3.89 bits at 4 GS/s with a 10 MHz input, and 3.47 bits at 3.4 GS/s with an 800 MHz input.

Mingzhen Wang et.al. [7] proposed a 4 bit flash ADC with high spurious free dynamic for high data transmission correspondences using 130nm CMOS technology. They proposed timed digital comparator with dynamic offset concealment to enhance the ADC dynamic performance. This flash ADC has two and half clock cycle latency. It has low input capacitance of 300fF. The power consumption is 1.35mW with 1.2V supply. It has 2.5GHz conversion rate using a multi-stage pipelined design. This flash ADC enhances high sampling rate, low power, low input capacitance and there is no need of any reference resistor stage.

M. Maruyama et.al [8] proposed a design of a superconductive flash ADC with a complementary configuration. A 4 bit A/D converter function in gray code are confirmed at low frequencies for both the QOS circuits with the ordinary comparators and with the dc-SQUID-type comparator.

Prof. S.S. Khot et.al. [9] introduced the design of 4-bit ADC. Threshold Inverter Quantization (TIQ) comparator is used with the input frequency of 1GHz and is designed using standard CMOS technology. The power consumption of ADC is less than 145μW. The DNL is observed as less than 0.5 LSB and INL is less than 0.7 LSB. The ADC design is simulated in Microwind 3.1.

H. Suzuki et.al. [10] proposed a 5-bit flash-type SFQ ADC's, which had used CQOS comparators integrated with error correction and bit-interleaving circuits.

Bui Van Hieu et.al. [11] proposed new approach which coordinates a bubble error identification circuits and it can declined all types of bubble error when contrasted with the past methodologies and the main advantage is that it consumes low power. This method has great structure, very high speed and little chip area when contrasted with different structure. With the help of this ROM based technique it can reduce the latency and power dissipation and can rectify both first and second order bubble error. This system just distinguishes all bubble errors as opposed to attempting to rectify bubble error, which still can't cover all errors. At whatever point bubble error happen, there is at least one violent move from 0 to 1 in the thermometer input code. By identifying the violent move bubble error can be uncovered. One two input AND gate distinguishes violent move of every input and afterward all outputs of AND gates are gathered to recognizes bubble errors.

Pradeep Kumar et.al. [12] introduced 3 bit flash ADC using 0.18 um technology with 1.3V power supply. This paper was proposed and clarified how the flash ADC is quick contrasted with other ADC. So it required as a part of uses where the latency is paramount and the hardware multifaceted nature is unassuming. The one limitation of the ADC converter is the exactness on

Volume 4 Issue I, January 2016 ISSN: 2321-9653

www.ijraset.com Volume 4

IC Value: 13.98 ISSN: 232

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

account of easiness of the circuits. For high resolutions the flash ADC's are very costly as a result of complexity is exponentially increments with the quantity of bit increments. The normal power consumption was 36.273mW.

Panchal S. D et.al. [13] proposed a 4-bit flash ADC in 180nm technology with 2.5V power Supply. In this paper pipelined flash Analog to Digital Converter (ADC) is designed to achieve high speed using 0.18um CMOS technology. ADC is designed using folding technique in cadence tool.

Arunkumar P. Chavan, et.al [14] proposed design and pre-simulation of a 3 bit and a 4 bit ADC for low power CMOS. The design operates with an input frequency of 25MHz with 1.5V supply. A conversion time for 3-bit is 2.162ns and 4-bit is 6.182 ns is obtained. The design and Pre-simulation are carried out in cadence tool under 90nm technology.

Mamta Gurjar et.al. [15] proposed implementation of TIQ based comparator that exhibits low power consumption compared to other types of comparator based design. A Speed of 15.3 Gs/s is observed for 3 bit ADC that has been simulated by cadence tool at 45 nm technology. TIQ based ADC provides the lower bandwidth of 16.65MHz and low SFDR 1.57dB.

H. Suzuki et.al. [16] proposed a 5-bit A/D converter by means including increasing the current density of the junction, reducing the size of the CQOS comparator and adopting the structure of locally isolated ground (LIG).

Amol Inamdar et al. [17] proposed different flavours of Flash comparators. One flavour uses differential quasi one junction SQUID quantizer with low inductance clocking scheme. The second flavour uses a differential SQUID wheel quantizer, and the third flavour uses a symmetric differential SQUID wheel quantizer with time interleaved clocks. Three flavors of the Flash comparator are designed to reduce its phase dependent nonlinearities by reducing the  $\beta L$  of the comparator. The powerful sampling scope reconstruction technique are also developed that enables to quantify the comparator SNR, duty cycle distortion, and sensitivity to duty DC bias using a single bit comparator..

Dheepak Mohanraj [19] proposed design of a High speed ADC system. The system described 8-bit ADC designed in a  $0.25\mu m$  CMOS technology and simulated in Win Spice. ADC can sample at 1.7875 MHz and the total sampling speed of ADC is becomes 14.3 Ms/s.

Gulrej Ahmed et.al. [20] proposed a 6 bit flash analog to digital converter using variable switching voltage CMOS Comparator with 65nm standard CMOS technology. The measured maximum differential and integral non-linearity (DNL and INL) for a ramp input are found to be 0.3 LSB 0.6 LSB respectively. This designed exhibits significant improvement in terms of power and speed.

Parthasarthy K.P.et.al. [21] introduced the usage of the low power consumption flash ADC for very high end receivers. The demanding issue in this paper was to design a low power latched comparator using 90nm technology with 0.8V DC supply. This technique consumes low power of 7.67mW, which consumes a low power of around half for a sampling frequency up to 1.2GHz. This configuration can be extended to high speed applications because comparator utilized as a part of this plan can work up to 5GS/s.

Xiaochen Yang et.al. [22] proposed a flash ADC architecture to achieve a better power Efficiency. Partially active flash ADC is designed with improved power efficiency in the 10 GS/s speed range. 6 bit four-way time-interleaved ADC prototype in 65 nm CMOS demonstrated. This ADC architecture offers better power efficiency than other ADC architectures in the 10 GS/s speed range.

S. S. KHOT [23] proposed a 6-BIT CMOS flash ADC. In this paper, a comparison of 6-bit flash ADC exercising TIQ comparator is manifested at 2.5 V and 3.3 V. A CMOS Flash ADC was schemed with 0.250 µm CMOS technology. Cascaded CMOS inverters is used as a comparator, fat tree encoder has been used to designed ADC.

TABLE I LITERATURE REVIEW

| Author                    | Architecture | Resolution | Input voltage | Technology | Improved Parameters        |

|---------------------------|--------------|------------|---------------|------------|----------------------------|

| Mamta Gurjar et.al [15]   | 3 bit flash  | 3 bit      | 0 V to 0.7 V  | 45 nm      | Speed-5.3 Gs/s             |

|                           | ADC          |            |               | COMS       | Bandwidth-16.65 MHz        |

| Mingzhen Wang et.al [7]   | 4 bit flash  | 4 bit      | 1.2 V         | 130 nm     | Power consumption- 1.35 m  |

|                           | ADC          |            |               | CMOS       | Conversion rate- 2.5GHz    |

| Pradeep Kumar et.al [12]  | 3 bit flash  | 3 bit      | 1.3 V         | 0.18um     | Power consumption-         |

|                           | ADC          |            |               | CMOS       | 36.273mw                   |

| Parthasarathy K. P. et.al | 6 bit flash  | 6 bit      | 0.8 V         | 90nm       | Power dissipation- 7.67mW. |

| [21]                      | ADC          |            |               | CMOS       |                            |

| Gulrej Ahmed et.al [20]   | 6 bit flash  | 6 bit      | 1.2 V         | 65nm       | Speed-1 GHz                |

|                           | ADC          |            |               | CMOS       |                            |

www.ijraset.com Volume 4 Issue I, January 2016 IC Value: 13.98 ISSN: 2321-9653

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

| Conor Donovan et.al [4]   | 6 bit flash<br>ADC | 6 bit | 2.2 V           | 0.25um<br>CMOS  | Power dissipation- 150 mW                                     |

|---------------------------|--------------------|-------|-----------------|-----------------|---------------------------------------------------------------|

| Prof. S.S. Khot et.al [9] | 4 bit flash<br>ADC | 4 bit | 0.7V            | 45nm<br>CMOS    | Power consumption- 145µW                                      |

| Panchal S. D. et.al [13]  | 4 bit flash<br>ADC | 4 bit | 2.5 V           | 0.18um<br>CMOS  | Gain- 72.5 dB at 150Hz 14.1 dB at 100MHz Bandwidth-2.511E6 Hz |

| S. S. Khot [23]           | 6 bit flash<br>ADC | 6 bit | 2.5 V and 3.3 V | 0.25 μm<br>CMOS | Speed- 500- 565msps                                           |

| Sunghyun Park et.al [6]   | 4 bit flash<br>ADC | 4 bit | 1.8 V           | 0.18 µm<br>CMOS | Power consumption- 78 mW                                      |

#### IV. CONCLUSIONS

In this paper different methods of designing flash ADC are examined. Comparator and encoder is vital part of designing Flash ADC. Different methods of designing Flash converter by various authors are compared for performance parameters like power consumption, conversion speed, gain, bandwidth, accuracy, and different technologies employed for obtaining better results.

#### V. ACKNOWLEDGMENT

The authors are thankful to Prof. S. P. Agnihotri-HOD, Dr. P. C. Kulkarni-Principal, Mr. P. M. Deshpande-Project Director, Sir M. S. Gosavi-Director, G. E. S. R. H. Sapat College of Engineering, Nashik, Maharashtra, India.

#### REFERENCES

- [1] Steven B. Kaplan, Paul D. Bradley, Darren K. Brock, Dmitri Gaidarenko, Deep Gupta, Wen- Quan Li and Sergey V. Rylov, "A Superconductive Flash Digitizer with on-chip Memory", IEEE Transactions on Applied Supercondutivity, Vol.9, No. 2, June 1999.

- [2] Yun-Ti Wang and Behzad Razavi, Member, IEEE, "An 8-Bit 150-MHz CMOS A/D Converter", IEEE Journal of solid-state circuits, Vol. 35, No. 3, Mar 2000.

- [3] Siamak Mortezapour and Edward K. F. Lee, "A 1-V, 8-Bit Successive Approximation ADC in Standard CMOS Process", IEEE Journal of solid-state circuits, Vol. 35, No. 4, April 2000.

- [4] Conor Donovan and Michael P. Flynn, Senior Member, IEEE, "A Digital 6-bit ADC in 0.25-um CMOS", IEEE Journal of solid-state circuits, Vol. 37, No. 3, Mar 2002.

- [5] Christoph Sandner, Member, IEEE, Martin Clara, Andreas Santner, Thomas Hartig, and Franz Kuttner, "A 6-bit 1.2-GS/s Low-Power Flash-ADC in 0.13-um Digital CMOS", IEEE Journal of solid-state circuits, Vol. 40, No. 7, July 2005.

- [6] Sunghyun Park, Member, IEEE, Yorgos Palaskas, Member, IEEE, and Michael P. Flynn, Senior Member, IEEE, "A 4-GS/s 4-bit Flash ADC in 0.18-um CMOS", IEEE Journal of solid-state circuits, Vol. 42, No. 9, Sept 2007.

- [7] Mingzhen Wang and Chien-In Henry Chen, "A High Spurious-Free Dynamic Range 4-bit ADC with Nyquist Signal Bandwidth for Wideband Communications, Instrumentation and Measurement Technology Conference (IMTC), Warsaw, Poland, May 1-3, 2007.

- [8] M. Maruyama, H. Suzuki, Y. Hashimoto, and M. Hidaka, "A flash ADC using Complementarily Combined SQUIDs", IEEE Transactions on Appl. Supercondutivity, vol. 19, pp. 680684, Jun. 2009.

- [9] Prof. S.S. Khot, Dr. P. W. Wani, Dr M S Sutaone, Shubhang Tripathi, "Design of a 45nm TIQ Comparator for High Speed and Low Power 4-Bit Flash ADC", Proc. of Int. Conf. on Advances in Electrical & Electronics 2010.

- [10] H. Suzuki, M. Oikawa, K. Nishii, K. Ishihara, K. Fujiwara, M. Maruyama, and M. Hidaka, "Design and Demonstration of a 5-Bit Flash-Type SFQ A/D Converter Integrated With Error Correction and Interleaving Circuits", IEEE Transactions on applied superconductivity, Vol.21, No. 3, June 2011.

- [11] Bui Van Hieu, Seunghwan Choi, Jongkug Seon, Youngcheol Oh, Chongdae Park, Jaehyoun Park, Hyunwook Kim, and Taikyeong Jeongt, "A New Approach to Thermometer-to-Binary Encoder of Flash ADCs Bubble Error Detection Circuit", IEEE MWSCAS, Aug 7-10, 2011.

- [12] Pradeep Kumar and Amit Kolhe, "Design and Implemented of low power 3 bit flash ADC in 0.18 um CMOS", International Journal of Soft Computing and Engineering (IJSCE), ISSN: 2231-2307, Volume-1, Issue-5, November 2011.

- [13] Panchal S. D., Dr. S. S. Gajre, Prof. V P Ghanwat, "Design and implementation of 4-bit flash ADC using folding technique in cadence tool", International Journal of Advanced Research in Computer and Communication Engineering Vol. 1, Issue 4, June 2012.

- [14] Arunkumar P Chavan Rekha G, P Narashimaraja, "An Efficient Design of 3bit and 4bit Flash ADC", International Journal of Computer Applications (0975 8887) Volume 61 No.11, January 2013.

- [15] Mamta Gurjar and Shyam Akashe, "Design low power encoder for threshold inverter Quantization based Flash ADC Converter", International Journal of VLSI design & Communication Systems (VLSICS) Vol.4, No.2, Apr 2013.

- [16] H. Suzuki, M. Oikawa, K. Nishii, and M. Hidaka, "Investigation of a 5-bit Flash-Type SFQ A/D Converter Using 10 kA/cm2 Niobium Process and Locally Isolated Grounds", IEEE Transactions on Applied Supercondutivity, Vol. 23, No. 3, June 2013.

- [17] Amol Inamdar, Senior Member ,IEEE, Anubhav Sahu, Jie Ren, Aniruddha Dayalu, and Deepnarayan Gupta, Senior Member, IEEE "Flash ADC Comparators and Techniques for Their Evaluation", IEEE Transactions on Applied Suppercondutivity, Vol.23, No. 3, June 2013.

- [18] Snehalata Vichare, Assi. Prof. U.R. More, "Design of Digital Section of Pipeline Analog to Digital Converter", International Journal of Engineering Research & Technology (IJERT) Vol. 2 Issue 9, Sept 2013.

- [19] Dheepak Mohanraj, Department of EEE, AMET University Chennai, India, "Design of high speed pipelined ADC System", International Journal of

www.ijraset.com Volume 4 Issue I, January 2016 IC Value: 13.98 ISSN: 2321-9653

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

- Engineering Research & Technology (IJERT), Vol. 3 Issue 2, Feb 2014

- [20] Gulrej Ahmed, Rajendra Kumar Baghel, "6 bit flash analog to digital converter using variable switching voltage CMOS Comparator", International Journal of VLSI design Communication Systems Vol.5, No.3, June 2014.

- [21] Parthasarthy K. P. and Dr. K. C. Narasimhamurthy, "A Low Power Comparator Design for 6-Bit Flash ADC in 90nm CMOS", International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, Vol. 3, Issue 6, June 2014.

- [22] Xiaochen Yang, Member, IEEE, and Jin Liu, Senior Member, IEEE, "A 10 GS/s 6 b Time-Interleaved Partially Active Flash ADC", IEEE Transactions on circuits and systems-I: Regular papers, Vol. 61, NO. 8, Aug 2014.

- [23] S. S. KHOT, "6-Bit CMOS Flash ADC using TIQ Comparator in 0.250µm technology", International Journal of Electronics, Communication & Instrumentation Engineering Research and Development (IJECIERD) ISSN (P):Vol. 5, Issue 3, Jun 2015.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)