# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 4 Issue: V Month of publication: May 2016

DOI:

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

www.ijraset.com Volume 4 Issue V, May 2016 IC Value: 13.98 ISSN: 2321-9653

#### **International Journal for Research in Applied Science & Engineering Technology (IJRASET)**

### A Review on High Performance Low Power **Conditional Discharge Flip Flop**

Sonam Parihar<sup>1</sup>, Rachana Arya<sup>2</sup>

<sup>1</sup>P.G student, Bipin Tripathi Kumaon Institute of Technology, Dwarahat, Almora, Uttarakhand <sup>2</sup>Assistant professor, ECE Deptt, Bipin Tripathi Kumaon Institute of Technology, Dwarahat, Almora, Uttarakhand

Abstract: Different logic circuits have emerged as a major area of research due to its ability to reduce the power dissipation. This is the main requirement in the low power digital circuit design. It has wide applications like low power CMOS design, Nanotechnology, Digital signal processing. In this paper, the designing and analysis of the Conditional Discharging Flip flop circuit is presented. The simulation is done at 1V using TSMC 90nm technology.

Keywords: Flip flop, low power, Conditional discharge, Pulse triggered.

#### INTRODUCTION

Low power industry is growing at a very rapid rate. One of the factors behind this rapid growth is the hand held devices which operate on battery. The battery technology has not improved as compared to VLSI also if we employ more power to batteries there is a risk of explosion, so we have the only option i.e. to design new low power circuits and design techniques.

Flip flop design are basic storage elements used in all types of digital design. Flip flop design and performance has a effect in reducing the power dissipation and in high performance system. Microprocessors basically uses master slave and pulse triggered flip flop. Master slave are made up of two stages, one master and one slave characterized by their hard-edge property. Pulse triggered reduces two stages into one and are characterized by soft-edge property. Pulse triggered is more popular than master slave because of its single latch structure and high speed operation. The main advantage of pulse triggered is that it allows time borrowing across cycle a boundary which leads to high performance. A Pulse triggered flip flop consists of pulse generator and a latch. Pulse triggered flip flop can be static, or semi-static, or dynamic, or semi dynamic. Pulse triggered flip flop can also be classified into single-edge triggered clocked flip flop and double edge triggered clocked flip flop.

#### II. PROPOSED FLIP FLOP DESIGN

Pulse generator is classified as implicit pulse triggered and explicit pulse triggered flip flop on the basis of location of pulse generator. In implicit the pulse is generated inside the flip flop where as in explicit pulse is generated outside the flip flop. Implicit are more economical but suffer from a problem of long discharge. Explicit incurs more power consumption but the logic separation from latch design gives the flip flop design a unique speed advantage.

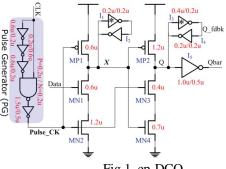

To provide a comparison few existing design are discussed here. Fig. show a classic explicit data close to output(ep-DCO). In this the FF, three inverters are used to determine the pulse width. The drawback of this design is that internal node X discharge on every rising edge of clock in spite of static input 1.

Fig.1. ep-DCO

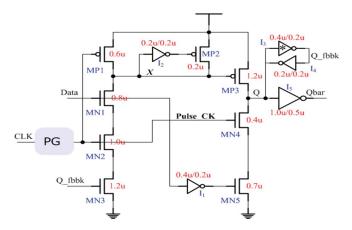

To overcome this problem many schemes have been proposed such as conditional discharge, conditional capture conditional precharge etc. In CDFF, fig (b) an extra nMOS is introduced so that no discharge occurs if input data remain 1. Here node X is also

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

simplified and consists of an inverter and a pull up pMOS transistor.

Fig. 2. CDFF

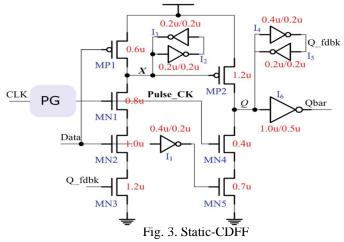

Similar to CDFF, static CDFF, fig (c), is proposed. The difference is in latching structure. Here node X is exempted from periodical precharge. It also exhibit longer D to Q delay as compare to CDFF. Both the design face a worst case delay because of three stacked transistor in the discharging path.

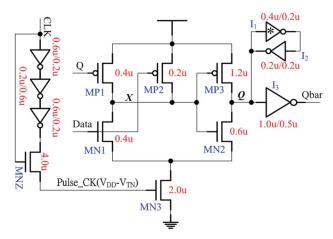

To overcome this delay MHLFF, fig (d) is introduced. MHLFF also uses static latch. The keeper logic at X is removed. But the drawback with this is that X floating in certain cases and its value may drift causing extra dc power.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

#### III. COMPARISON TABLE AND SIMULATED RESULTS

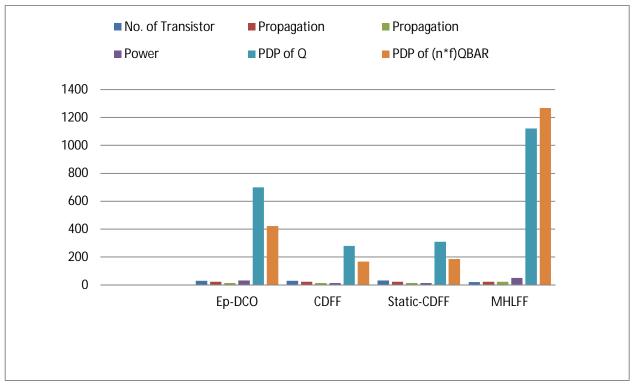

The simulation results for all the flip flop were obtained in a 90nm CMOS technology at room temperature using Tanner Tool 13, the supply voltage is 1.8V. A clock frequency of 250MHz is used for single-edge triggered flip flops, whereas double-edge triggered flip flops uses a a frequency of 125MHz. Comparison table shows the simulation results of various flip flops. In view of power consumption and PDP, CDFF has least value as compare to other flip flop.

TABLE I

| Flip Flop | No. of     | Propagation    | Propagation   | Power           | PDP of Q | PDP of  |

|-----------|------------|----------------|---------------|-----------------|----------|---------|

|           | Transistor | Delay of Q (n) | Delay of QBAR | Consumption (f) | (n*f)    | (n*f)QB |

|           |            |                | (n)           |                 |          | AR      |

|           |            |                |               |                 |          |         |

|           |            |                |               |                 |          |         |

| Ep-DCO    | 28         | 22.516         | 13.5259       | 31.1            | 699.75   | 420.47  |

| CDFF      | 30         | 22.511         | 13.5141       | 12.37           | 278.46   | 167.16  |

| Static-   | 31         | 22.512         | 13.51         | 13.79           | 308.414  | 185.08  |

| CDFF      |            |                |               |                 |          |         |

| MHLFF     | 19         | 22.50          | 25.47         | 49.8            | 1120.50  | 1268.4  |

|           |            |                |               |                 |          |         |

FEATURE COMPARISON OF VARIOUS FF DESIGN

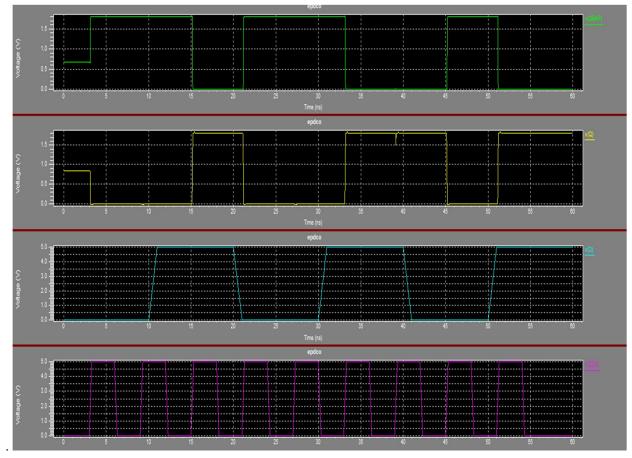

Fig.5. Waveform of ep-DCO

www.ijraset.com Volum

IC Value: 13.98

ISSN:

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

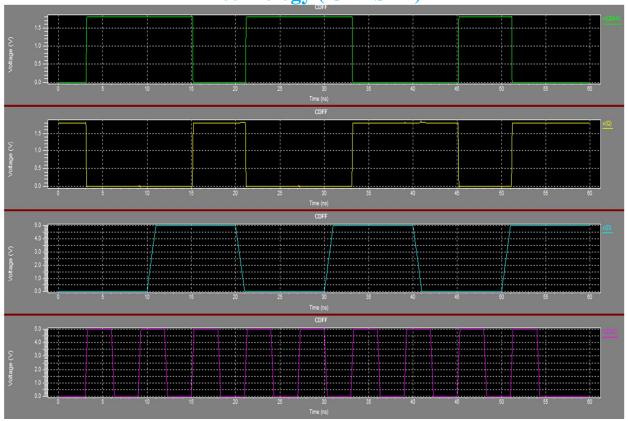

Fig.6 Waveform of CDFF.

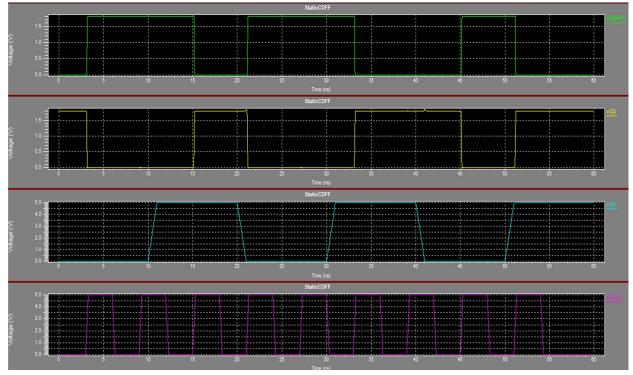

Fig.7. Wavefrom of Static-CDFF.

www.ijraset.com Volume IC Value: 13.98 ISSN: 2

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

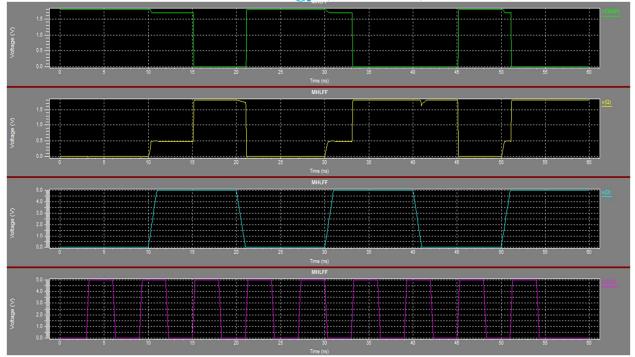

Fig.8. Waveform of MHLFF.

Fig.8. Comparison of different characteristics Flip-Flop.

#### IV. CONCLUSION

In this paper, four flip flops are studied and compared. Both single edge and dual edge clocked flip flop are discussed. Dual edge triggered clocked flip flop consumed less power. Delay, number of transistor, average power consumed and power delay product of different flip flops designs is compared. The quality and performance of a CMOS process and gate design is measured in terms of

www.ijraset.com Volume 4 Issue V, May 2016 IC Value: 13.98 ISSN: 2321-9653

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

power-delay product. The power-delay product can be interpreted as the average energy required for a gate to switch its output from low to high and from high to low. The simulation is performed in 90nm technology CMOS technology, using power supply of 1.8V and clock frequency of 250MHz.

#### **REFERENCES**

- [1] Jin-Fa Lin, "Low-Power Pulse-Triggered Flip-Flop Design Based on a Signal Feed-Through Scheme" IEEE Transactions On Very Large Scale Integration (VLSI) Systems, Vol. 22, No. 1, January 2014.

- [2] F. Zhao, T. Darwish, M. Bayoumi, "High-performance and low power conditional discharge flip-flop", IEEE Trans. Very Large Scale Integration. (VLSI) Syst., Vol. 12, No. 5, pp. 477–484, May 2004.

- [3] JuhiRastogi, vipul Bhatnagar, "Low power high performance pulse FF based on signal feed scheme" IJATES, vol 3, issue no 01, March 2015.

- [4] [4]Yin-Tsung Hwang, Jin-Fa Lin and Ming-HwaSheu. "Low-power Pulse-triggered flip flop Design with Conditional Pulse-Enhancement Scheme" IEEE Transaction On Very Large Scale Integration (VLSI) Systems, Vol. 20, No. 2, January 2014.

- [5] [5]Kanika Jindal, Renu, V K Pandey, "Design of Conditional Data Mapping Flip Flop for Low Power Applications," IJISME, vol 1, issue 5, April 2013.

- [6] [6]CMOS Digital Intergrated Circuits, Analysis and Design by Sung-Mo Kang and Yusuf Leblebici.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)