IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 4 Issue: V Month of publication: May 2016 DOI:

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

## International Journal for Research in Applied Science & Engineering Technology (IJRASET) Study on Performance of Vedic Multiplier Based On the Adders Used

Rose Ann Mathew<sup>1</sup>, Shruthi.H.Shetty<sup>2</sup>, Ashwath Rao<sup>3</sup>, Deepthi Dayanand<sup>4</sup>, Megha N<sup>5</sup>, Savidhan Shetty<sup>6</sup>

<sup>1,2</sup>*M.Tech in VLSI Design & Embedded Systems,* <sup>3</sup>*Associate Professor,* <sup>4,5,6</sup>*Assistant Professor* <sup>3,4,5,6</sup>*Dept. Electronics & Communication Engineering ,Sahyadri college of Engineering & Management, India*

Abstract— In ALUs, DSPs, and microprocessors addition and multiplication are most commonly used arithmetic computation. Multipliers play a key role in determining the overall performance of the system design. But multipliers use more processer time thus diminishing the overall system performance. Thus to maintain high throughput it is important to select high speed multipliers in terms of low area, low power, less delay. Multiplier involves generation of partial products and also their addition. Vedic mathematics is considered to be a powerful tool for enhancing the calculation speed. It speeds up the multiplication by generation of partial product. Vedic multiplier is considered to be faster multiplier when compared to the other multipliers. The speed of multipliers is based on the adders used for the addition of partial products. In this paper performance of Vedic multipliers are discussed based on the adders used.

Keywords— Vedic multiplier, Urdhva-Tiryakbhaym sutra, 2x2Vedic multiplier, 4x4Vedic multiplier

#### I. INTRODUCTION

Many instructions in Microprocessor and most of the DSP algorithms perform operations like addition and multiplication; hence addition and multiplication operation play a crucial role in execution time. The demand of high speed processors is increased due to the increasing demand of computer and signal processing applications. To achieve desired performance in many real-time applications, it is highly essential to select high performance multiplier with low power, area and delay. Employing Vedic techniques in computation algorithm of processors reduces the complexity, execution time of the system, power, area etc. Vedic multiplier (VM) is the fastest multiplier and it is based on Vedic multiplication formulae called sutra. Advantage of VM is that the generation of partial product and their addition are done concurrently. Vedic Mathematics is mainly based on 16 sutras where 2 sutras commonly used for multiplication are "Urdhva-Tiryakbhyam (UT) and Nikhilam Sutra". Nikhlim sutra is basically used for larger numbers which are nearer to their base. Urdhva-Tiryakbhyam sutra means "vertical-crosswise" multiplication. In this technique the partial products and sums are generated parallelly. This sutra is applicable for all cases of multiplication. Here in this paper we consider the Vedic Multiplier based on Urdhva-Tiryakbhyam sutra. Since speed of adders is also considered for speed of multiplication it is important to select adders with high throughput. Reducing delay is advantages since it increases the speed.

#### **II. VEDIC MULTIPLIER**

Vedic Mathematics is simple to understand than the conventional mathematics. After eight years of research by Swami Bharati Krishna Tirthaji Maharaja Vedic Mathematics was reconstructed from the "Ancient Indian Scriptures (called Vedas). Multipliers' using Vedic mathematics reduces the complexity in computation and helps to achieve the desired performance of the system i.e. integrating Vedic Mathematics in Multiplier design enhances the speed of operation. In this paper the discussed multiplier architecture is based on Urdhva-Tiryakbhyam sutra. The line diagram for 4-bit multiplication of UT sutra is as shown in Figure 1. Considering an example of decimal numbers (192 x 135) in step1, first the product of 2 LSBs of multiplier and multiplicand is taken, i.e. The product obtained is stored and the carry generated is added to the result of next stage. In next step, the two LSBs (of multiplier and multiplicand) are multiplied crosswise and their product generated is added with the previous carry from step1. In further step the product of middle bits are taken and summed and carry is propagated to next stage. In the last step the 2 MSBs are multiplied and added with carry propagated from previous stage. Therefore the final result is obtained from concatenating the product from each step and carry in last step.

Fig 1: line diagram for 4-bit multiplication of UT

International Journal for Research in Applied Science & Engineering Technology (LIRASET)

| Step1:                                                | step2:               | step3:             |  |  |

|-------------------------------------------------------|----------------------|--------------------|--|--|

| 192 rslt: 10                                          | 1 9 2 rslt: 51       | 192 rslt: 34       |  |  |

| 135 pvCry: 0                                          | 135 pvCry: 1         | 135 pvCry: 5       |  |  |

| 0 1 0<br>carry= 1                                     | 2 0 52<br>carry= 5   | 920 39<br>carry= 3 |  |  |

| step4:                                                | step5:               |                    |  |  |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | 2   1 9 2<br>  1 3 5 |                    |  |  |

| 5920 1<br>carry=1                                     | $\langle$            | 200 2<br>35=25290  |  |  |

|                                                       |                      |                    |  |  |

Fig 2: illustration of UT sutra using decimal numbers

Let us consider two numbers  $x = x_0 x_1$  and  $y = y_0 y_1$  as shown in line diagram. First the final product is obtained by taking the product of 2 LSB's i.e.  $x_0$  and  $y_0$ , in second step the product of the LSB of x with the higher bit of y is taken in crosswise manner, the output carry generated is added to the result of the next step. Next step is to take product of 2 MSB's.

$$\begin{array}{l} S_0 = x_0 y_0 \hdots (1) \\ C_1 S_1 = x_1 y_0 + x_0 y_1 \hdots (2) \\ C_2 S_2 = C_1 + x_1 y_1 \hdots (3) \end{array}$$

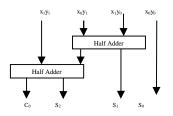

The final result obtained is  $C_2S_2 C_1S_1 S_0$ . The 2x2 Vedic multiplier consists of four AND gate and two half adder. The advantage of this multiplier is that as the bit increases the area and delay increases very slowly, hence it is faster when compared with other multipliers. Hence total delay is the sum of delay of 2 half adders after partial product generation.

Figure 3: 2x2 Vedic Multiplier

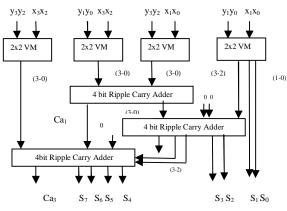

For 4x4 multiplication let us consider two 4-bit numbers x and y i.e.  $x = x_3 x_2 x_1 x_0$  and  $y = y_3 y_2 y_1 y_0$ . The procedure for multiplication is explained in the line diagram shown above (figure 1). Therefore the final result is  $C_6S_6 C_5S_5 C_4S_4 C_3S_3 C_2S_2 C_1S_1 S_0$ . Since the partial products are calculated parallelly the delay can be reduced as the number of bit increases.

| $\mathbf{S}_0 = \mathbf{x}_0 \mathbf{y}_0$                        | (4)  |

|-------------------------------------------------------------------|------|

| $C_1S_1 = x_1y_0 + x_0y_1$                                        | (5)  |

| $C_2S_2=C_1+x_0y_2+x_2y_0+x_1y_1$                                 | (6)  |

| $C_3S_3 = C_2 + x_0y_3 + x_3y_0 + x_1y_2 + x_2y_1$                | (7)  |

| $C_4S_4\!\!=\!\!C_3\!\!+\!\!x_1y_3\!\!+\!\!x_3y_1\!\!+\!\!x_2y_2$ | (8)  |

| $C_5S_5 = C_4 + x_3y_2 + x_2y_3$                                  | (9)  |

| $C_6S_6 = C_5 + x_3y_3$                                           | (10) |

The 4x4 multiplication can be implemented using four 2x2 vedic multiplier modules and three ripple carry adders of 4-bit size is used. 4-bit RCA is used for the addition of two 4-bit numbers. The arrangement of RCA is as shown in the figure, which reduces the computation time thus reducing the delay to give better performance

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Figure 4: 4x4 Vedic Multiplier

### **III. SURVEY DESIGNS**

**J. Thomas et.al** [1] has compared the performance of Vedic multiplier in terms of area, delay and power on the basis of adder used. Here they compared 8x8 Vedic multiplier based on different adders used and the factors considered are delay, area and power. This analysis is done to find the suitable design of multiplier to achieve the desired applications like low area, low power and low delay. These factors are compared for different adders such as carry Lookahead adder (CLA), carry select adder (CSLA), parallel prefix adders like Kogge stone adder (KSA), Ladner Fischer adder (LFA) and Brent Kung adder (BKA) in Vedic multiplier. This paper gives information about Urdhva-Tiryakbhyam algorithm of Vedic Mathematics that is utilized for multiplication and also gives brief description about adders that can be used in Vedic multiplier ,to improve the speed and area of multiplier.

| CADENCE | Adders | Area (slices) | Power(mW) | Delay (nsec) |

|---------|--------|---------------|-----------|--------------|

| &XILINX | CLA    | 89            | 57.2      | 29.981       |

|         | CSLA   | 93            | 42.2      | 28.644       |

|         | KSA    | 105           | 57.3      | 31.788       |

|         | LFA    | 89            | 57.2      | 28.981       |

|         | BKA    | 91            | 57.0      | 29.944       |

Table 1: Comparative study of various adders used in Vedic multiplier

The above table gives the analysis report of the 8x8 Vedic multipliers with fast adders on the basis of parameters area, delay and power. Among parallel prefix adders in terms of area and delay LFA shows the better performance but the disadvantage is that it has larger fan-out. Though KSA has large area and delay compared to LFA and BKA it has lesser fan-out when compared to both. CLA is better in terms of speed and delay when compared with other adders. Thus after analysis it is sad that CSLA being the fastest adders, it will best adder for designing of Vedic Multiplier (VM).

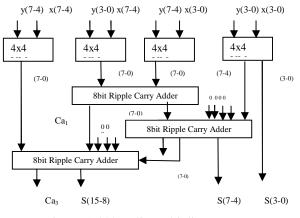

Figure 5: 8\*8 vedic multiplier

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

**S.Tamilselvan et.al [2]** in their paper they have mainly focused on the reducing the time delay of the multiplication operation. The Vedic multipliers (VM) are implemented with the adders having lesser time delay. The comparison is done in between ripple carry adder, carry lookahead adder, carry skip adder and carry select adder. Comparison says that carry select adder has lesser time delay compared to others. Hence CSLA is used in VM for addition process. VM can be used in FFT algorithms.

|        | Adders | Area(slices) | Delay(nsec) |

|--------|--------|--------------|-------------|

|        | CLA    | 10           | 6.494       |

| XILINX | RCA    | 6            | 7.682       |

|        | CSLA   | 6            | 6.494       |

|        | CSkip  | 8            | 6.494       |

Table 2: Comparison of 4 Bit Adders Based On Time Delay

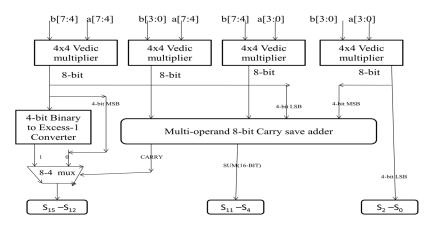

**P.Devpura et.al [3]**, in their paper, a novel 8\*8 bit Vedic multiplier which is based on "Urdhva triyakbhyam sutra" is proposed and it uses Binary to Excess-1 code converter, as its key component to increase the speed and reduce the area utilized by the multiplier. They have also compared area, delay and power with the existing topologies. The proposed architecture shows the better performance when compared to others, thus fulfilling the motivation of both reduced delay and area.

| Vedic Architecture                            | Delay<br>(ns) | Logic<br>Delay(ns) | Route<br>Delay(ns) | Slice Utilization |

|-----------------------------------------------|---------------|--------------------|--------------------|-------------------|

| Conventional<br>Architecture                  | 21.644        | 10.893             | 10.751             | 119               |

| Carry Save Adder<br>Based Architecture        | 21.608        | 11.372             | 10.236             | 104               |

| Carry Save<br>Adder+BEC based<br>Architecture | 18.139        | 9.996              | 8.143              | 100               |

Table 3: Comparison of BEC-1 based multiplier with existing topology

Figure 6: Proposed BEC-1 based Vedic multiplier

In this proposed architecture is divided into 4 blocks 4x4 Vedic multiplier Multi-operand carry Save adder Binary to Excess-1 Converter 8:4 Mux The multi-operand carry save adder reduces the addition on 3 numbers into 2 numbers. The purpose of using BEC-1 is to reduce the www.ijraset.com IC Value: 13.98

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

computation time for addition and decrease the delay. The 8:4 Mux is used for conditional addition, it selects the output of BEC-1 if the carry generated by Multi-operand carry save adder is zero else output is taken directly from the partial product generated by 4x4 VM if the carry =1. The 4x4 VM uses 2x2 VM modified by multi-operand carry save adder.

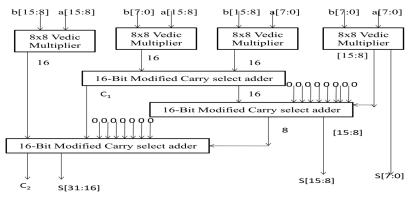

**Bhavani Prasad.Y et.al [8],** have described the design of low power and high speed Modified Carry Select Adder for 16 bit Vedic Multiplier. In this paper, a high speed and low power 16x16 Vedic Multiplier is designed by using low power and high speed modified carry select adder. This gives less power consumption when compared to other multiplier techniques because the number of additions gets reduced by applying Urdhva-Tiryakbhyam which is a short approach form of multiplication. In this paper the proposed 16-bit modified CSLA consists of

Ripple Carry Adder

Basic Unit (Binary to Excess-1 Converter)

Multiplexer

Ripple Carry adder (RCA) is called as Ripple carry adder because each carry bit "ripples" to the next full adder. RCA is designed using multiple full adders, which allows for fast design time since RCA layout is simple. Binary to Excess-1 converter (BEC) is designed using XOR, AND and NOT gates, which reduces the area, time delay and power consumption since it uses less number of gates compared to normal RCA. The expressions for 4-bit BEC is given below

$$\begin{split} & E_0 = \sim B_0 & (11) \\ & E_1 = B_0 \wedge B_1 & (12) \\ & E_2 = B_2 \wedge (B_0 \& B_1) & (13) \\ & E_3 = B_3 \wedge (B_0 \& B_1 \& B_2) & (14) \end{split}$$

Multiplexers (Mux) are used for the selection of output between RCA and BEC. Multiplexer is also called as Data selector. It has  $2^n$  inputs and n select lines. Depending on the select lines the input is send to the output. Therefore this 16- bit modified CSLA reduces the computation time such that the delay decreases. The proposed 16x16 VM using Modified CSLA is as shown

Figure 7: Proposed 16x6 VM architecture [8]

This proposed multiplier has very less delay, because of the addition of new 16-bit modified CSLA module. This proposed VM consumes less power because the number of addition is reduced by applying UT sutra, which is the short approach for multiplication. This technique can be used for DSP applications and also for low power applications.

### **III. CONCLUSION**

This paper presents the brief study on Vedic multiplier based on adders used. Vedic multiplier is designed using various adders to achieve high speed, low area, low power consumption, and reduced delay. Vedic multipliers can be used in different fields of applications like Digital Signal Processing (DSPs), FFT algorithms, Convolution, Multiplication and Accumulation (MAC) unit and in many microcontroller and microprocessors.

#### REFERENCES

- [1] Josmin Thomas, R. Pushpangadan, "Comparative Study of Performance Vedic Multiplier on The Basis of Adders Used", IEEE International WIE Conference on Electrical and Computer Engineering, December 2015.

- [2] S.Tamil selvan, V. Anil Kumar, V. Kamal kannan, CH. V.M. S. N. Pavan Kumar, "Design, Analysis and FPGA Implementation of N Bit Vedic Multiplier Based on Different Adder Architectures" International Journal of Advanced Research in Computer and Communication Engineering Vol. 4, Issue 8, August 2015.

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

- [3] Prachi Devpura, Anurag Paliwal, "High Throughput Vedic Multiplier Using Binary To Excess-1 Code Converter"

- [4] Gaurav Sharma, Arjun Singh Chauhan, Himanshu Joshi, Satish Kumar Alaria, "Delay Comparison of 4 by 4 Vedic Multiplier based on Different Adder Architectures"

- [5] D.Muthulakshmi, S.Durgadevi, B.Iyyappan, "High Speed and Reduced Area 16 bit Vedic Multiplier Using Carry Select Adder", International Journal of Advanced Research Trends in Engineering and Technology (IJARTET) Vol. II, Issue III, March 2015.

- [6] N.G.Nirmal, Dr. D.T.Ingole, "Novel Delay Efficient Approach for Vedic Multiplier with Generic Adder Module"

- [7] Shiksha Pandey, Deepak kumar, "Comparison of Efficient and High Speed Adders for Vedic Multipliers: A Review", International Journal of Engineering Trends and Technology (IJETT) – Volume 29 Number 5 - November 2015.

- [8] Bhavani Prasad.Y, Ganesh Chokkakula, Srikanth Reddy.P and Samhitha.N.R, "Design of Low Power and High Speed Modified Carry Select Adder for 16 bit Vedic Multiplier"

- [9] Shilpi Thawait, Jagveer Verma, "FPGA Implementation of Simple and High Speed Vedic Multiplier"

- [10] Y. N. Rao, G. S. V. P. Raju, and P. V. K. Raja, "Studies and performance evaluation of vedic multiplier using fast adders," IJCET, June2014, INPRESSCO, Vol4, no. 3, 2014.

- [11] B. Ramkumar and H. M. Kittur, "Low-power and area-efficient carry select adder," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 2, pp. 371– 375, Feb. 2012.

- [12] B. K. Mohanty and S. K. Patel, "Area-delay-power efficient carry select adder," IEEE Trans. Circuits and Systems. vol. 61, no. 6, pp. 418422, June 2014.

- [13] Y. Narasimha RaoÅ, G.Samuel Vara Prasada Raju and Penmetsa V Krishna Raja, "Studies and Performance Evaluation of Vedic Multiplier using Fast Adders"

- [14] Basant Kumar Mohanty and Sujit Kumar Patel, —Area–Delay–Power Efficient Carry-Select Adderl, IEEE Transaction on Circuits and Systems—II: Express Briefs, VOL. 61, NO. 6, June 2014.

- [15] B.Ramkumar , Harish M Kittur, "Low power and area efficient carry select adder", IEEE 2014.

- [16] Elakkiya.J, Mathan.N, "Survey on Performance of Vedic Multiplier", International Journal of Advanced Research in Computer and Communication Engineering Vol. 4, Issue 2, February 2015.

- [17] V. Jindal, M. N. Z. Rizvi, and D. K. Singh, "Vhdl code of vedic multiplier with minimum delay architecture."

- [18] Ms. G. R. Gokhale, Ms. P. D. Bahirgonde, "Design of Vedic-Multiplier using Area-Efficient Carry Select Adder"

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)