IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 4 Issue: VII Month of publication: July 2016 DOI:

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

## International Journal for Research in Applied Science & Engineering Technology (IJRASET) Design of Reconfigurable OFDM and CDMA Transceiver Based On FPGA

Sharpavati Myalagi<sup>1</sup>, Dr.Baswaraj Gadgay<sup>2</sup>, Suman B Pujari<sup>3</sup> <sup>1</sup>PG Student, Dept. of VLSI Design & Embedded System. <sup>2</sup>Research Guide & Professor, <sup>3</sup>Assistant Professor Dept. of VLSI&ES VTU PG Centre Kalaburagi, Karnataka, India.

Abstract - The rapid expansion in digital Wireless communications results in a demand for systems that are reliable and have a high spectral efficiency. To fulfill these demands, the multicarrier modulation scheme, often called Orthogonal Frequency Division Multiplexing (OFDM), has drawn a lot of attention. On the other hand Code Division Multiple Access (CDMA) techniques have been considered to be a candidate to support multimedia services in mobile radio communications. In this work, Space-Time Block Coding is a technique used in wireless communications to transmit multiple copies of a data stream across a number of antennas and to exploit the various received versions of the data to improve the reliability of data-transfer. The fact that the transmitted signal must traverse a potentially difficult environment with scattering, reflection, refraction and so on and may then is further corrupted by thermal noise in the receiver means that some of the received copies of the data will be better than others.

Keywords- Orthogonal Frequency Division Multiplexing (OFDM), Code Division Multiple Access (CDMA), Field Programmable Gate Array (FPGA).

I.

#### INTRODUCTION

A Space Time Code is a method employed to improve the reliability of data transmission in wireless communication systems using multiple transmit antennas. STCs rely on transmitting multiple, redundant copies of a data stream to the receiver in the hope that at least some of them may survive the physical path between transmission and reception in a good enough state to allow reliable decoding. In recent years there has been a constant development of wireless standards due to the demand for broadband access and the proliferation of applications for wireless communication systems. These wireless standards operate over multiple frequency bands with different modulation formats. Hence, radiofrequency (RF) front ends, and particularly their transmitters, are expected to handle diverse signals at different frequencies while meeting requirements in terms of power efficiency and signal quality. Therefore, re-configurability is a key issue of present and developing communication systems to provide greater system flexibility allowing devices to operate in a number of different radio access networks (RAN). Furthermore, re-configurability reduces manufacturing and maintenance costs. The final objective may be to put into practice software defined radio (SDR) technologies where either the network provider or the user can control the communication standard or the operating frequency band.

#### A. Orthogonal Frequency Division Multiplexing (OFDM)

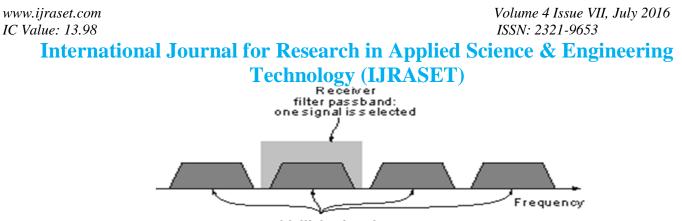

OFDM is a form of multicarrier modulation. An OFDM signal consists of a number of closely spaced modulated carriers. When modulation of any form - voice, data, etc. is applied to a carrier, then sidebands spread out either side. It is necessary for a receiver to be able to receive the whole signal to be able to successfully demodulate the data. As a result when signals are transmitted close to one another they must be spaced so that the receiver can separate them using a filter and there must be a guard band between them. This is not the case with OFDM. Although the sidebands from each carrier overlap, they can still be received without the interference that might be expected because they are orthogonal to each another. This is achieved by having the carrier spacing equal to the reciprocal of the symbol period.

Multiple signals Fig 1: Traditional view of receiving signals carrying modulation

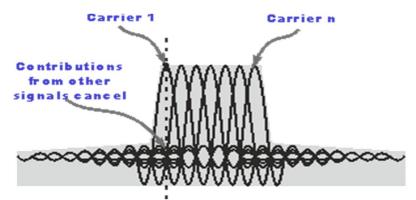

To see how OFDM works, it is necessary to look at the receiver. This acts as a bank of demodulators, translating each carrier down to DC. The resulting signal is integrated over the symbol period to regenerate the data from that carrier. The same demodulator also demodulates the other carriers. As the carrier spacing equal to the reciprocal of the symbol period means that they will have a whole number of cycles in the symbol period and their contribution will sum to zero - in other words there is no interference contribution.

Fig 2: OFDM Spectrums

One requirement of the OFDM transmitting and receiving systems is that they must be linear. Any non-linearity will cause interference between the carriers as a result of inter-modulation distortion. This will introduce unwanted signals that would cause interference and impair the orthogonality of the transmission.

#### B. Code Division Multiple Accesses (CDMA)

Code division multiple access (CDMA) is a channel access method used by various radio communication technologies. It should not be confused with the mobile phone standards called CDMA one, CDMA2000 (the 3G evolution of CDMA one) and WCDMA (the 3G standard used by GSM carriers), which are often referred to as simply CDMA, and use CDMA as an underlying channel access method.

#### II. RELATED WORK

As the demand for system-on-chip (SOC) implementations increases, the need to accurately model mixed signal designs becomes more important. Digital designs have been highly automated, and the prevalence of top down design is very strong in this area. In contrast, traditional analog RF designs are normally bottom-up, starting at the transistor level. Mixed-signal designers must then take a combination of hierarchical design approaches, and effort is being made to automate this design flow in a similar manner as seen for current digital systems. The overall goal is to provide designers tools to allow the combination of digital and RF models at the net list level, creating a physical SOC model from which masks can be made for quick prototyping and fabrication. The ability to model and co-simulate digital and RF components together was made possible by the creation of hardware description languages (HDLs) such as VHDL and Verilog. That requires the development of high-level behavioral models for mixed-signal systems blocks. Later, the abstraction levels of these models can be reduced to more accurately model physical circuit implementations.

Digital modulation is less complex, more secure and more efficient in long distance transmission. The noise detection and correction in digital is more efficient than analog counterpart. So it has more importance in modern communication. Digital

#### www.ijraset.com IC Value: 13.98

#### *Volume 4 Issue VII, July 2016 ISSN: 2321-9653*

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

modulation represents the transfer of the digital bit stream from the transmitter to the receiver via the analog channels. During the modulation process the information signal modifies one or more carrier parameters, leading to shift keying techniques. A very widespread solution is the Software Defined Radio (SDR), whose modulation/demodulation methodology consists in programming either software in a dedicated processor (DSP), or logic in a programmable logic device (FPGA). An SDR (Software Defined Radio) is a radio in which the properties of carrier frequency signal bandwidth, modulation, and network access are defined by software. Today's SDR, in contrast, is a general-purpose device in which the same radio tuner and processors are used to implement many waveforms at many frequencies. Its idea is to get the software as close to the antenna as is feasible. Ultimately, we're turning hardware problems into software problems. To enable such functionality SDR is using reconfigurable hardware platform such as Field Programmable Gate Array (FPGA) so we are going to design reconfigurable OFDM & CDMA transceiver on FPGA.

III. PROPOSED WORK

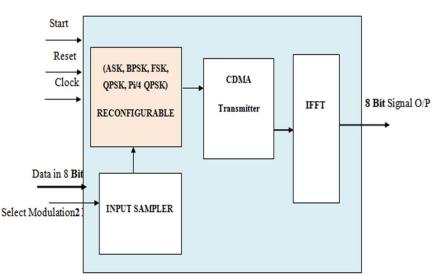

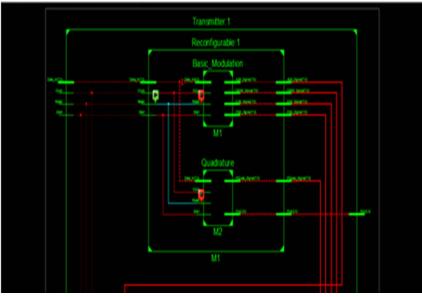

Fig 3: Block Diagram of Reconfigurable Transmitter

#### A. Input Sampler

Sampler is also called as 'Bit separator or Bit Splitter'Separating indusial Bits given digital data by Parallel to Serial Conversion Normally called Bit Splitter. This block produces separate bits with the help of clock select line from the clock distribution with specified count. For QPSK input sampler separates the bit two bits at a time, the forming two bits called as the one symbol. As we can see in below figure of input sampler it consists of mux and D-Flip Flop, the 8bit data in is given to mux and based on the select line the particular bit will be stored in the D-filp flop. QPSK parallel processing of Two bits are there so bit splitting should be for two bit so separating I Bit & Q Bit from the given digital data by Parallel to Serial Conversion Normally called Bit Splitter.

#### B. Reconfigurable Block

In reconfigurable unit the process corresponds to switch keying the amplitude frequency, or phase of the carrier signal changes with the incoming digital data so there are few basic digital modulation techniques are as follows:

- 1) Amplitude shift keying (ASK)

- 2) Frequency shift keying (FSK)

- 3) Phase shift keying (PSK)

- a) Binary PSK (BPSK)

- b) Differential PSK (DPSK)

- *c)* Quadrature Phase Shift Keying (QPSK)

- d)  $\pi/4$  Quadrature Phase Shift Keying (QPSK)

Volume 4 Issue VII, July 2016 ISSN: 2321-9653

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

C. CDMA Transmitter

www.ijraset.com

IC Value: 13.98

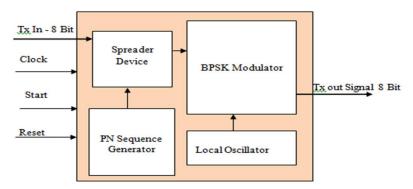

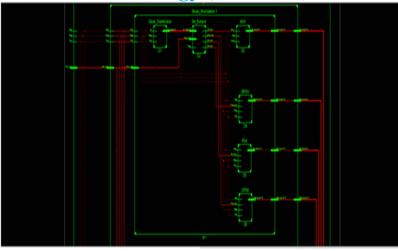

Fig 4: Functional Block diagram of CDMA Transmitter

The basic construction blocks of a CDMA transmitter scheme are shown above Fig 4. The transmitter of CDMA consists of PN Sequence Spreader Device, BPSK Modulation and Local Oscillator, the input data bits are given to spreader device in the Spreader device block the multiplied with the extend by PN series generator output.

- PN Sequence Generator: This is main diagram of CDMA transmitter is the PN chronological generator. A PN series or code is

a binary series sequence that produces predictability characteristics with help of the shit register it generates N number of

sequence for the different input only based on the timing or clock.

- 2) Spreader Device: In the block the original information of bits are xor with the PN Sequence. This block works as coding to original information.

#### D. Inverse Fast Fourier Transform (IFFT)

It is the one of the important module in the OFDM system. To compute IFFT first exchange real and imaginary parts then perform FFT. After performing FFT then exchange real and imaginary terms then it is the IFFT and finally divide the by N. where N is the number of points, here we are using 8- point FFT so divide the results by 8. The output of the IFFT is applied to the Digital to analog converter is used to convert the digital data into OFDM signals and these symbols are transmitted through the transmitting system.

Fig 5: RTL model of internal view of Reconfigurable transmitter

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig 6: RTL schematic for Basic modulation

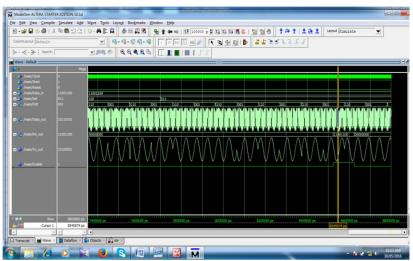

Fig 7: Simulation results of FSK modulation

Fig 8: Simulation result of QPSK Modulation

www.ijraset.com IC Value: 13.98

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

## V. CONCLUSION

In the proposed design we have successfully implemented Reconfigurable OFDM & CDMA transceiver with transmitter as well as receiver with inside block likes, IFFT, FFT, Input Sampler, PN Sequence, Design of Spreader device, and BPSK Modulation, Clock Divider, Sampling block, demodulation, Serial in parallel out (SIPO), and matched filter, all this functional blocks are designed by using a VHDL and functionality will be A verified using ModelSim also we synthesized on Altera Cyclone IV FPGA.

#### REFERENCES

- [1] Adahland H. Zirath, "A 1AGHzAclass EALDMOS power amplifier" in A33rd Eur. Microw. Conf., Oct. A2003, volA.1, ppA285-

- [2] J. Jeong D Kimball M. Kwak, PA Draxler, C. Hsia, C. Steinbeiser, T. Landon, O. Krutko, L. Larson, and P. Asbeck, "High efficiency WCDMA envelope tracking base station amplifier implemented with GaAs HVHBTs," IEEEAJ. Solid State Circuits, vol. A44, no.A10, ppA2629A2639, Oct. 2009.

- [3] D Gustafsson, CAMA Andersson, CA Fager, "A novel wide band reconfigurable high average efficiency power amplifier," in IEEEAMTT-International Microwave Symposium Digest, JuneA2012, volA1, pp. 1A3.

- [4] J. AR. Perez Cisneros AP. Garcia-Ducar, PA Carro, Valdovinos, J. de Mingo, "Performance enhancement of RF wideband power amplifier by reconfigurable matching networks," in 11th International Multi-Conference on Systems, Signals and Devices, Feb].

- [5] D. Y. Wu, S. Boumaiza, "A Mixed-Technology Asymmetrically Biased Extended and Reconfigurable Doherty Amplifier with Improved Power Utilization factor," IEEE Trans. Microw. Theory Tech., vol. 61, no. 5, pp. 1946-1956, may 2013.

- [6] A.M. Mahmoud Mohamed, S. Boumaiza, R.R. Mansour, "Reconfigurable Doherty Power Amplifier for Multifrequency Wireless Radio Systems," IEEE Trans. Microw. Theory tech vol. 61, no. 4, pp. 1588-1598, Apr. 2013.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)