IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: III Month of publication: March 2017 DOI: http://doi.org/10.22214/ijraset.2017.3185

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

www.ijraset.com IC Value: 45.98 Volume 5 Issue III, March 2017 ISSN: 2321-9653

# International Journal for Research in Applied Science & Engineering Technology (IJRASET) Implementation of Zigbee Transmitter using Verilog

Prof. Mr. YRK. Paramahamsa<sup>1</sup>, S. Usman Basha<sup>2</sup>, S. Mallika<sup>3</sup>, S. Naveed<sup>4</sup>, N. Ambika<sup>5</sup> <sup>1,2,3,4,5</sup>BITS Kurnool

Abstract: The previous quite a while have seen a fast advancement in the remote system region. So far remote systems administration has been centred around fast and long range applications. Sigsbee innovation was created for a Remote Individual Zone Systems (WPAN), went for control and military applications with low information rate and low power utilization. Sigsbee is a standard characterizes the arrangement of correspondence conventions for low-information rate short-go remote systems administration. Sigsbee-based remote gadgets work in 868 MHz, 915 MHz, and 2.4 GHz recurrence groups. The greatest information rate is 250K bits for every second. Zigbee is fundamentally for battery-controlled applications where low information rate, minimal effort, and long battery life are principle necessities. Improvements of advanced arrangements have been conceivable because of good computerized framework plan and demonstrating systems. Keywords: Include at least 5 keywords or phrases

#### I. INTRODUCTION

Sigsbee is a detail for a suite of abnormal state correspondence conventions utilizing little, low-control advanced radios in light of an IEEE 802 standard for individual territory systems. Sigsbee gadgets are frequently utilized as a part of work system shape to transmit information over longer separations, going information through transitional gadgets to achieve more removed ones. This permits Sigsbee systems to be framed impromptu, with no brought together control or high-control transmitter/beneficiary ready to achieve the majority of the gadgets. Any Zigbee gadget can be entrusted with running the system. Zigbee is not planned to bolster control line organizing but rather to interface with it in any event for keen metering and shrewd machine purposes. Since Zigbee hubs can go from rest to dynamic mode in 30 ms or less, the inactivity can be low and gadgets can be responsive, especially contrasted with Bluetooth wake-up deferrals, which are commonly around three seconds. Since Zigbee hubs can rest more often than not, normal power utilization can be low, bringing about long battery life.

#### II. LITERATURE SURVEY

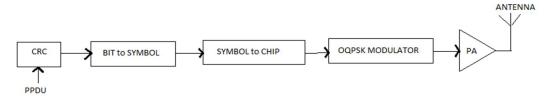

The recognize outline utilized contains 11 octets (i.e. 88 bits) of physical convention information unit (PPDU). The twofold information from the PPDU parcel are embedded into the cyclic excess check square to recognize blunders amid transmission. Each four bits of PPDU octet are mapped onto one information image, which will occur in bit-to-image square. The images will be spread into 32-chip PN arrangement by using Direct Succession Spread Range technique in Image to-chip piece. At that point, the chips will be tweaked utilizing OQPSK method.

The Zigbee computerized transmitter is intended for an affirmation casing which is appeared in Figure in view of IEEE 802.15.4 standard. This is the least complex Macintosh outline organize and does not convey any Macintosh payload. This casing is built from Macintosh header (MHR) and Macintosh footer (MFR). The casing control field and direct succession number (DSN) shape the MHR. The MFR is made out of 16-bit outline check grouping (FCS). Both MHR and MFR are known as PHY administration information unit (PSDU), which turns into the PHY payload. The PHY payload is prefixed with the synchronization header (SHR) contained preface arrangement, begin of casing delimiter (SFD), and PHY header (PHR). Together with the SHR, PHR and PHY payload shape the PHY convention information unit (PPDU).

# **International Journal for Research in Applied Science & Engineering**

# **Technology (IJRASET)**

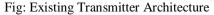

# III. PROPOSED METHOD

A Zigbee transmitter is to be intended for PHY and Macintosh layer for an affirmation outline. This outline will be displayed utilizing Verilog HDL and mimicked through Xilinx. The range and execution of operation of the proposed configuration ought to fulfill the hypothetical determinations and will be checked with the recreation comes about. Since the yield of the modulator is not guaranteed to be transmitted without mistake. Along these lines, with a specific end goal to evade such mutilations, we have to include Heartbeat forming hinder at the yield of OQPSK modulator. This will maintain a strategic distance from Entomb image Obstruction and some transmission commotions.

Fig: Proposed Transmitter Architecture

# A. Design Methodology

Cyclic Redundancy Check: Mistake discovery is the way toward checking information transmission and deciding when blunders have happened. Mistake identification strategies neither right blunders nor distinguish which bits are in mistake – they demonstrate just when a blunder has happened. The motivation behind blunder recognition is not to keep mistakes from happening but rather to keep undetected blunders from happening.

The most widely recognized blunder discovery strategies are repetition checking, which incorporates vertical excess checking, checksum, longitudinal repetition checking, and cyclic repetition checking.

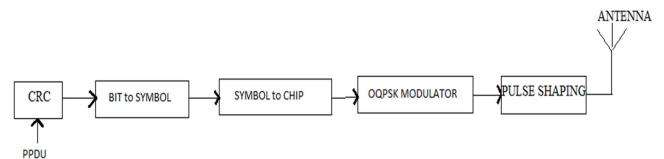

#### B. CRC Polynomial

The most solid excess checking strategy for blunder location is a convolutional coding plan called cyclic repetition checking (CRC)With CRC, roughly 99.999% of all transmission mistakes are distinguished. In CRC-16, 16 bits are utilized for the square check succession. Here, the whole information stream is dealt with as a long persistent paired number. Since the Piece Check Succession (BCS) is separate from the message yet transported inside a similar transmission, CRC is viewed as an efficient code. Cyclic square codes are regularly composed as (n, k) cyclic codes where n = bit length of transmission and k = bit length of message. Consequently, the length of the Piece Check Character (BCC) in bits is

$$BCC = n - k \tag{1}$$

A CRC-16 BCC is the rest of a double division handle. An information message polynomial G(x) is separated by a one of a kind generator polynomial capacity P(x), the remainder is disposed of, and the rest of truncated to 16 bits and affixed to the message as a BCS. The generator polynomial must be a prime number. With CRC era, the division is not refined with standard number-crunching division. Rather, modulo-2 division is utilized, where the rest of got from an elite OR (XOR) operation. In the recipient, the information stream, including the CRC code, is separated by the same creating capacity P(x). In the event that no transmission mistakes have happened, the rest of be zero.

Scientifically, CRC can be communicated as G(x) / P(x) = Q(x) + R(x) Where, G(x) = message polynomial P(x) = generator polynomial Q(x) = remainder R(x) = leftover portion The generator polynomial for CRC-16 is P(x) = x15 + x11 + x4 + x0 International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig. CRC-16 Producing circuit

- A CRC producing circuit requires one move enroll for each piece in the BCC. An audit of CRC creation process is as per the following:

- *1)* Get the crude edge

- 2) Left move the crude edge by n bits and after that partition it by P.

- *3)* The rest of the last activity is the FCS.

- 4) Append the FCS to the crude edge. The outcome is the edge to transmit.

- C. CRC-16 Detects

- 1) Any single-bit errors

- 2) All double-bit errors

- 3) All odd number of bit errors

- 4) All error bursts of 16 bits or less

- 5) 99.9% of error bursts greater than 16 bits long

#### D. Bit-to-Symbol Block

All the 88 bits from the CRC square is embedded into the bit-to-image piece. This parallel data is mapped into the information image. The 4 LSBs (b0, b1, b2, b3) of every octet is mapped into one information image and the 4 MSBs (b4, b5, b6, b7) of every octet is mapped into the following information image. Every octet of PPDU is handled through the bit-to-image square successively, starting with the Introduction field and consummation with the last octet of the PSDU. For the last outcome, 22 images will be the yield of the bit-to-image piece.

# **IV. SIMULATION RESULTS**

From the figure the output data consists of 16 digits represented by "crc16\_o[15:0]". At 510ns, with 25 bits of input data, output CRC code is obtained.

A. Cyclic redundancy check

Fig: CRC waveform

Volume 5 Issue III, March 2017 ISSN: 2321-9653

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

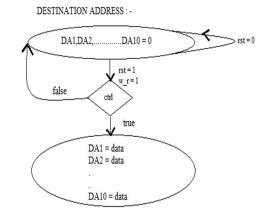

B. Destination Address

www.ijraset.com IC Value: 45.98

| ₽                                              |          |       |       |     |       |         |   |        |      |  | 3,000.000 ns |  |

|------------------------------------------------|----------|-------|-------|-----|-------|---------|---|--------|------|--|--------------|--|

| Name                                           | Value    | 1,500 | ns    |     | 2,000 | ns .    |   | 2,500  | ) ns |  | 3,000 ns     |  |

| Lie Cik                                        | 1        |       |       |     |       |         |   |        |      |  |              |  |

| Rst                                            | 1        |       |       |     |       |         |   |        |      |  |              |  |

| 🕽 🗋 🖌 🖓                                        | 1        |       |       |     |       |         |   |        |      |  |              |  |

| ) 🕨 📑 Ctri[3:0]                                | 0101     |       |       |     |       | 0101    |   |        |      |  |              |  |

| 🕨 🕨 📑 Data[7:0]                                | 10101010 |       |       |     | 1     | 0101010 | ) |        |      |  |              |  |

| 🗗 🕨 📷 DA1[7:0]                                 | 0000000  |       |       |     | 0     | 000000  | ) |        |      |  |              |  |

| 🕨 📑 DA2[7:0]                                   | 0000000  |       |       |     |       | 000000  |   |        |      |  |              |  |

| <ul> <li>DA2[7:0]</li> <li>DA3[7:0]</li> </ul> | 00000000 |       |       |     |       | 000000  |   |        |      |  |              |  |

| ▶ 📷 DA4[7:0]                                   | 00000000 |       |       |     | 0     | 000000  | ) |        |      |  |              |  |

| i 🕨 📑 DA5[7:0]                                 | 00000000 |       |       |     | 0     | 000000  | ) |        |      |  |              |  |

| ▶ 📑 DA6[7:0]                                   | 10101010 |       | 00000 | 000 |       |         |   | 101010 | 10   |  |              |  |

| 📔 🕨 📷 DA7[7:0]                                 | 00000000 |       |       |     | -     | 000000  |   |        |      |  |              |  |

| DA8[7:0]                                       | 00000000 |       |       |     | -     | 000000  |   |        |      |  |              |  |

| DA9[7:0]                                       | 00000000 |       |       |     |       | 000000  |   |        |      |  |              |  |

| ▶ 📑 DA10[7:0]                                  | 00000000 |       |       |     | 0     | 000000  | ) |        |      |  |              |  |

|                                                |          |       |       |     |       |         |   |        |      |  |              |  |

|                                                |          |       |       |     |       |         |   |        |      |  |              |  |

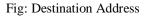

C. Source Address

SOURCE ADDRESS : -

# IC Value: 45.98 International Journal for Research in Applied Science & Engineering Technology (IJRASET)

| Name          | Value    | 11.50 | 0 ns |       |   | 12.00 | )0 ns  |     | E  | 2.50 | 0 ns |   |  | 3,000 ns |

|---------------|----------|-------|------|-------|---|-------|--------|-----|----|------|------|---|--|----------|

| La Cik        | 1        | -/    |      |       |   |       |        |     |    | 1    |      | + |  | -,       |

| Rst           | 1        |       |      |       |   | ÷     |        |     |    |      |      | - |  |          |

| 1 w_R         | 1        |       |      |       |   |       |        |     |    |      |      |   |  |          |

| 🕨 📑 Ctrl[3:0] | 0101     |       |      |       |   |       | 0101   | l   |    |      |      |   |  |          |

| 🕨 📑 Data[7:0] | 10101010 |       |      |       |   |       | 101010 | 010 |    |      |      |   |  |          |

| ▶ 📷 SA1[7:0]  | 00000000 |       |      |       |   |       | 000000 | 000 |    |      |      |   |  |          |

| ▶ 📑 SA2[7:0]  | 00000000 |       |      |       |   |       | 000000 |     |    |      |      |   |  |          |

| SA3[7:0]      | 00000000 |       |      |       |   |       | 000000 |     |    |      |      |   |  |          |

| SA4[7:0]      | 00000000 |       |      |       |   |       | 000000 |     |    |      |      |   |  |          |

| SA5[7:0]      | 00000000 |       |      |       |   |       | 000000 | 000 |    |      |      |   |  |          |

| SA6[7:0]      | 10101010 |       | 000  | 00000 | ) |       | X      |     | 10 | 1010 | 010  |   |  |          |

| ▶ 📷 SA7[7:0]  | 00000000 |       |      |       |   |       | 000000 |     |    |      |      |   |  |          |

| SA8[7:0]      | 00000000 |       |      |       |   |       | 000000 |     |    |      |      |   |  |          |

| ▶ 📷 SA9[7:0]  | 00000000 |       |      |       |   |       | 000000 |     |    |      |      |   |  |          |

| SA10[7:0]     | 00000000 | <br>- |      |       |   |       | 000000 | 000 |    |      |      |   |  |          |

|               |          |       |      |       |   |       |        |     |    |      |      |   |  |          |

Fig: Source Address waveform

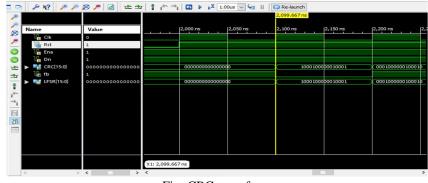

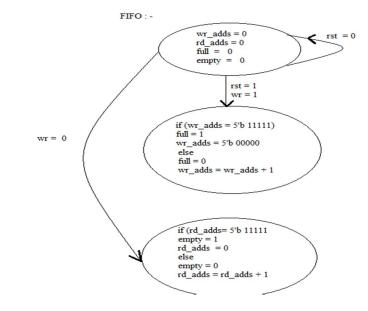

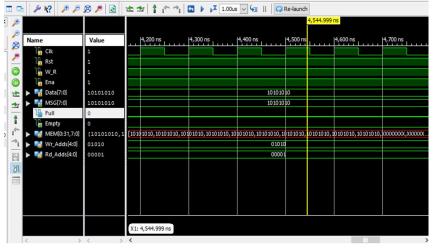

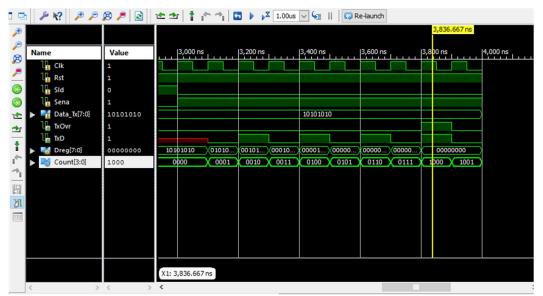

# D. FIFO

www.ijraset.com

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

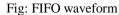

# E. Serializer

Fig: Serializer waveform

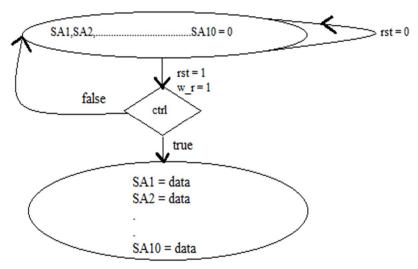

# F. Output Waveform

| 🖉 🎤 🌾 🥕 🌶     | ° 🥦 🏓 🔳 🛛 | ** ** | "i   🖬 🕨 📭 [ | 1.00us 🗸 😼 🗍 | Re-launch  |        |        |

|---------------|-----------|-------|--------------|--------------|------------|--------|--------|

|               |           |       |              |              | 150.500 ns |        |        |

| Name          | Value     | 0 ns  | 50 ns        | 100 ns       | 150 ns     | 200 ns | 250 ns |

| 🖓 TxD         | 0         |       |              |              |            |        |        |

| TxOvr         | 0         |       |              |              |            |        |        |

| 🔚 Cik         | 0         |       |              |              |            |        |        |

| 🐻 Rst         | 1         |       |              |              |            |        |        |

| 16 W_R        | 1         |       |              |              |            |        |        |

| ា🖗 sid        | 0         |       |              |              |            |        |        |

| 🔚 Sena        | 1         |       |              |              |            |        |        |

| 🔚 CntEna      | 1         |       |              |              |            |        |        |

| 🔚 Ena         | 1         | L     |              |              |            |        |        |

| ▶ 📷 Sel[5:0]  | 000000    |       |              |              | 00000      |        |        |

| 🕨 📷 Data[7:0] | 10101111  | (     |              | 10           | 0101111    |        |        |

|               |           |       |              |              |            |        |        |

|               |           |       |              |              |            |        |        |

|               |           |       |              |              |            |        |        |

|               |           |       |              |              |            |        |        |

|               |           |       |              |              |            |        |        |

www.ijraset.com IC Value: 45.98 Volume 5 Issue III, March 2017 ISSN: 2321-9653

# International Journal for Research in Applied Science & Engineering Technology (IJRASET)

# CONCLUSION

V.

This paper demonstrates the Verilog based plan of computerized transmitter for 2.4GHz band Zigbee applications. The conduct of CRC and Bit-to-image were described utilizing Verilog and utilizing VHDL. From the exchange, up until this point, some portion of the Zigbee transmitter is distant from everyone else is portrayed and integrated. Both the outcomes and combination report were looked at and dialog has made for the plan procedure. Hence, utilizing Verilog, Number of possessed

cuts required is 8 out of 4656 and utilizing VHDL it is 15 out of 4656. The rest of the piece of the transmitter will be planned and incorporated in future. The Bit-to-Image yield must be confirmed with a specific end goal to encourage the following piece. Generally this piece has been integrated and number of cuts to be used has. To study and plan Image to-Chip Mapper. This part must be outlined with the help if Coordinate Arrangement Spread Range Strategy. To study and configuration Counterbalance Quadrature Stage Move Keying (O-QPSK) adjustment system. This adjustment strategy alone is appropriate for 2.4GHz band of Zigbee transmitter. To study and configuration Heartbeat forming hinder for tweaked yield, which will diminish the Bury Image Obstruction (ISI).

#### REFERENCES

- [1] Khalifa. O, Islam. MDR and Khan. S, "Cyclic redundancy encoder for error detection in communication channels", RF and Microwave Conference, 2004.

- [2] Matloff .N, "Cyclic redundancy checking", Department of Computer Science, University of California, 2001.

- [3] Rahmani.E, "Zigbee/IEEE 802.15.4", University of Tehran, 2005.

- Shuaib.K, Alnuaimi.M, Boulmalf.M, Jawhar.I, Sallabi.F and Lakas.A, "Performance evaluation of IEEE 802.15.4: Experimental and simulation results", Journal of Communications, 2, 4(2007): 29-37.

- [5] Ting Ting Meng, Chen Zhang, Peter Athanas, "An FPGA- Based Zigbee Receiver on the Harris Software Defined Radio SIP", SDR Forum Technical Conference, Denver, Colorado, 2007.

- [6] Wayne Tomasi, "Advanced Electronic Communication System", 6<sup>th</sup> Edition, Pearson Education.

- [7] Zigbee Alliance, available at: www.zigbee.org.

Prof.Y.R.K.Paramahamsa, B. E, S. V. H. College of Engineering , Machilipatnam

M. Tech Jawaharlal Nehru Technological University Ananthapuramu.

Shaik.Usman Basha, pursuing B.TECH In Brindavan Institute of Technology and Science, Kurnool.

Shaik . Mallika, pursuing B.TECH in Brindavan Institute of Technology and Science, Kurnool.

# www.ijraset.com Volume 5 Issue III, March 2017 IC Value: 45.98 International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Syed . Naveed, pursuing B.TECH in

N. Ambika, pursuing B.TECH in Brindavan Institute of Technology and Science, Kurnool.

Brindavan Institute of Technology and Science, Kurnool.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)