IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: III Month of publication: March 2017 DOI: http://doi.org/10.22214/ijraset.2017.3186

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

www.ijraset.com IC Value: 45.98 Volume 5 Issue III, March 2017 ISSN: 2321-9653

## International Journal for Research in Applied Science & Engineering Technology (IJRASET) Information Exchange between Different Protocols

Y. R. K. Paramahamsa<sup>1</sup>, G. Manaswini<sup>2</sup>, M. Sharath<sup>3</sup>, B. Vijay<sup>4</sup>, K. S. Prakash<sup>5</sup> <sup>1,2,3,4,5</sup>Bits-Kurnool

Abstract: All outline units comprise of littler utilitarian pieces called subsystem or module. For successful working of the framework these modules should be in a state of harmony with each other and share assets. Issue begins when one module takes after various conventions as others and every module has its diverse piece rate or baud rate of information exchange which can be either offbeat or synchronous. The paper takes a case of I2C convention and AMBA APB convention to portray the design which characterizes how information are exchanged starting with one convention then onto the next. It exploits the adaptable conventions of I2C to make it good with APB convention. The proposed design is an extension between I2C Master and APB Salve. The information goes from a serial transport (I2C) to parallel transport (APB) to serial (I2C) in a state of harmony with the separate space clock. This structures a bidirectional interface between I2C bolstered module and APB upheld module.

#### I. INTRODUCTION

I2C is a 2-wire, serial device with SDA and SCL, transport created with the essential thought of interfacing distinctive ICs and application particular modules with processors on a typical correspondence net-work. I2C is a multi-ace transport and the fringe gadgets are tended to by remarkable programmable address. By inspecting the SDA above Nyquist rate I2C can speak with any de-bad habit. Then again APB is a low data transfer capacity transport with re-duced interface many-sided quality. APB has devoted programmable control registers to get to peripherals gadgets. Like I2C, APB good gadgets are effortlessly fused in any outline stream.

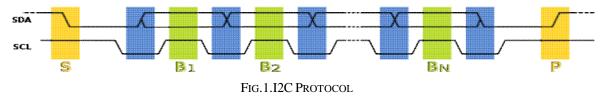

#### A. I2C Protocol

I2C is a serial convention for two-wire interface to associate low-speed gadgets like microcontrollers, EEPROMs, A/D and D/A converters, I/O interfaces and other comparative peripherals in installed frameworks. It was developed by Philips and now it is utilized by all significant IC makers. Each I2C slave gadget needs an address. I2C transport is prevalent on the grounds that it is easy to use, there can be more than one ace, just upper transport speed is characterized and just two wires with draw up resistors are expected to interface practically boundless number of I2C gadgets. I2C can utilize considerably slower microcontrollers with universally useful I/O pins since they just need to create redress Start and Stop conditions notwithstanding capacities for perusing and composing a byte.

Each slave gadget has a special address. Exchange from and to ace gadget is serial and it is part into 8-bit bundles. All these basic prerequisites make it exceptionally easy to actualize I2C interface even with shoddy microcontrollers that have no extraordinary I2C equipment controller. You just need 2 free I/O pins and couple of basic i2C schedules to send and get orders.

The underlying I2C details characterized most extreme clock recurrence of 100 kHz. This was later expanded to 400 kHz as Fast mode. There is likewise a High speed mode which can go up to 3.4 MHz and there is additionally a 5 MHz ultra-quick mode.

In typical state both lines (SCL and SDA) are high. The correspondence is started by the ace gadget. It produces the Start condition (S) trailed by the address of the slave gadget (B1). On the off chance that the bit 0 of the deliver byte was set to 0 the ace gadget will keep in touch with the slave gadget (B2). Something else, the following byte will be perused from the slave gadget. When all bytes are perused or composed (Bn) the ace gadget creates Stop condition (P). This signs to different gadgets on the transport that the correspondence has finished and another gadget may utilize the transport. Most I2C gadgets bolster rehashed begin condition. This implies before the correspondence closes with a stop condition, ace gadget can rehash begin condition with address byte and change the mode from writing to perusing.

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

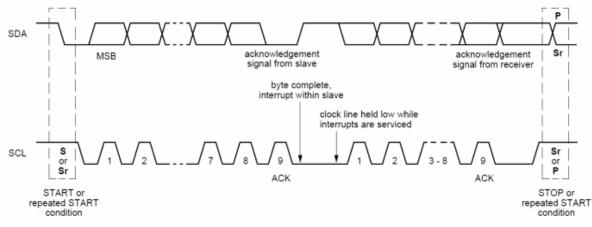

#### B. I2C Data Transfer

Information on the I2C transport is moved in 8-bit parcels (bytes). There is no impediment on the quantity of bytes, be that as it may, every byte must be trailed by an Acknowledge bit. This bit signals whether the gadget is prepared to continue with the following byte. For all information bits including the Acknowledge bit, the ace must create clock beats. On the off chance that the slave gadget does not recognizes exchange this implies there is no more information or the gadget is not prepared for the exchange yet. The ace gadget should either produce Stop or Repeated Start condition.

FIG.2. I2C DATA TRANSFER

#### II. APB PROTOCOL

The Advanced peripheral bus(APB) is a piece of the Advanced Microcontroller Bus Architecture(AMBA) convention family used to convert serial data to parallel data. It characterizes an ease interface that is advanced for insignificant power utilization and lessened interface many-sided quality. The APB convention is not pipelined, utilize it to interface with low-data transfer capacity peripherals that don't require the elite of the AXI convention. The APB convention relates a flag move to the rising edge of the clock, to rearrange the reconciliation of APB peripherals into any outline stream. Each exchange takes no less than two cycles.

- A. The APB can Interface with

- 1) MBA Advanced High-performance Bus (AHB)

- 2) AMBA Advanced High-performance Bus Lite (AHB-Lite)

- 3) AMBA Advanced Extensible Interface (AXI)

- 4) AMBA Advanced Extensible Interface Lite (AXI4-Lite)

You can use it to access the programmable control registers of peripheral devices.

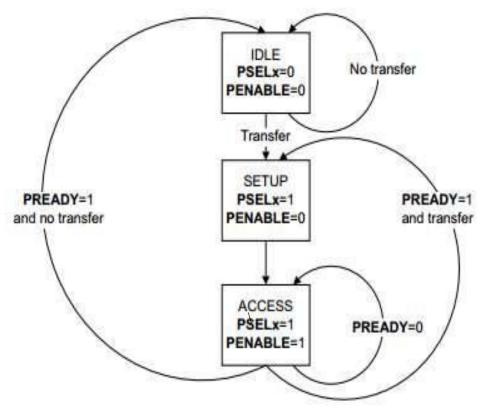

#### B. APB Working States

The state machine works through the going with states:

- 1) Idle: This is the default state of the APB.

- 2) Set Up: When a trade is required the transport moves into the SETUP state, where the best possible select banner, PSELx, is pronounced. The transport just remains in the SETUP state for one clock cycle and reliably moves to the Get to state on the taking after rising edge of the clock.

- *3) Get to:* The enable banner, PENABLE, is confirmed in the Get to state. The address, create, and select banners all remain stable in the midst of the move from the SETUP to Get to state.

- 4) *Pready:* The PREADY movement from the slave controls the exit from the Get to state.

If PREADY is held LOW by the slave then the periphery transport remains in the Get to state.

If PREADY is driven HIGH by the slave then the Get to state is left and the vehicle returns to the Sit still state more trades are required. Of course, the vehicle moves direct to the SETUP state if another trade a great many.

www.ijraset.com IC Value: 45.98 Volume 5 Issue III, March 2017 ISSN: 2321-9653

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig 3: APB operating states

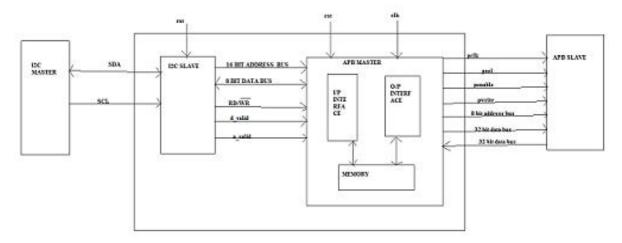

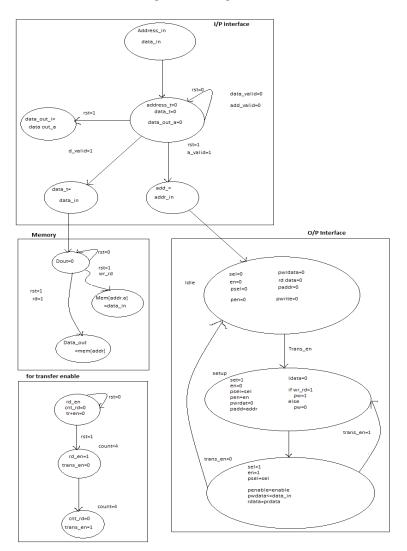

#### C. Block Diagram

The correspondence connect amongst I2C and APB is appeared in beneath figure. This design contains I2C slave and APB ace. As we realize that, the ace starts the information exchange, the I2C ace sends the information to I2C slave and from slave it is exchanged to APB ace. From APB ace the information sends to APB slave. The I2C ace needs to speak with APB slave by means of I2C slave as it were.

The information exchange is looked at by APB ace and it is exchanged to APB slave.

The information and address substantial signs are given by I2C slave flag.

To peruse information, correspondence is done by means of APB ace to I2C slave to I2C ace.

An affirmation is sent to APB ace for APB slave to peruse the information signals.

#### D. Write Operation

- 1) Whenever I2C Master needs to speak with APB Slave it would be done by means of I2C Slave.

- 2) I2C Slave will attest Data Valid and Address Valid signs.

- 3) Seeing these flag high, outlined APB Master surveys the memory for its accessibility and begins APB compose state machine.

- 4) I2C sends four lumps of 8-bit information serially to be composed on APB Memory at four back to back advertisement dresses.

- 5) After exchange of every byte APB Master keeps a mind check whether each of the four memory areas are refreshed effectively.

- 6) As soon as the information at APB Master is refreshed it exchanges the same 32-bit information to APB Slave.

- E. Read Operation

- 1) Here again when I2C need to peruse information from the APB Slave, correspondence will occur by means of APB Master to I2C Salve to I2C ace.

- 2) APB Salve will send a flag to APB Master advising that the information are accessible to be perused.

- 3) APB Salve then transmit the information to APB Master where it is put away in the interior memory to be gotten by I2C Slave

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

at time purpose of time.

Fig.4.BlockDiagram

Volume 5 Issue III, March 2017 ISSN: 2321-9653

**International Journal for Research in Applied Science & Engineering**

| Name              | Value                                   |         | 1,045 us      | 1,050 us                                | 1,055 us  | 1,060 us                                | 1,065 us     | 1,070 us              | 1,075 us |

|-------------------|-----------------------------------------|---------|---------------|-----------------------------------------|-----------|-----------------------------------------|--------------|-----------------------|----------|

| ▶ 📲 data_out[7:0] | 0000000                                 |         |               |                                         |           | 0000000                                 |              |                       |          |

| 🕼 pclk            | 0                                       |         |               |                                         |           |                                         |              |                       |          |

| De psel           | 1                                       |         |               |                                         |           |                                         |              |                       |          |

| 1 penable         | 1                                       |         |               |                                         |           |                                         |              |                       |          |

| 1 pwrite          | 1                                       |         |               |                                         |           |                                         |              |                       |          |

| 🕨 🛃 paddr[31:0]   | 000000000000000000000000000000000000000 | 0000000 | 00000000000 X |                                         | 00        | 000000000000000000000000000000000000000 | 000001001011 |                       |          |

| 🕨 橘 pwdata[31:0]  | 000011000000110                         |         | 000000        | 000000000000000000000000000000000000000 | 000000000 | X                                       | 000011000000 | 1 1000000 1 1000000 1 | 100      |

| 🔚 cik             | 0                                       |         |               |                                         |           |                                         |              |                       |          |

| 🚡 Reset           | 1                                       |         |               |                                         |           | -                                       |              |                       |          |

| 🕨 🃷 DataIn[7:0]   | 00001100                                |         |               |                                         |           | 00001100                                |              |                       |          |

| 🕨 📷 Address[3:0]  | 1000                                    |         |               | 1.1                                     |           | 1000                                    |              | 1.                    |          |

| 1 ChipSelect      | 1                                       | 0       |               |                                         |           |                                         |              |                       |          |

| 🐻 ReadWrite       | 0                                       | ~       |               | 19-                                     |           |                                         |              |                       |          |

| 🕨 📷 prdata[31:0]  | 000000000000000000000000000000000000000 |         |               |                                         | 0000      | 000000000000000000000000000000000000000 | 000000000    |                       |          |

|                   |                                         |         |               |                                         |           |                                         |              |                       |          |

Fig.6 simulation results of communication bridge

Fig.6.1 Top view

#### IV. CONCLUSION

The implemented communication bridge between I2C and APB was designed and implemented in Xilinx ISE 13.4, Isim, using Verilog HDL. This project demonstrates how I2C Master Controller (Master) transmits and receives data to and from the (Slave). So that any low speed peripheral devices can be interfaced using I2C bus protocol as master. In future, this can be implemented as real time clock in networks that contains multiple masters and multiple slaves to co-ordinate the entire system by clock synchronization techniques. Simulation results are verified and data transfer from I2C master to APB slave can be clearly seen in provided simulation results.

#### REFERENCES

- Enhanced Universal Serial Communication Interface (eUSCI) I2C Mode, SLAU425B-August 2012– Revised February 2013, Texas Instruments Incorporated.

- [2] M. Alassir, J. Denoulet, O. Romain & P. Garda "A SystemC AMS Model of an I2C Bus Controller", IEEE.

- [3] J. J Patel, B.H. Soni, "Design and Implementation of I2C Bus Controller Using Verilog" ISSN: 0975 6779 NOV 12 TO OCT 13 | VOLUME 02, ISSUE 02

- [4] Samir Palnitkar, Verilog HDL, second Edition. \

- [5] UM10204, I2C-bus specification and user manual, Rev. 4—13 February 2012, NXP Semiconductors. \

- [6] AMBA® APB Protocol Specification, Version: 2.0, 13 April 2010, issue C, http://www.arm.com.

#### www.ijraset.com IC Value: 45.98

Volume 5 Issue III, March 2017 ISSN: 2321-9653

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

- [7] D.B.Rane, Ahmed Mustafa M. I. Shaikh, Devanand Mahajan, Mehdi Ali, "Priority Based I2C Bus Controller" (IJCTEE) Volume 3, Special Issue, March-April 2013.

- [8] Bacciarelli, L. Lucia, G. ; Saponara, S. ; Fanucci, L. ; Forliti, M., "Design, testing and prototyping of a software programmable I2C/SPI IP on AMBA bus", IEEE Research in Microelectronics and Electronics 2006, Ph. D.

Mr. Y. Rama Krishna ParamahamsaProfessor in Department of ECE of BITS-KNLM. Tech : Jawaharlal Nehru Technologicai University(Ananthapuram) ,B. E : S.V.H college of Engineering, Machilipatnam .

Miss. G.Manaswini is pursuing her B.Tech in Department of ECE of BITS-KNL

Mr. M.Sharath Kumar Reddy is pursuing his B.Tech in Department of ECE of BITS-KNL

Mr. B. Vijay Shekar Reddy is pursuing his B. Tech in Depa

Mr. K.S.Prakash Kumar Reddy is pursuing his B.Tech in Department of ECE of BITS-KNL

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)