# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: IV Month of publication: April 2017

DOI: http://doi.org/10.22214/ijraset.2017.4241

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

# A Comparative Performance Analysis of Various CMOS Design Techniques for XOR and XNOR Circuits

Aditi Joshi <sup>1</sup>, Chanchal Jain <sup>2</sup>, Pooja Choudhary<sup>3</sup>, Chirag Arora<sup>4</sup>, Krishan Rapswal <sup>5</sup>

<sup>1,2,4,5</sup>Deptt. of Electronics and Comm. Engg., SKIT, M&G, Jaipur, (RAJ.) INDIA

<sup>3</sup>Asst. Prof., Deptt. of Electronics and Comm. Engg., SKIT, M&G, Jaipur, (RAJ.) INDIA

Abstract: XOR and XNOR gates play an important role in digital systems. XOR & XNOR logic gates are basic building blocks of many arithmetic circuits. The XOR and XNOR circuit is implemented in pass transistor logic, static CMOS logic, transmission gate logic. The design of the XOR & XNOR circuits based on TSMC 32nm process models at the supply voltage 0.9V is simulated using HSPICE. Due to low power consumption and high speed these design circuits are suitable for arithmetic operations and VLSI applications. Hence comparison of delay & power is obtained in this paper for various design techniques of logic gates.

Keywords: HSPICE, Low power, pass transistor logic, transmission gate, Exclusive-OR, Exclusive-NOR

#### I. INTRODUCTION

To design integrated circuits with high operating frequency the major issues are power, delay and smaller silicon area with higher speed. The XOR and XNOR circuits influence the performance of the complex logic circuits. The key parameter for today's electronic industry is low power. In order to make a device more reliable and efficient, power consumption should be reduced. As the demand of portable consumer electronics increases, and the size of the chip decreases, challenges towards the power dissipated are induced [1-3].

In CMOS circuit, the power consumption for any given function must be reduced for two different reasons: the first reason is to reduce heat dissipation in order to allow a large density of functions to be incorporated on an IC chip. Any amount of power consumption is fruitful as long as it doesn't degrade overall circuit performance [4]. The second reason is to save energy in battery operated instruments. By choosing proper design style the power saving capability in circuits can increase at the design level. Without low-power design techniques such applications generally suffer from very short battery life, while packaging and cooling them would be very difficult. This is leading to an unavoidable increase in the cost of the product.

#### A. Static CMOS Logic

It is the most commonly used logic design technique. This circuit is made up of two networks namely pull up network (PUN) and pull down network (PDN). PUN and PDN comprises of PMOS transistors and NMOS transistors respectively. Input to these networks is dual of each other [5]. Output is based on the inputs applied to PUN and PDN making the output 1 or 0 respectively. This design technique is mostly used and produces results that are widely accepted but it requires more number of CMOS.

#### B. Pass Transistor Logic

The static Gate with low-impedance path exists. In this logic design, the reduction in output voltage swing is useful for power consumption as well as for slow switching. Less number of transistors are difficulty to design [7].

#### C. Transmission Gate Logic

Transmission gate CMOS (TG) uses complex logic functions by using complementary transistors. PMOS and NMOS are in parallel and are controlled by complementary signals. Both transistors are ON or OFF simultaneously [8].

The NMOS switch passes a good zero but a poor 1.

The PMOS switch passes a good one but a poor 0.

Combining them we get a good 0 and a good 1 passed in both directions.

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

#### II. CIRCUIT DESIGN

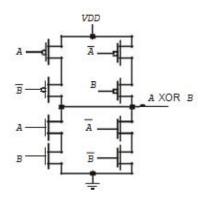

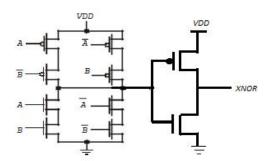

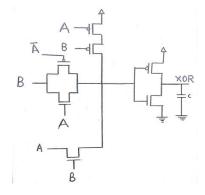

#### A. Static CMOS XOR and XNOR Circuit

Complementary CMOS uses dual networks to implement a given function [9-11]. A first part consists solely of complementary pull-up (PMOS) network while a second part consists of pull-down (NMOS) networks. This technique is popular and produces results that are widely accepted but it requires more numbers of CMOS transistors. Static CMOS XOR and XNOR gate is shown in Fig.2.1(a) and Fig.2.1(b). The circuit operates with full output voltage swing.

$$Z = A \bigoplus B = (A + B). (A' + B')$$

$Z' = (A \bigoplus B)' = \{(A + B). (A' + B')\}'$

$Z' = AB + A'B'$

$Z = (AB + A'B')' = A \bigoplus B$

Fig.2.1 (a) Static CMOS XOR circuit.

Fig.2.1 (b) Static CMOS XNOR Circuit

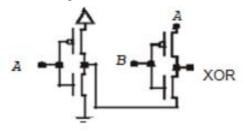

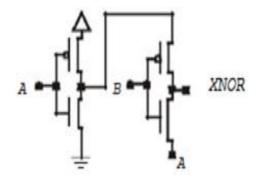

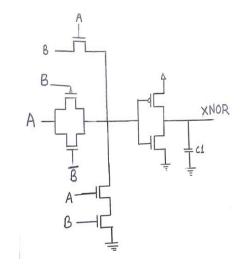

#### B. PTL based XOR and XNOR Circuits

When the input B is at logic 1, the PMOS pass transistor is OFF and NMOS pass transistor is ON. Therefore the XOR output of the circuit in Fig.2.2(a) is the complement of input A and XNOR output in Fig.2.2(b) gets the same logic value as input A. When the input B is at logic 0, the XNOR output of the circuit in Fig.2.2(b) is the complement of input A and XOR output in Fig.2.2(a) gets the same logic value as input A for the reason that PMOS pass transistor is ON and NMOS pass transistor is OFF.

Fig.2.2 (a) Pass Transistor XOR Circuit

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig.2.2 (b) Pass Transistor XNOR Circuit

#### C. Transmission Gate based XOR and XNOR Circuits

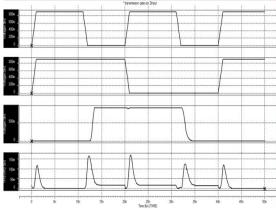

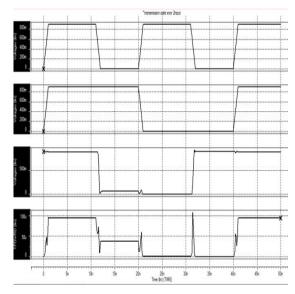

It solves the problem of low logic level swing by using PMOS as well as NMOS. The circuits for XOR-XNOR function is shown in Fig. 2.3(a) alleviate the problems of threshold voltage loss and non-zero standby power dissipation. By cascading a standard inverter after the XOR circuit, a high performance XNOR, as shown in Fig. 2.3(b) will have a restored output. The same property is present in the XOR structure. These circuits provide a full voltage swing (i.e., 0V for logic 0 and 1.8V for logic 1) [12-13].

Fig.2.3 (a) Transmission Gate XOR Circuit

Fig.2.3 (b) Transmission Gate XNOR Circuit

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

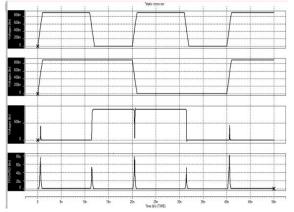

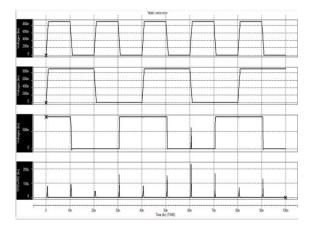

#### III. SIMULATION RESULTS

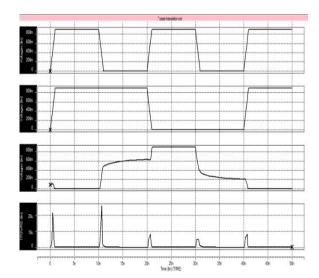

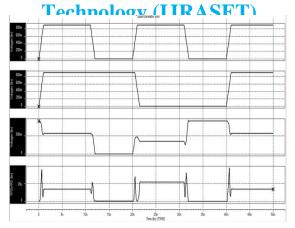

The transient and DC analysis of the circuits were performed on HSPICE at a supply voltage ranging 0.9V using TSMC 32nm CMOS process. The simulation results of various XOR and XNOR designs are shown in Fig.3.1-3.6.

Fig.3.1 Static CMOS XOR Waveform

Fig.3.2 Static CMOS XNOR Waveform

Fig.3.3 Pass Transistor XOR Waveform

Volume 5 Issue IV, April 2017 ISSN: 2321-9653

www.ijraset.comVolume 3IC Value: 45.98ISSN: 23

#### **International Journal for Research in Applied Science & Engineering**

Fig.3.4 Pass Transistor XNOR Waveform

Fig.3.5 Transmission gate XOR Waveform

Fig.3.6 Transmission gate XNOR Waveform

#### IV.COMPARISON

The comparative performance for all design techniques described in this paper using XOR and XNOR circuit at VDD = 0.9V are respectively shown in Table 1 and Table 2.

Volume 5 Issue IV, April 2017 www.ijraset.com IC Value: 45.98 ISSN: 2321-9653

### **International Journal for Research in Applied Science & Engineering** Technology (IJRASET) TABLE I

Comparative performance of transient analysis of XOR circuits with different design techniques at Vdd = 0.9V

| Parameter<br>XOR        | Static<br>CMOS<br>Logic | Pass<br>Transistor<br>Logic | Transmission<br>Gate<br>Logic |

|-------------------------|-------------------------|-----------------------------|-------------------------------|

| Number of<br>Transistor | 12                      | 4                           | 2                             |

| tplh                    | 9.0851E-<br>09          | 3.0510E-<br>10              | 5.2327E-11                    |

| tphl                    | 1.3190E-<br>11          | 1.6685E-<br>10              | 2.0933E-11                    |

| Delay                   | 4.5491E-<br>09          | 2.3598E-<br>10              | 3.6630E-11                    |

| Average<br>Power        | 1.9658E-<br>06          | 7.9505E-<br>07              | 9.8448E-05                    |

| Maximum<br>Power        | 7.8521E-<br>05          | 2.6015E-<br>05              | 1.6720E-04                    |

| PDP                     | 8.9426E-<br>15          | 1.8761E-<br>16              | 1.3417E-15                    |

TABLE II Comparative performance of transient analysis of XNOR circuits with different design techniques at Vdd = 0.9V

| Parameter<br>XNOR       | Static CMOS<br>Logic | Pass<br>Transistor<br>Logic | Transmission Gate Logic |

|-------------------------|----------------------|-----------------------------|-------------------------|

| Number of<br>Transistor | 14                   | 4                           | 11                      |

| tplh                    | 6.6263E-11           | 2.3065E-11                  | 3.2094E-11              |

| tphl                    | 6.1547E-11           | 7.9278E-11                  | 1.6440E-10              |

| Delay                   | 6.3905E-11           | 5.1171E-11                  | 9.8248E-11              |

| Average<br>Power        | 2.6255E-06           | 9.8413E-06                  | 3.4730E-05              |

| Maximum<br>Power        | 1.5933E-04           | 3.5464E-05                  | 1.0833E-04              |

| PDP                     | 1.6778E-16           | 5.0358E-16                  | 3.1421E-15              |

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

#### V. CONCLUSION

In this paper, we have studied various design techniques for XOR-XNOR circuits. The mentioned design techniques are compared based on area, delay, power consumption, and PDP. The performances of these techniques have been evaluated by HSPICE using a TSMC 32nm CMOS technology. These design techniques are suitable for arithmetic circuits and other VLSI applications with very low power consumption and a very high speed performance. Based on the simulation results, it has been culminated that in the PTL based XOR and XNOR design the output high (or low) voltage is deviated from the VDD (or ground) by a multiple of threshold voltage. The XOR-XNOR circuits using transmission gate improve the threshold voltage loss problem while XOR and XNOR circuits with feedback transistors have good output signal levels, consume less power and have high speed compared to the previous designs at low supply voltage.

#### VI. ACKNOWLEDGMENT

This work has been done in Project lab, Electronics & Communication Department. The authors would like to thank Director (Academics) and the Management of SKIT, Jaipur for permission to carry out this work.

#### REFERENCES

- [1] N. Weste, K. Eshranghian, Principles of CMOS VLSI Design: A System Perspective, Reading MA: Addison-Wesley, (1993).

- [2] Sung-Mo Kang, Y. Leblibici, CMOS Digital Integrated Circuits: Analysis and Design, Addition-Tata McGraw Hill, (2003).

- [3] J.Rabaey, Digital Integrated Circuits (A Design Prospective), Prentice-Hall, Englewood Cliffs, NJ, (1996).

- [4] Sung-Chuan Fang, Jyh-Ming Wang, Wu-Shiung Feng, A New Direct design for three-input XOR function on the transistor level, IEEE Trans. Circuits Syst. I: Fundamental theory and Applications, 43(4): (1996).

- [5] K.H. Cheng and C.S. Huang, The novel efficient design of XOR/XNOR function for adder applications, in Proc. IEEE Int. Conf. Elect., Circuits Syst., 1: 29-32(1999).

- [6] M. Vesterbacka, A New six-transistor CMOS XOR Circuits with complementary output, to appear in Proc. 42nd Midwest Symp. On Circuits and Systems, Las Cruces, NM, Aug., 8-11(1999).

- [7] R. Zimmermann, W. Fichtner, Low-power logic styles: CMOS versus pass-transistor logic, IEEE J. Solid-State Circuits, 32(7): 1079-1090(1997).

- [8] D. Radhakrishanan, S.R. Whitaker, G.K. Maki, Formal design procedures for pass-transistor switching circuits, IEEE J. Solid-State Circuits, 20(3): 531-536(1985).

- [9] C. Pedron, A. Stauffer, Analysis and synthesis of combinational pass transistor switching circuits, IEEE Trans. Computer-Aided Design Integer. Circuit Syst., 7(7):775-786(1988).

- [10] H. Lee and G. E. Sobelman, New low-voltage circuits for XOR and XNOR, in Proc. IEEE Southeastcon, Apr. 12-14, pp. 225-229(1997).

- [11] A.M. Shams, T.K. Darwish, M.A. Bayoumi, Performance analysis of low-power 1-bit CMOS full adder cells, IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 10(1): 20-29(2002).

- [12] H. Lee and G.E. Sobelman, New XOR/XNOR and Full adder circuits for low voltage, low power application, Microelectronics Journal 29: 509-517(1998).

- [13] Sumeer Goel, Mohammed A Elgamel and MA Bayoumi, Design Methodologies for High-Performance Noise-Tolerant XOR-XNOR Circuits, IEEE Trans. Circuits Syst.I., 53(4): (2006).

10.22214/IJRASET

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)