IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: V Month of publication: May 2017 DOI:

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

# Power Factor Corrected Zeta Converter Based SMPS with High Frequency Isolation

Rajeev K R<sup>1</sup>, Dr. Bos Mathew Jos<sup>2</sup>, Prof. Acy M Kottalil<sup>3</sup>

<sup>1,2,3</sup>Dept. of Electrical and Electronic Engineering, Mar Athanasius College of Engineering, Kothamangalam, Kerala, India

Abstract: T Multiple output Switched Mode Power Supplies (SMPSs) for personal computers (PCs) and other equipments are normally depict extremely bad power quality indices at the utility interface such as total harmonic distortion of the input current being more than 80%, power factor being lower than 0.5 and output voltage regulation being very poor. So, they violate the limits of harmonic emissions set by international power quality standards. This work presents power quality improvement in a multiple output SMPS that yields regulated dc output voltages irrespective of line and load variations. Here a Zeta PFC converter is used for the development of computer SMPSs that are capable of drawing a purely sinusoidal current with unity PF, offering low rippled output which is the prime requirement of PCs. In this work, the Continuous Conduction Mode (CCM) of the Zeta converter have been analyzed and compared to select the best operating mode for a computer power supply application. The simulations of the circuit were done in PSIM and experimental results are also verified. Keywords: SMPS, Zeta, CCM, PF, THD.

#### I. INTRODUCTION

Switched Mode Power Supply (SMPS) is an integral part of the computer that converts ac to multiple numbers of suitable dc voltages to impart power to different parts of the PC. It contains a diode bridge rectifier (DBR) with a capacitor filter followed by an isolated dc-dc converter to achieve multiple dc output voltages of different ratings. The uncontrolled charging and discharging of the capacitor result in a highly distorted, high crest factor, periodically dense input current at the single phase ac mains; this violates the limits of international power quality (PQ) standards such as IEC 61000- 3-2. Further, the neutral current in the distribution system increases if these PCs are used in large numbers which creates serious problems like overloading the neutral conductor, noise, derating of the transformer, voltage distortion etc.

A switched-mode power supply (switching-mode power supply, switch-mode power supply, switched power supply, SMPS, or switcher) is an electronic power supply that incorporates a switching regulator to convert electrical power efficiently. Like other power supplies, an SMPS transfers power from a DC or AC source (often mains power), to DC loads, such as a personal computer, while converting voltage and current characteristics. Unlike a linear power supply, the pass transistor of a switching-mode supply continually switches between low-dissipation, full-on and full off states, and spends very little time in the high dissipation transitions, which minimizes wasted energy. Ideally, a switched-mode power supply regulates the output voltage by continually dissipating power in the pass transistor. This higher power conversion efficiency is an important advantage of a switched-mode power supply. Switched-mode power supply. Switched-mode power supply also be substantially smaller and lighter than a linear supply due to the smaller transformer size and weight.

AC-DC converter with high frequency transformer is most widely used in switched mode power supply (SMPS), battery charging, uninterrupted power supply (UPS), electronic ballast, induction heater. SMPS works like a DC chopper by operating the on/off switch rapidly, AC ripple frequency rises which can be easily filtered by L and C filter circuits which are small in size and less in weight. It may therefore be inferred that is the requirement of small physical size and weight that has led to the wide spread use of SMPSs. If the switching devices are power transistor, the chopping

frequency limited to 40 kHz. For power MOSFETs the chopping frequency is of the order of 200KHz as a result size of the filter circuit and transformer decreases leading to considerable savings. as such high frequency, ferrite core is used in transformers. The overall size of SMPS it depend on operating frequency. Use of power transistor is limited to approximately 40-50 kHz. Above this operating frequency, power MOSFET is used upto above 200 kHz.

#### A. Zeta Converter based SMPS

A boost converter is a common choice as a PFC in various industrial applications. However, it cannot be used if a wide range of ac

www.ijraset.com IC Value: 45.98 *Volume 5 Issue V, May 2017 ISSN: 2321-9653*

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

mains voltage is to be taken care of. Similarly, due to limited output voltage range buck converters are not preferred for computer power supply. Non-isolated buck boost PFC converter configurations are the best suited for maintaining a constant dc output voltage irrespective of wide variations in ac supply voltages. Different buck-boost converters configurations and their application to SMPS are reported in the literature. A conventional buck-boost converter Power Factor Corrected Zeta Converter Based Improved Power Quality Switched Mode Power Supply has a low component count. The buck-boost Cuk converter is not preferred due to the polarity of the output being reversed which gives rise to various design issues. SEPIC also depicts a pulsating output current. As the output stage of the power supply is very sensitive, this pulsating current is not desirable. The flyback converter suffers from leakage inductance problem which imposes a limit on its rating. To eliminate these issues, a Zeta PFC converter is employed as a PFC converter in many research papers. It provides a continuous output current with a low ripple output voltage along with a high level performance which is highly recommendable for PCs.

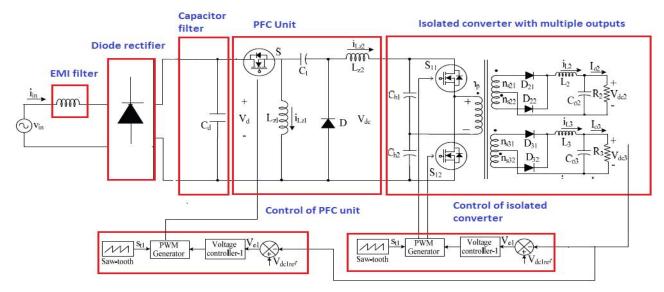

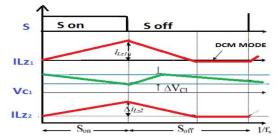

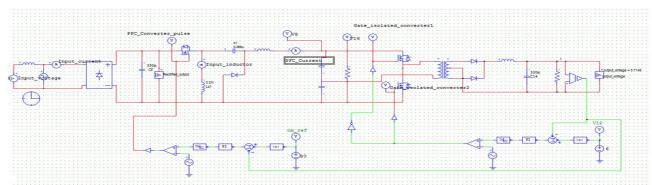

SEPIC also depicts a pulsating output current. As the output stage of the power supply is very sensitive, this pulsating current is not desirable. The flyback converter suffers from leakage inductance problem which imposes a limit on its rating. To eliminate these issues, a Zeta PFC converter is employed as a PFC converter in many research papers. It provides a continuous output current with a low ripple output voltage along with a high level performance which is highly recommendable for PCs. The system configuration of a PFC Zeta converter based multi-output SMPS topology. At the input, a DBR with filter is connected to a non-isolated Zeta converter. It consists of two inductors  $L_{z1}$  and  $L_{z2}$ , one intermediate capacitor  $C_1$ , one high frequency switch S and one diode D. This PFC converter regulates the output dc voltage and draws a sinusoidal current from the ac mains at unity PF. Either Three different DCM conditions (i.e. input inductor DCM, intermediate capacitor DCM and output inductor DCM)or Continuous Conduction Mode can be considered here to choose the best operating condition of the front end PFC converter. In the DCM operation, the current becomes zero either in the input inductor or output inductor, or the voltage across the intermediate capacitor becomes zero for some duration in one switching cycle. Despite the better dynamic response of the converter in DCM the CCM mode enjoys the advantage of yielding better efficiency. Further the  $I_{peak}$  and  $V_{peak}$  is low on the switch stress in the CCM which means the switches used can be less expensive. Hence depending upon the application to be used a ZETA converter can be used in either of the mode as required. The output dc voltage is regulated using a Proportional-Integral (PI) voltage controller. The regulated output dc voltage is connected to an isolated converter for achieving multiple dc voltages at the output. The isolated converter consists of two equal valued input capacitors, two switches, one high frequency transformer (HFT) and filters. The filters are used in each output winding to reduce the output voltage and current ripples. Only one of the output voltages is directly sensed and the output voltages are controlled by the duty cycle of the isolated converter. The winding that is selected for control action is of the largest power rating among all the outputs. Further, to reduce the component stresses, the isolated converter is designed in CCM.

Another voltage PI controller is used here to regulate the output voltage .Simulation of the complete system is performed in PSIM and experimental results are verified.

Fig. 1 Proposed SMPS with PF correction and high frequency isolation.

# International Journal for Research in Applied Science & Engineering Technology (IJRASET)

## B. Zeta Converter based SMPS

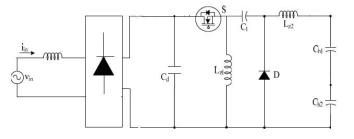

Zeta converter is fourth order DC-DC converter, which consists of two inductors and a series capacitor, which is sometimes called a flying capacitor. The ZETA converter has its main switch in series with the input power supply; because of this reason this converter is subjected to a greater level of stress in the input current than other basic fourth-order converter. The zeta converter designed for the proposed SMPS is shown in figure . The converter is composed of input filter capacitor  $C_d$ , Switch, input inductor  $L_{Z1}$ , output inductor  $L_{Z2}$ , intermediate capacitor  $C_1$ , freewheeling diode D, and two output capacitors connected in series. The zeta converter is designed in Discontinuous Conduction Mode

Fig. 2 Circuit diagram of ZETA converter.

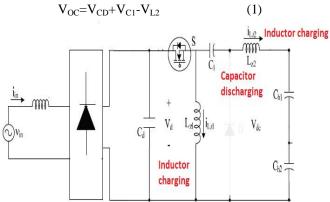

1) Operation of ZETA Converter – Model: When the PFC switch S turns on, the current in the input inductor  $L_{Z1}$  and output inductor  $L_{Z2}$  start increasing and the voltage across the capacitor C1 starts decreasing.

Fig. 3 Mode 1 of operation of ZETA converter.

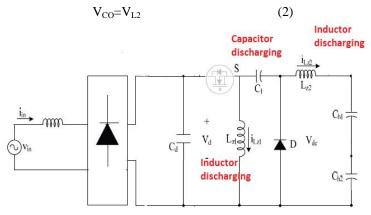

2) Operation of ZETA converter – Mode2: When S is turned off, diode D starts conducting. The stored energy in  $L_{Z1}$  starts decreasing and continues until the current through  $L_{Z1}$  equals the negative of the current through  $L_{Z2}$  The voltage across the intermediate capacitor C1 starts increasing.

Fig. 4 Mode 2 of operation of ZETA converter.

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

3) Operation of ZETA Converter – Mode3: Both switch S and diode D are off in this period of one switching cycle. This state lasts until the start of the next PWM cycle. The input current in LZ1 remains zero ensuring the DCM condition. The three operating modes are shown in fig 5.

Fig. 5 Input inductor is in Discontinuous Continuous Mode.

### C. Isolated DC-AC Converter

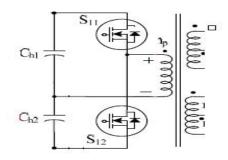

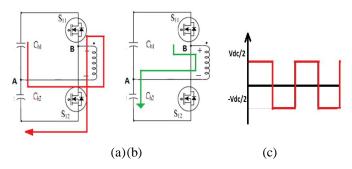

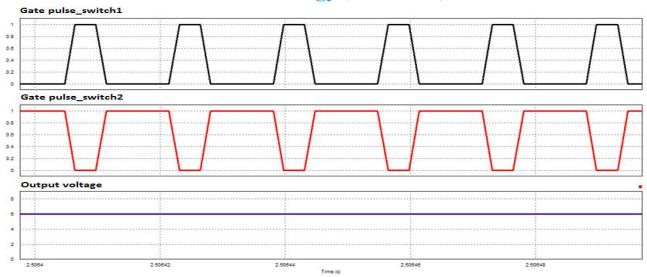

The output of the Zeta converter is DC output. To get multiple output the DC must convert to AC and this has to given to a transformer primary section. The output of the zeta converter is taken from serially connected capacitor with equal values. Between the two capacitor, the primary winding of the isolation transformer is connected with two switches. Hence it is actually equivalent to a H-Bridge inverter. It consist of two capacitors and two switches. By applying complementary pulses to the switches in H-bridge the output will be like sinusoidal as like the inverter output. The inverter output is then transformer has to convert to DC for SMPS output.

1) Operation of Isolated DC-AC converter: The operating modes are same as that of the H-bridge inverter. The DC voltage across the capacitor is become half when one switch is ON. The output will switch in positive as well as negative side. When switch S12 is ON, the output voltage is become +Vdc/2, during this time the switch S11 is OFF. Also when switch S11 is ON the output voltage is become -Vdc/2 where the switch S12 is OFF.

Fig. 6 Mode 2 operation of ZETA converter.

The output of the inverter is then given to the primary of the transformer and this transform to required AC voltage level. To get different DC voltage at SMPS output side Full/Half bridge rectifier is required.

Fig. 7 Isolated converter: (a) switch S12 is ON, (b) switch S11 is ON, (c) Output of H-bridge DC/AC converter

# International Journal for Research in Applied Science & Engineering Technology (IJRASET)

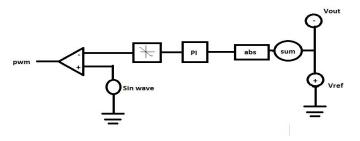

## D. Control Strategy

The control algorithm used here is a voltage follower method. The PWM is generated by comparing the two voltages, one of the voltages is the output voltage of converter and the next is a reference voltage. Here in conventional SMPS two separate control loop is required. One loop for the generation of pwm pulses to the Zeta converter switch and other loop for the pulse generation for isolated converter. The PI controller is used for the control loop operation. The value of Kp,Ki are selected according to the operation. The measured power factor of the conventional circuit violates the international standards.

Fig.8 Control strategy used in Zeta converter and Isolated DC/AC converter

#### E. Simulation of Proposed Circuit

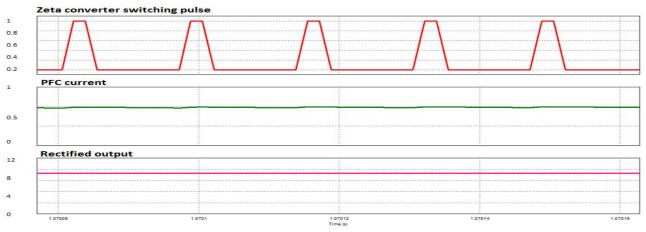

The proposed model is simulated by reducing the rating of the circuit. The simulations are done based on the hardware aspects. The control strategy is more simple here. Instead of having two control loop only one loop is used here. One of the load voltage is fed back for the PWM generation. The load voltage is compared with one reference voltage and that error is used for pulse generation for the Zeta converter switch, and load voltage is compared with another reference voltage for the isolated converter switching pulse.

Fig. 9 Simulation diagram of proposed circuit.

Fig. 10 Pulse waveforms of Zeta converter and rectified output.

www.ijraset.com IC Value: 45.98

# International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig. 11 Pulse waveforms of DC/AC converter and load voltage.

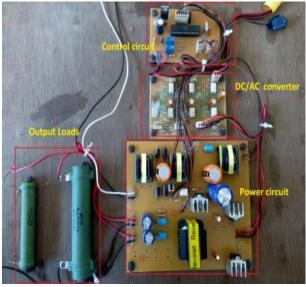

The hardware is implemented in reduced circuit model. The input AC voltage can be step down to 12V using a 12-0-12 center tapped transformer or can use direct 12V through an autotransformer. The AC input voltage is converted to dc voltage by a diode bridge rectifier. The DC is then applied to the zeta converter and the output of the zeta converter is DC voltage which is then converted to AC by a H-bridge DC-AC converter. The H-bridge is printed on another circuit board in the hardware setup. The isolation transformer is fixed on the power circuit PCB. More secondary load connecting slots are printed in the PCB for future expansion of the work. The loads are connected in the outside of the PCB's. The hardware setup is shown in fig 12.

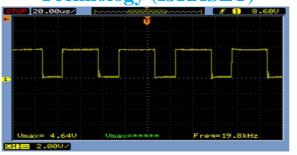

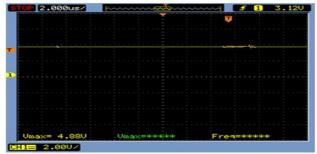

The Zeta converter is operating in DCM. So input inductor current is discontinuous. The PWM pulse is formed by comparing load voltage with the reference value or set value. The isolated converter switching pulses are complement to each other .The pulse is generated by comparing load voltage with a reference value. In dsPIC the output pins has its own High and Low pins, so it has complementary values. Hence by forming one pulse its complementary is also forming at the Low pin. Both pulses are applying to the Mosfet's in Isolated converter. This converting the DC link capacitor value to AC by alternate ON& OFF. This AC signal is transferring to the secondary terminal of High Frequency isolation Transformer. The load voltages are formed across the load resistors. From the design it is calculated as 20 for both outputs. The load voltages are shown in fig 15 and fig 16. Also the input factor is measured as 0.904 which is satisfying the international standards.

Fig. 12 Mode 2 operation of ZETA converter.

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig. 13 Mode 2 operation of ZETA converter.

Fig. 14 Complementary pulses to the DC/AC converter

|          | and the second se |  |                   |                   |     |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------------|-------------------|-----|

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  | the second second | Concession of the |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

|          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

| Vmax= 1  | 1.4 U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  | Ere               | q=: 19.9          | KHZ |

| HIE 2.00 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |                   |                   |     |

Fig. 15 Load voltage of 12 V

Fig. 16 Load voltage of 5V.

## **II. CONCLUSION**

A DCM operated front end PFC converter cascaded with a multiple output isolated converter has been used for the design of an SMPS for PCs. It has been designed, modeled, simulated and developed for input power quality improvement and output voltage regulation. All the dc output voltages are regulated by controlling only one output voltage. From the hardware model it is evident that the proposed power supply is able to mitigate power quality problems that are present in the conventional SMPS systems. In the prototype the circuit is modeled with reduced ratings. For an AC input voltage of 12V the SMPS producing multiple output of 12V

International Journal for Research in Applied Science & Engineering

**Technology (IJRASET)**

and 5V. Also a power factor of 0.904 is achieved.

#### **III. ACKNOWLEDGMENT**

It is a great pleasure to acknowledge all those who have assisted and supported me for successfully completing my project. I thank God Almighty for his blessings as it is only through his grace that I was able to complete my project successfully. I take this opportunity to extend my sincere thanks to my project guide Dr. Bos Mathew Jos, Professor and all the members of the Department of Electrical & Electronics Engineering for sharing their valuable comments during the preparation of the project. express my deep sense of gratitude to Prof. Acy M Kottalil, Head of Electrical & Electronics Engineering Department, for the valuable guidance as well as timely advice which helped me a lot in doing the project successfully. I also extend my deep sense of gratitude to PG Coordinator, Sri. George John P, Professor, Electrical & Electronics Engineering Department and our Faculty Advisor and project coordinator, Smt. Beena M Varghese, Associate Professor, Electrical & Electronics Engineering Department for their creative suggestions during the preparation of the project. I whole - heartedly thank all my classmates, for their valuable suggestions and for the spirit of healthy competition that existed between us.

#### REFERENCES

- [1] Sikha Sing, Bhim Sing, Power factor corrected zeta converter based switched mode power supply, IEEE Trans. Industrial Electronics, vol.55, no. 1, pp. 154162, Jan. 2008.

- [2] J. Bhim Sing , Analysis and design and implementation of single phase power factor corrected AC/DC converter with high frequency isolation , Journal of electrical engineering and technology ,2008

- [3] N. Selvarani, P. Satheesh kumar, Power factor correction based zeta converter for BLDC Motor drive, Middle- east journal of scientific research, 2016.

- [4] R. S. Prem kumar, D. Praveen sangeeth Kumar, Zeta converter for boost up in low frequency application low frequency instrumentation, IJCTT TRANSACTION, 2012.

- [5] Jeff Falin, Designing of DC/DC Converter based on zeta converter topology, Power management, Texas instrument.

- [6] D. O. Koval, and C. Carter, Power quality characteristics of computer loads, IEEE Trans. Ind. Applications, vol. 33, no. 3, pp. 613-621, 1997.

- [7] T. F. Wu, Y S. Lai, J. C. Hung, and Y M. Chen, Boost converter with coupled inductors and buck-boost type of active clamp, IEEE Trans. Industrial Electronics, vol.55, no. 1, pp. 154162, Jan. 2008.

- [8] D. D. Gaikwad, M. S. Chavan, M. S. Gaikwad, Hardware Implementation of DC-DC Converter for MPPT in PV Applications, IEEE Global Conference on Wireless and Networking, 2014

- [9] Jawad Ahmad, A Fractional Open Circuit Voltage Based Maximum Power Point Tracker for Photovoltaic Arrays, 2<sup>nd</sup> International Conference on Software Technology Engineering(ICSTE), 2010

- [10] D.Baimel, R.Shkoury, L.Eblaz, Novel Optimized Method for Maximum Power Point Tracking in PV Systems Using Fractional Open Circuit Voltage Technique, International Symposium on Power Electronics, Electrical Drives, Automation and Motion, 2016.

- [11] Ali F Murtaza, Hadeed Ahmed Sher, Chiaberge M, A Novel Hybrid MPPT Technique for Solar PV Applications Using Perturb & Observe and Fractional Open Circuit Voltage Technique, MECHATRONICA 15<sup>th</sup>International Symposium, 2012

- [12] The IEEE website. [Online]. Available: http://www.ieee.org/

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)