IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: VI Month of publication: June 2017 DOI:

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

*Volume 5 Issue VI, June 2017 ISSN: 2321-9653*

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

## Implementation of High Speed Vedic Multiplier for Digital Signal Processing Using Multiplexer Based Adder

Neha Tyagi<sup>1</sup>, Neeraj Kumar Sharma

<sup>1</sup>Electronics and Communication Department, Vivekanand Institute of Technology, Ghaziabad, India <sup>2</sup>Associate Professor, Vivekanand Institute of Technology, Ghaziabad, India

Abstract: Digital signal processors (DSPs) are very important in various engineering disciplines. Fast multiplication is very important in DSPs for convolution, Fourier transforms, etc. A fast method for multiplication based on ancient Indian Vedic mathematics is proposed in this paper. The whole of Vedic mathematics is based on 16 sutras (word formulae) and manifests a unified structure of mathematics. Among the various methods of multiplication in Vedic mathematics, Urdhava tiryakbhyam is discussed in detail. Urdhava tiryakbhyam is the general multiplication formula applicable to all cases of multiplication. The coding is done in Verilog and synthesis is done using Xilinx ISE 14.5. The combinational delay obtained after the synthesis is compared with existing multiplier. Further, this Vedic multiplier is used in matrix multiplication. This Vedic multiplier can bring great improvement in the DSP performance.

Keywords: Vedic multiplier, Urdhava tiryakbhyam, Verilog HDL, DSP.

#### I. INTRODUCTION

Multipliers are frequently used in DSP, image processing architectures and microprocessors. It plays an important fundamental function in arithmetic operations. These days in modern VLSI design delay in data path is considered as a critical parameter. In present time designers are demanding high speed of operation, so it is essential to minimize the delay. There has been lot of researches and work to reduce the delay and now designers have shifted their focus on making a multiplier circuit which are efficient and considerably faster.

A high speed processor performance greatly depends on the multiplier, in most digital signal processing systems as well as in allpurpose processors which is one of the essential hardware components also its consumed area is more. Vedic multiplier gives the fast speed of operations than the conventional multiplier and requires less system memory. As compared to existing multiplier design this multiplier requires very small area. Here in this work we use MUX based adder for designing Vedic multiplier, this adder minimize the delay and reduced consumed area. In this paper 16- bit Vedic multiplier using MUX based adder has been designed The results shows that the proposed 16- bit Vedic multiplier is faster than 16- bit Vedic multiplier with normal adder. The reduction in the delay is approximately 30.6%. The main purpose of this work is to design and implement a high speed 16 X 16 bit Vedic multiplier by combining the best technique in Vedic mathematics named Urdhva Tiryagbhyam and MUX based adder.

#### II. VEDIC MATHEMATICS

The ancient Indian Vedic mathematics is now currently used in our global silicon chip technology for easier and faster calculations. The proposed Vedic multiplier is based on the Vedic multiplication formulae (Sutras). By using three sutras of Vedic mathematics the complex number multiplication can be done, which are Urdhva Tiryakbhyam sutra, Ekadhikena Purvena, and Nikhilam Navatascaraman Dasatah or simply Nikhilam. The Nikhilam sutra of Vedic mathematics can only be applied to large number multiplication. While the Urdhva Tiryakbhyam method of Vedic mathematics can be efficiently applied to all cases of multiplication. This is a universal method for obtaining fast multiplication which can be applied everywhere. It is very simple and easy to implement. For the multiplication of two numbers in the decimal number system these Sutras have been traditionally used. In this present work, we apply the same ideas to the binary number system for making the proposed algorithm compatible with the digital hardware.

A. Urdhva Tiryagbhyam

www.ijraset.com IC Value: 45.98 *Volume 5 Issue VI, June 2017 ISSN: 2321-9653*

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

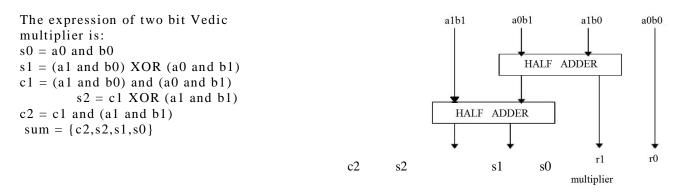

Urdhva Tiryakbhyam Sutra is a general multiplication formula which is applicable to all cases of multiplication. It literally means "Vertically and crosswise". This Sutra has been conventionally used for multiplication of two numbers in the decimal number system. The same idea has been applied for binary multiplication in this work. By breaking into smaller sizes, this can solve the multiplication of larger number (N X N bits). The 2 x 2 Vedic multiplier are basic building module through which higher multiplier are designed by splitting into smaller sizes.

This algorithm can be implemented into three steps which are as follows:

Step-1: The first step is vertical multiplication of LSB of both multiplicands.

Step-2: Second step is crosswise multiplication and additions of the partial products.

Step-3: Third step is vertical multiplication of MSB of the multiplicand and

addition with the carry propagated from step 2.

For better understanding consider 2-bit two binary number are a1a0 and b1b0. The below figure 1 shows the 2 bit multiplier.

Figure 1: Line Diagram for 2 X 2 Bit binary multiplication using Urdhva Tiryagbhyam Sutra

B. Algorithm for 16 X 16 Bit binary numbers Multiplication Using Urdhva Tiryagbhyam: A=A15A14A13A12A11A10A9A8 A7A6A5A4A3A2A1A0 X1 X0 B=B15B14B13B12B11B10B9B8 B7B6B5B4B3B2B1B0 Y1 Y0

F E D C

CP = X0 \* Y0 = C CP = X1 \* Y0 + X0 \* Y1 = D CP = X1 \* Y1 = EWhere CP=Cross product

#### C. Nikhilam Sutra

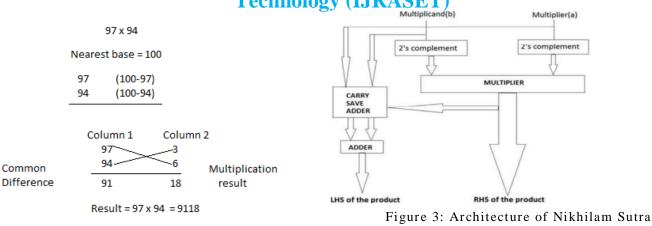

Nikhilam Sutra literally means "all from 9 and last from 10". Although it is applicable to all cases of multiplication, it is more efficient when the numbers involved are large.

To perform multiplication with Nikhilam Sutra, compliment of the numbers from the nearest base is required, larger is the original number, lesser the complexity of the multiplication. So this method is more efficient for large numbers which are nearer to the base. We first illustrate this Sutra by considering the multiplication of two decimal numbers (97 \* 94) where the chosen base is 100 which is nearest to and greater than both these two numbers.

Figure 2: Multiplication Using Nikhilam Sutra

The right hand side (RHS) of the product can be obtained by simply multiplying the numbers of the Column 2 (3\*6 = 18). The left hand side (LHS) of the product can be found by cross subtracting the second number of Column 2 from the first number of Column 1 or vice versa 97 - 6 = 91 or 94 - 3 = 91. The final result is obtained by concatenating RHS and LHS (Answer = 9118).

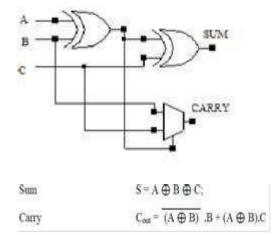

#### III. MUX BASED ADDER

For efficient implementation adders become a critical hardware unit of multiplier. The speed of multiplier ultimately increased when the delay of the adder is reduced. In terms of delay and power dissipation, it is observed that full adder with multiplexer and XOR gate gives best performance, especially. It consists of two XOR gates and one 2x1 MUX as shown in Fig. 4.

Figure 4: Architecture of MUX based adder

By using logical effort method we can calculate delay mathematically instead of using simulation tools. It gives a simple method to select best logical topology. Let us assumed 'd' is the delay for a single stage network in term of is logical effort 'g', electrical effort 'h' and parasitic delay 'p', than the delay can be calculated by the equation (1) as given below

$$l = g*h+p;$$

where 'g 'represents logic gate's ability to produce output current (Compared to inverter, how much worse it is in producing output current), 'h' gives ratio of output capacitance to input capacitance and p gives delay of gate due to internal capacitance.

(1)

#### IV. DESIGN OF 16 X 16 VEDIC MULTIPLIER USING MUX BASED ADDER

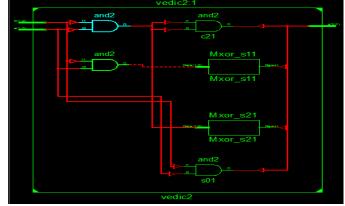

The 2 x 2-bit Vedic multiplier is the basic building section for the system. Two Half adders are required in designing 2 x2 Vedic Multiplier, Figure 5 gives the architecture of 2 x 2 bit Vedic multiplier.

Figure 5 architecture of 2 x 2 bit Vedic Multiplier

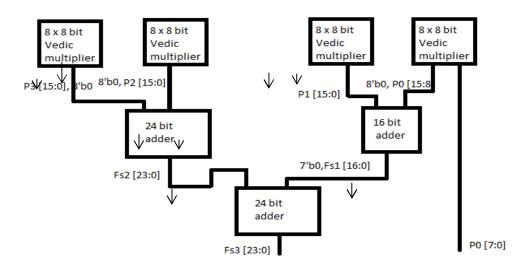

The 4 x 4-bit multiplier is designed by using four 2 x 2-bit Vedic multiplier. The 8 x 8 bit Vedic multiplier is designed by using four 4 x 4 bit Vedic multiplier building blocks. The approach applied for designing a 16 x 16-bit Vedic multiplier by using four 8 x 8 bit multiplier blocks and two 24-bit and one 16-bit MUX based adder blocks is shown in figure 6.

Figure 6 Block diagram of 16 x 16 bit Vedic Multiplier using MUX based adder

#### V. RESULT

#### A. Synthesis

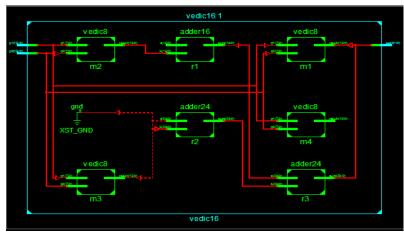

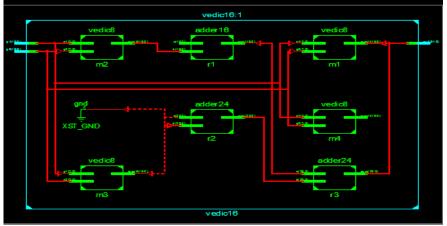

The Verilog code of proposed Vedic multipliers (using MUX based adder) and conventional Vedic multiplier are synthesized using XILINX ISE 14.5. The figure 7 & 8 shows the RTL diagrams of both multipliers.

The functionality of Vedic multiplier is verified and confirms the operation of the design from the simulated waveforms. The combinational delay is reduced drastically with a little bit of trade off in terms of area. ISim simulator is used for simulation purpose. Figure 9& 10 shows the Simulation result for 16 bit Vedic multiplier in which 'P1' and 'P2'are same set of inputs and 'out' is their product and table 1 gives the delay and number of slice LUTs comparison between these two design architecture.

Figure 7: RTL view of 16x16 conventional Vedic multiplier

Figure 8: RTL view of 16x16 Vedic multiplier using MUX based adder

#### B. Simulation

|                |                                         |                          |                 |                                         |                    | <u>5,0</u>               | Name                                               | Value                                   | 1,999,992 ps     | 1,999,993 ps | 1,999,994 ps | 1,999,995 ps                            | 1,999,995 ps                            | 1,999,997 ps | 1,999,998 ps | 1,999,999 ps |

|----------------|-----------------------------------------|--------------------------|-----------------|-----------------------------------------|--------------------|--------------------------|----------------------------------------------------|-----------------------------------------|------------------|--------------|--------------|-----------------------------------------|-----------------------------------------|--------------|--------------|--------------|

| Name           | Value                                   | 2,999,992 ps   2,999,993 | ps 2,999,994 ps | 12,999,995 ps 12,999,996 ps             | 12,999,997ps  2,99 | 19,998 ps   2,999,999 ps | 🕨 <table-of-contents> p1(15:0)</table-of-contents> | 11110003030000030                       |                  |              |              | 11110000                                | 000000                                  |              |              |              |

| 🕨 🎽 p1(15:0)   | 111100000000000000000000000000000000000 |                          |                 | 1111000000000000                        |                    |                          | 🕨 🖬 p2(15x0)                                       | 101011111111111                         |                  |              |              | 10001111                                | 1111111                                 |              |              |              |

| # p2(15:0)     | 101011111111111                         |                          |                 | 900011111011111                         |                    |                          | 🕨 📲 out[31:0]                                      | 10000110111111100                       |                  |              |              | 300001101111111                         | 000100000000000000000000000000000000000 |              |              | i            |

| ▶ 📲 out[31:0]  | 100001101111111000100000000000          |                          |                 | 10001101111111000100000000              | 0                  |                          | 🕨 🙀 v1(15:0)                                       | 001000000000000000                      |                  |              |              |                                         | 000000                                  |              |              |              |

| ▶ 👹 d(154)     | 000000000000000000000000000000000000000 |                          |                 | 01001000000000                          |                    |                          | 🕨 🙀 v2(15:0)                                       | 1110111100010000                        |                  |              |              | 11101119                                | 00000                                   |              |              |              |

| 🕨 🕌 dji54]     | 1110111100010000                        |                          |                 | 1110111100010000                        |                    |                          | 🕨 😽 v3(15:0)                                       | 001000000000000000                      |                  |              |              |                                         | 0000000                                 |              |              |              |

| 🕨 👹 (6(154)    | 000000000000000000000000000000000000000 |                          |                 | 000000000000000000000000000000000000000 |                    |                          | ► 😽 v4(150)                                        | 1000011000010000                        |                  |              |              | 10000110                                | 00010000                                |              |              |              |

| 🕨 🕺 Müzzi      | 1000011000010000                        |                          |                 | 1000011000010000                        |                    |                          | 🕨 🐝 w1(15:0)                                       | 001000000000000000                      |                  |              |              |                                         | 000000                                  |              |              |              |

| 🕨 🙀 walazal    | 000000000000000000000000000000000000000 |                          |                 | 000000000000000000000000000000000000000 |                    |                          | 🖌 🐝 suni(160)                                      | 01110111100010300                       |                  |              |              | 011101111                               | 00010000                                |              |              |              |

| 🕨 👹 sumi(16d)  | 01110111101010000                       |                          |                 | 01110111100030000                       |                    |                          | ▶ 🐝 sun2[23:0]                                     | 10000110000100000                       |                  |              |              | 100001100001                            | 000000000                               |              |              |              |

| ▶ 🙀 sum2(23.0) | 1000011000010000000000000               |                          |                 | 10000110000100000000000                 |                    |                          | 🕨 🐝 sun3(23:0)                                     | 101001101111111100                      |                  |              |              | 100001101111                            |                                         |              |              |              |

| ▶ 👹 sum3(23:0) | 10000110111111100010000                 |                          |                 | 100001101111110100010000                |                    |                          | - • • • • • • • • • • • • • • • • • • •            | 000000000000000000000000000000000000000 |                  |              |              | 000000000000000000000000000000000000000 |                                         |              |              |              |

| ▶ 👹 w2[23:0]   | 000000000000000000000000000000000000000 |                          |                 | (0)100100100000000000000000000000000000 |                    |                          |                                                    | 100001100001000000                      | _                |              |              | 100001100001                            |                                         |              |              |              |

| 🕨 👹 wə(23d)    | 100001100001000000000000                |                          |                 | 10000110000100000000000                 |                    |                          |                                                    |                                         |                  |              |              |                                         |                                         |              |              |              |

| 🕨 🙀 w4(23d)    | 000000001110111100010000                |                          |                 | 0000000011131111000010000               |                    |                          | ▶ 🙀 w4[23:0]                                       | 000000001110111100                      | _                |              |              | 000000001110                            | 11110010000                             |              |              |              |

|                |                                         |                          |                 |                                         |                    |                          |                                                    |                                         |                  |              |              |                                         |                                         |              |              |              |

|                |                                         |                          |                 |                                         |                    |                          |                                                    | _                                       |                  |              |              |                                         |                                         |              |              | d            |

|                |                                         | X1: 3,000,000 ps         |                 |                                         |                    |                          |                                                    |                                         | X1: 2,000,000 ps |              |              |                                         |                                         |              |              |              |

Figure 6: Simulation Result of 16X 16 bit Conventional multiplier Figure 7: Simulation Result of 16X 16 bit Vedic multiplier using MUX based adder

using Brent Kung adder

| Туре                                      | No. of<br>Bits | NoToatble 1<br>bonded IOs | : Delay<br>(ns) | Level of logic | Number of<br>Slice LUTs |  |

|-------------------------------------------|----------------|---------------------------|-----------------|----------------|-------------------------|--|

|                                           | 16             | 64                        | 20.347          | 23             | 623                     |  |

| Vedic multiplier using MUX<br>based adder | 16             | 64                        | 16.142          | 23             | 513                     |  |

Conventional Vedic multiplier

#### V. CONCLUSION AND FUTURE WORK

This paper work presents a high performance design for multiplication by combining the feature of Vedic mathematics and MUX based adder. When we compared our purposed design with conventional Vedic multipliers proposed design gives much less delay. We conclude that the proposed Vedic multiplier is a p p r o x i m at ely 30% faster from conventional Multiplier. The multiplier architecture and fast performance makes this particularly attractive for VLSI implementations. For future work, its performance within MAC unit and ALU can be tested and compared with other conventional and Vedic designs. This 16 bit Multiplier can be further extended to 32 bit or 64 bit multiplier.

#### REFERENCES

- [1] Computure arithmetic "Algorithm and hardware design" by "Behrooz Parhami

- [2] Gaurav Sharma, Arjun Singh Chauhan, Himanshu Joshi, Satish Kumar Alaria "Delay Comparison of 4 by 4 Vedic Multiplier based on Different Adder Architectures using VHDL" International Journal of IT, Engineering and Applied Sciences Research (IJIEASR), Volume 2, No. 6, June 2013.

- [3] Diptendu Kumar Kundu, Supriyo Srimani, Saradindu Panda, Prof. Bansibadan Maji "Implementation of Optimized High Performance 4x4 Multiplier using Ancient Vedic Sutra in 45 nm Technology" 2014 2nd International Conference on Devices, Circuits and Systems (ICDCS), 978-1-4799-1356-5/14/\$31.00 ©2014 IEEE.

- [4] Saji. M. Antony, S.Sri Ranjani Prasanthi, Dr.S.Indu, Dr. Rajeshwari Pandey, "Design of High Speed Vedic Multiplier using Multiplexer based Adder" 2015 International Conference on Control, Communication & Computing India (ICCC) 19-21 November 2015, IEEE.

- [5] S R Panigrahi, 0 P Das, B B Tripathy, T K Dey, "FPGA Implementation of a 4x4 Vedic Multiplier", International Journal of Engineering Research and Development, Volume 7, Issue 1 (May 2013), PP. 76-80.

- [6] Poornima M, Shivaraj Kumar Patil, Shivukumar, Shridhar K P, Sanjay H, "Implementation of Multiplier using Vedic Algorithm" International Journal of Innovative Technology and Exploring Engineering, Volume-2, Issue-6, May 2013

- [7] Maroju SaiKumar, Dr. P. Samundiswary "Design and Performance Analysis of Various Adders using Verilog", IJCSMC, Vol. 2, Issue. 9, September 2013, pp. 128-138

- [8] M. Zamin Ali Khan, Hussain Saleem, Shiraz Afzal and Jawed Naseem"An Efficient 16-Bit Multiplier based on Booth Algorithm" International Journal of Advancements in Research & Technology, Volume 1, Issue 6, November-2012.

- [9] Shamim Akhter," VHDL implementation of fast N×N multiplier based on Vedic Sevilla Spain, pp. 472-475, August, 2007.

- [10] S. S. Kerur, PrakashNarchi, Jayashree C N Harish M Kittur and Girish V A, "Implementation of Vedic Multiplier for Digital Signal Processing", International Conference on VLSI, Communication & Instrumentation (ICVCI) 2011.

- [11] ShamimAkhter, "VHDL Implementation of Fast NXN Multiplier Based on Vedic Mathematics", Jaypee Institute of Information Technology University, Noida, 201307 UP, INDIA, 2007 IEEE.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)