IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: VII Month of publication: July 2017 DOI:

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

# Design of High Speed 16-Bit Vedic and Booth Multiplier

Ku. Damini C. Dandade<sup>1</sup>, Prashant R. Indurkar<sup>2</sup>

<sup>1</sup>M.Tech Student, Department of Electronics and Telecommunication, B.D.C.O.E, Wardha, Maharashtra, India <sup>2</sup>Associate professor, Department of Electronics and Telecommunication, B.D.C.O.E, wardha, Maharashtra, India

Abstract: In VLSI design the performance of any system is determined by the performance of the elements of the system. Multiplier is the slow element in the system. The multiplier speed is depends on multiplication technique and type of adder. This paper proposes the type of architecture of 16\*16 Vedic and Booth multiplier. The code is implemented in XILINX ISE 14.5 software. The combinational path delay of 16\*16 bit Vedic and booth multiplier obtained after synthesis is compared with existing multiplier and found that the proposed Vedic multiplier circuits seems to have better performance in terms of speed. KeyWords: VLSI, Vedic multiplier, Booth multiplier, XILINX, etc.

## I. INTRODUCTION

Multiplication is one of the fundamental functions in arithmetic operations. In a Digital Signal Processors multipliers are the key components. Since multiplication dominates the execution time of many DSP algorithms, so there is need of high speed multiplier. The demand of high speed processing is increasing in computer and DSP application. Efficient arithmetic operations are important to achieve the desired performance in many real-time signals.

Hence continuous efforts are taken to improve the performance of multiplier by reducing the speed. There are several methods have been used for multipliers such as Braun-Array, Baugh-Wooley method of two's complement and Booth's algorithm is the most successful method for multiplication.

In this paper a simple 16\*16 bits multiplier is proposed which is based on Urdhva tiryabhyam sutra of Vedic mathematics and on Booths algorithms. The two numbers of 16 bit each are multiplied by using Vedic maths. The main concept behind this is that to reduce the propagation delay of the architecture which is the drawback of Booth's algorithm. As the number of bit increases in the Booth's algorithm delay increases noticeably and for Vedic mathematics as number of bit increases delay increases slightly. In the end we have compared the tow algorithms on the basis of certain parameters and prove that Vedic mathematics is the best way to multiplication of higher number of bits like 16\*16 bit.

## II. BOOTH ALGORITHM

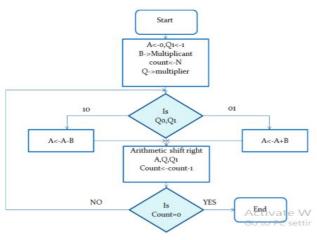

The Booth's multiplier based on Booth's algorithm. This method is given by "Andrew Donald Booth". The given flowchart describes the method.

Fig. 1. Flow chart for Booth algorithm

The Booth's multipliers scan the three bits at time to reduce the number of partial product. These three bits are the two bits from the present pair and third bit from high order bit of an adjacent lower order pair.

# A. From above Flow Chart we have Algorithm as follows

- 1) The multiplier and multiplication are placed in Q and B registers respectively.

- 2) A one bit Q(-1) register is placed at the least significant bit of Q(0) of register Q.

- 3) The final results appears in A.

- 4) A and Q(-1) registers are initialized to 0. Earlier days this Booth's multiplier is very suitable for multiplication. This will give the accurate result of multiplication.

- 5) Multiplication of no. Is one in n cycle

- 6) In each cycle Q(0)and Q(-1) are examined. i if Q(0) and Q(-1)are (1-1 or 0-0) then all the bits of A, Q AND Q(-1) registers shifted right by 1 bit. ii if Q(0) and Q(-1) are 01 then multiplication is added with A. After addition A Q and Q(-1) registers are shifted right by 1 bit. iii if Q(0) and Q(-1) are 10 then multiplication is substracted from A. After substraction A Q and Q(-1) registers are shifted to right by 1-bit

- 7) The final result appears in A.

In this multiplier has some drawback. The drawbacks can be overcome by designing suitable multiplier for 16\*16 bit multiplication. We will design the new multiplier as Vedic multiplier by using the concept of Vedic mathematics.

# III. VEDIC MULTIPLIER

Vedic multiplier is based on Vedic mathematics. Vedic mathematics is the ancient method of mathematics. It was rediscovered from Vedas in between 1911 to 1918 by Sri Bharti Krishna Ttirthaji (1884-1960). Who was mathematician and Sanskrit scholar. The Vedic mathematics is based on the 16 sutras of Urdhva Tiryagbhyam. It simply means that "vertically and crosswise multiplication". It involves minimum no. of calculations, it reduces the space, save the computational time and it is applicable in all cases of multiplication. This method is most efficient when the number of bit increases in multiplication.

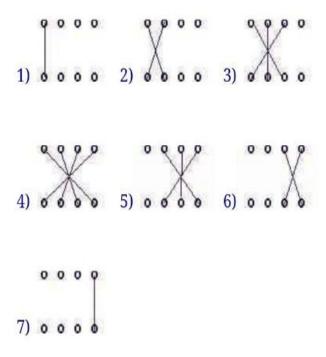

The structure of this method is shown in the fig-2 from this we get clear idea about "vertical and crosswise multiplication". For multiplication of 4 bit numbers the process is divided into 7 steps. The first no. is X3X2X1X0 which is multiplier and second no. is Y3Y2Y1Y0 which is multiplicand as shown in step 1 of the figure.

The LSB(least significant bit) of multiplier is multiplied with LSB of the multiplicand and the result of this multiplication is stored as the LSB of the final result. Then as shown in the step2 of the above figure the LSB of the multiplier is multiplied with second higher bit of multiplier is multiplied with LSB of multiplicand and second higher bit of multiplier is multiplied with LSB of multiplicand and then these two partial product are added, after adding these two numbers the LSB of addition is taken as the second higher bit of the final result and remaining bits of the addition are taken as carry bit and this carry can be of multi-bit. Then follow the steps which are given in above figure and after that we get result of 4-bit multiplication.

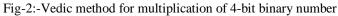

In this paper we have done 16-bit multiplication and for that we require different modules of the 2-bit, 4-bit, 8-bit Vedic multiplier. the 16\*16 bit Vedic multiplier, this multiplier is implemented from the 8\*8 multiplier. in this diagram X0 to X15 are the bits of first digit and Y0 to Y15 are the bits of second digit. For 16\*16 multiplier we require four 8\*8 multiplier and three adders after doing the procedure as shown in fig-3, we will get the result of 16\*16 multiplier and the result obtained is of 32 bits. The adder used in this proposed work is CSA adder which minimizes partial product.

Fig-3:-16\*1 Vedic multiplier by using CSA adder

# IV. IMPLEMENTATION ON XILINX SOFTWARE

Now we are moving towards main programming parts. Using the Vedic multiplier and Booth multiplier we have to develop a program. In this paper the 16\*16 bit multiplier is designed in VHDL (very high speed integrated circuits hardware description language). Synthesis and simulation was done in XILINX ISE 14.5. project navigator and simulator integrated in the XILINX package. XILINX is software which is purely based on the VHDL language. VHDL is Very Large Scale Integrated Circuit Hardware Description Language. We have performed our programming using the Vertex6XC6VCX75T FF84-2. Integrated Software Environment is a software tool produced by Xilinx for synthesis and analysis of HDL design, enabling the developer to synthesize their design, perform time analysis, examine RTL diagrams, simulate a design reaction to different stimuli, and configure the target device with the programmer. It includes ISE simulator which we can use for functionality verification of program. The programming is divided into 4 parts. For developing the multiplier 16\*16 bit, we have to first develop the multiplier of 2\*2, 4\*4 and 8\*8

# V. EXPERIMENTAL RESULT

The result of the 16\*16 Vedic and Booth multiplier is given in the figures below in which 16-bit number is in binary form. Also the RTL schematic of Vedic and Booth multiplier is given.

|             |                                         |                |         |                                         |          | 744.00 | 00 ns  |

|-------------|-----------------------------------------|----------------|---------|-----------------------------------------|----------|--------|--------|

| Name        | Value                                   | 0 ns           | 200 ns  | 400 ns                                  | 600 ns   | 1      | 800 ns |

| ▶ 📑 x[15:0] | 000000000001000                         | C              |         | 000000000000000000000000000000000000000 |          |        |        |

| ▶ 🏹 y[15:0] | 000000000000000000000000000000000000000 | $\sim$         |         | 000000000000000000000000000000000000000 |          |        |        |

| ▶ 📑 z[31:0] | 000000000000000000000000000000000000000 | $\sim$         | 0000000 | 000000000000000000000000000000000000000 | 00010000 |        |        |

|             |                                         |                |         |                                         |          |        |        |

|             |                                         |                |         |                                         |          |        |        |

|             |                                         |                |         |                                         |          |        |        |

|             |                                         |                |         |                                         |          |        |        |

|             |                                         |                |         |                                         |          |        |        |

|             |                                         |                |         |                                         |          |        |        |

|             |                                         |                |         |                                         |          |        |        |

|             |                                         | X1: 744.000 ns |         |                                         |          |        |        |

# Fig-4:-simulation result of Booth multiplier

|                                   |                                         | 0.843 ns     |         |                                         |          |           |

|-----------------------------------|-----------------------------------------|--------------|---------|-----------------------------------------|----------|-----------|

| Name                              | Value                                   | 0 ns         | 200 ns  | 400 ns                                  | 600 ns   | 800 ns  1 |

| 🕨 🍓 x[15:0]                       | 000000000000100                         |              |         | 000000000000000000000000000000000000000 |          |           |

| 🕨 🏹 y[15:0]                       | 000000000000010                         |              |         | 000000000000000000000000000000000000000 |          |           |

| 🕨 🍓 z[31:0]                       | 000000000000000000000000000000000000000 |              | 0000000 | 000000000000000000000000000000000000000 | 00001000 |           |

| 9. p. 19. (2).<br>19. p. 19. (2). |                                         |              |         |                                         |          |           |

|                                   |                                         |              |         |                                         |          |           |

|                                   |                                         |              |         |                                         |          |           |

|                                   |                                         |              |         |                                         |          |           |

|                                   |                                         |              |         |                                         |          |           |

|                                   |                                         |              |         |                                         |          |           |

|                                   |                                         |              |         |                                         |          |           |

|                                   |                                         |              |         |                                         |          |           |

|                                   |                                         |              |         |                                         |          |           |

|                                   |                                         |              |         |                                         |          |           |

|                                   |                                         |              |         |                                         |          |           |

|                                   |                                         |              |         |                                         |          |           |

|                                   |                                         |              |         |                                         |          |           |

|                                   |                                         | X1: 0.843 ns |         |                                         |          |           |

|                                   |                                         | X1.0.045 HS  |         |                                         |          |           |

Fig-5:-simulation result of Vedic multiplier

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VIII, July 2017- Available at www.ijraset.com

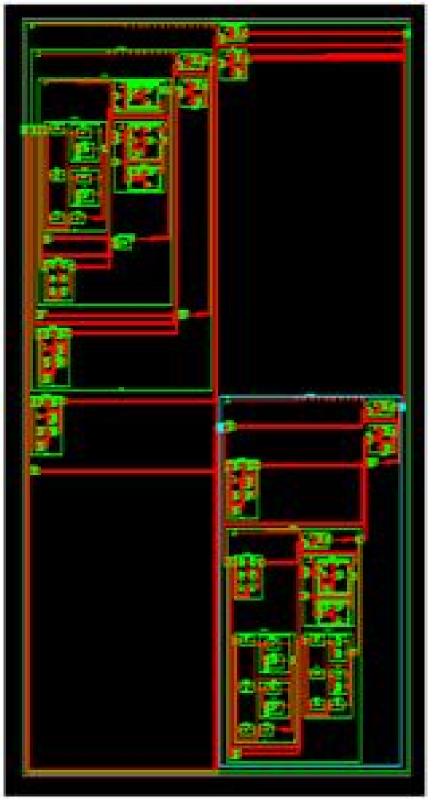

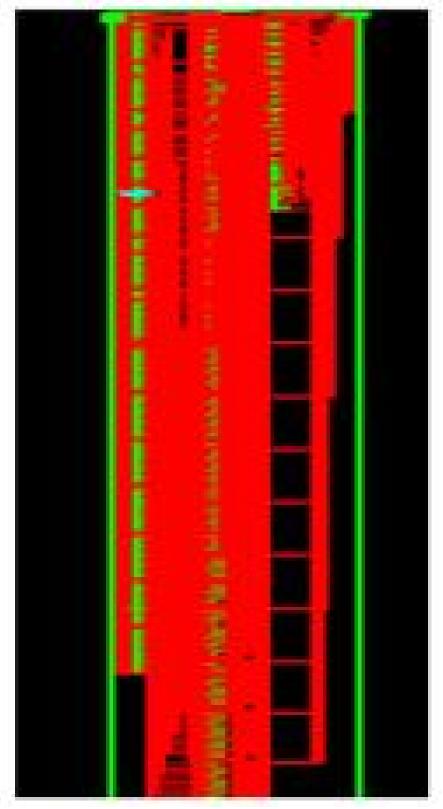

Fig. 6. RTL schematic view of Vedic multiplier

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VIII, July 2017- Available at www.ijraset.com

Fig-7:-RTL schematic view of Booth multiplie

| REF.<br>PAPER   | NAME OF<br>MULTIPLIE<br>R | DELA<br>Y<br>(NS) | NO.OF<br>SLICES     | NO. OF<br>4<br>INPUT<br>LUTS | NO.OF<br>BOUNDE<br>D IOBs | DEVICE/<br>FAMILY           |

|-----------------|---------------------------|-------------------|---------------------|------------------------------|---------------------------|-----------------------------|

| Proposed design | Booth<br>multiplier       | 22.12             | 752 out of<br>46560 | -                            | 64 out of 240             | Vertex6 XC6VCX75T<br>FF84-2 |

| Proposed design | Vedic<br>multiplier       | 15.27             | 603 out of<br>46560 | -                            | 64 out of 240             | Vertex6 XC6VCX75T<br>FF84-2 |

Table I-Result of device utilization of proposed method between Booth and Vedic multiplier

| REF.<br>PAPER   | NAME OF<br>MULTIPLIE<br>R              | DELA<br>Y<br>(NS) | DEVICE/<br>FAMILY              |

|-----------------|----------------------------------------|-------------------|--------------------------------|

| [3]             | Vedic<br>multiplier<br>(HALF<br>ADDER) | 27.14             | Vertex6<br>XC6VCX75T<br>FF84-2 |

| Proposed design | Vedic<br>multiplier<br>(CSA<br>ADDER)  | 15.27             | Vertex6<br>XC6VCX75T<br>FF84-2 |

Table II-comparison of 16\*16 existing with proposed Vedic multiplier

From this table we conclude that delay required for Vedic multiplier using CSA adder is 15.27 ns is less than existing method.

## VI. ACKNOWLEDGEMENT

we would like to thanks Mr. P. R. Indurkar, Associate Professor, Electronics and Telecommunication Department, B.D.C.O.E. for his valuable suggestion .we would thanks to our college for providing facilities which helps us in our research work. We also express thanks to our parents, friends and colleagues.

## VII. CONCLUSION

The proposed Vedic and Booth multiplier is simulated using XILINX ISE 14.5. The comparison between proposed and existing multiplier is shown in table-2. From the table-1 the Vedic multiplier is superior in speed and delay than the Booth multiplier.

#### REFERENCES

[1] H.Budhiraja, M.Syed, Ms. A. Ramya, "Verilog Implementation of vedic multiplier," international journal of advancement in engineering technology, management and applied science, volume 3, Issue 5 may 2016.

[2] P. Soni, S. Kadam, "Implementation of 16\*16 bit multiplication algorithm by using vedic mathematics over booth algorithm," IRJET, eISSN:2319-1163|pISSN

[3] R. K. Bathija, R.S. Meena, "Low power high speed 16\*16 multiplier using vedic mathematics," International journal of computer applications(0975-8887), volume 59-No.6, december 2012.

- [4] Dr. K.S. Gurumurthy, M.S.Prahalad "fast and power efficient 16\*16 Array of multiplier using vedic multiplication,"

- [5] G.Vaithiyanathan, K.Venkatesan, "Simulation and implementation of vedic multiplier using VHDL code," International journal of scientific and engineering research volume 4, Issue 1, january-2013.

- [6] Rakhi Thakur and kavita khare, "High Speed FPGA implementation of FIR filter for DSP Applications," International Journal of Modeling and Optimization, vol.3,No 1,February 2013.

- [7] Mahesh Golconda and Maruti Zalte, "Comparitive analysis of Multiplier and Multiplier-less method used to implement FIR filter on FPGA," International journal of technical research and application e-ISSN:2320-8163, volume 4 Issue 3(May-June, 2016), pp.370-375.

- [8] T. D. sawarkar, Lokesh Chawle, N. G. Narole, "Implementation of 4-tap sequential and parallel Micro-programmed based Digital FIR filter architecture using VHDL," International journal of innovative research in computer and communication engineering (An ISO 3297: 2007 certified organization) vol. 4, Issue 4, April 2016.

- [9] A.R.Narasimha,K.Rajasekhar,A.SujanaRani, "Implementation of low area and power efficient architectures for Digital FIR filters," International journal of advanced research in computer science and software engineering, volume 2, Issue 8, August 2012.

- [10] Park, S.Y. and Meher, P.K. (2014) Efficient FPGA and ASIC realization of a DA-Based Reconfigurable FIR Digital filter. IEEE Transactions on circuits and systems-II: Express Briefs, 61, 511-515.

- [11] U. Meyer-Baese, G. Botella, D.E.T. Romero and Martin Kumm, "optimization of high speed pipelining in FPGA-based FIR filter design using genetic algorithm, "Proc. Of SPIE.Vol.8401,2012.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)