IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: VII Month of publication: July 2017 DOI:

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

# Simulation of a Novel Multi-Level Inverter Topology for Induction Motor Drive Applications

Ravi Kumar Kanaparthi<sup>1</sup>, Chandra Sekhar Gujjarlapudi<sup>2</sup>

<sup>1</sup>Department of Electrical and Electronics Engineering, Aravindhaksha Educational Society's Group of Institutions <sup>2</sup>Department of Electrical and Electronics Engineering, Sri Mittapalli College of Engineering

Abstract: This paper presents a novel multilevel inverter for inductor motor drive applications. The use of MLIs in medium and high power applications are increasing due to reduced voltage stress across the switches and lower total harmonic distortion (THD) of the output waveform. But the conventional MLIs requires more number of switches as the level increases for reducing the THD of the output waveform. This paper presents a new MLI inverter topology with reduced number of power electronic components. The proposed inverter produces thirteen level output voltage using only 9 switches and a diode. For generating thirteen level output voltage conventional Hbridge MLI uses 12 switches, which increase the cost as well as switching losses. This paper presents the comparison between cascaded H-bridge MLI and symmetrical and asymmetrical configuration of the proposed inverter. Finally induction motor fed from the proposed MLI is simulated in MATLAB/SIMULINK environment and the corresponding results are presented.

Keywords— Induction motor, Multilevel inverter, symmetrical configuration and Total harmonic distortion, Voltage source inverter.

#### I. INTRODUCTION

The use of induction motors (IMs) are increasing day by day in industry sector for high power applications. The main advantages of IMs are rugged in construction, easy maintenance, less cost and sufficiently high efficiency, etc. Speed control of IM requires a suitable inverter to change the voltage and frequency [1] applied to it. Normally we do two stage conversion, i.e. convert the ac power from supply mains to dc (rectification) and then it is converted to again ac (inversion) to control the speed of the machine. Generally we use a voltage source inverter (VSI) for this job. But the conventional H-bridge VSI produces a square wave output voltage waveform which contains infinite number of odd

harmonics. For getting the sine wave output we prefer PWM based inverter, but the main disadvantage of PWM inverter [2] is switching losses are high and also it is limited to low power applications. For medium and high power applications, we are using multilevel inverters (MLI) [3-6]. The main advantage of MLI is that the output voltage is almost nearer to sine wave. The other advantages of MLI are reduced dv/dt stress across the switches, and less THD. Generally multilevel inverters are categorized into three types depending upon their configuration. They are Diode clamped MLI, Flying capacitor MLI, and Cascaded H-bridge MLIs. The main problem associated with Diode

clamped MLIs [7] is that requirement of extra diodes in addition to the switches which increase the cost. In flying capacitor MLIs [8-10], control is complicated and large numbers of capacitors are expensive as the level increases. Cascaded H-bridge MLI [11] are more expensive as the level increases and also it requires separate dc sources. To overcome the above disadvantages this paper proposes a new multilevel inverter topology with fewer switches compared to conventional MLIs. Finally the induction motor fed by the proposed MLI is presented in this paper.

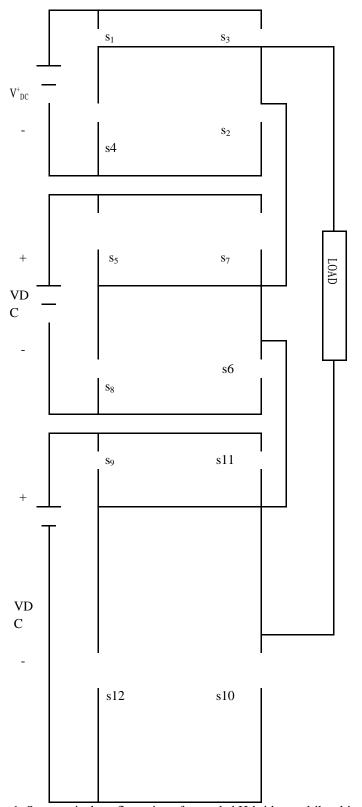

#### II. CASCADED H-BRIDGE MLI TOPOLOGY

The general structure of cascaded H-bridge multilevel inverter in symmetrical configuration is shown in the figure 1. Each Hbridge uses four switches. For N number of levels level, the no of H-bridge required is given by the following formula,

Number of levels = 2N + 1

Where,

N = number of H-bridges

Here each H-bridge is connected in series so that the outputs of each bridge are added up to get the required output level [12-13]. For generating seven level output voltage, we require three H-bridges in symmetrical configuration. So it requires 12 switches to generate seven level output voltage which increases the switching losses and cost also.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VIII, July 2017- Available at www.ijraset.com

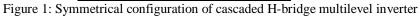

Asymmetrical configuration of cascaded H-bridge multilevel inverter is shown in figure2.

Figure 2: Asymmetrical configuration of cascaded H-bridge multilevel inverter

It requires three H-bridges with three different dc input voltages to generate thirteen level output voltage. It also uses twelve switches to get the required output voltage

which means switching losses and cost also high. To avoid the above problems this paper presents a new multilevel inverter topology with fewer switches to generate the required output voltage.

#### **III. PROPOSED MULTILEVEL INVERTER TOPOLOGY**

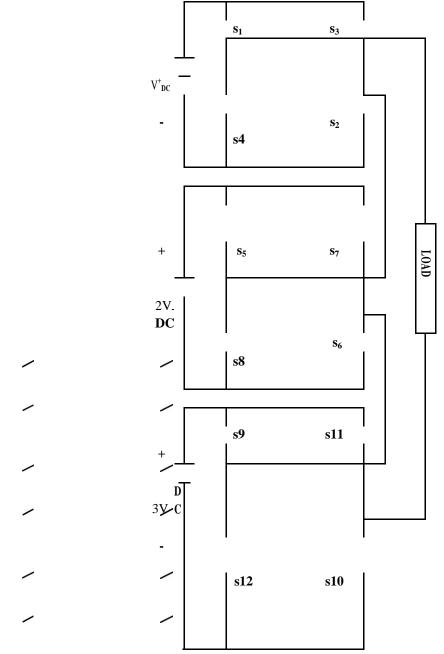

A. Symmetrical configuration

The following figure 3 shows the symmetrical configuration of the proposed MLI topology.

VDC

Volume 5 Issue VIII, July 2017- Available at www.ijraset.com

Figure 3: Symmetrical configuration of proposed multilevel inverter

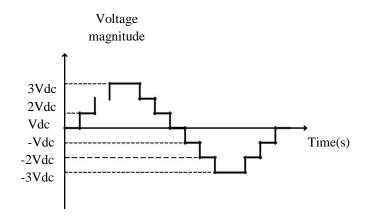

It consist of nine switches  $S_1, S_2, S_3 \dots S_{9 \text{ to}}$  achieve seven level output voltage. Compared to symmetrical configuration of cascaded H-bridge MLI (uses 12 switches), the proposed multilevel inverter topology uses less switches. Since the switches are less, the switching losses and cost are low. The following figure 4 shows the ideal waveform of seven level output voltage.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VIII, July 2017- Available at www.ijraset.com

Figure4. Ideal seven level output voltage waveform

The output voltage waveform consists of seven levels  $\pm 3$ Vdc,  $\pm 2$ Vdc,  $\pm 2$ Vdc,  $\pm d$  and 0. The following table I shows the switching pattern for the proposed MLI in symmetrical configuration.

| S1 | S2 | <b>S</b> 3 | S4 | S5 | <b>S</b> 6 | S<br>7 | <b>S</b> 8 | <b>S</b> 9 | Voltag<br>e<br>level |

|----|----|------------|----|----|------------|--------|------------|------------|----------------------|

| 1  | 1  | 0          | 0  | 1  | 0          | 0      | 1          | 0          | +Vdc                 |

| 1  | 1  | 0          | 0  | 1  | 0          | 1      | 0          | 0          | +2Vdc                |

| 1  | 1  | 0          | 0  | 1  | 0          | 1      | 0          | 1          | +3Vdc                |

| 0  | 1  | 0          | 1  | 0  | 0          | 0      | 0          | 0          | 0                    |

| 0  | 0  | 1          |    | 1  | 0          | 0      | 1          | 0          | -Vdc                 |

| 0  | 0  | 1          | 1  | 1  | 0          | 1      | 0          | 0          | -2Vdc                |

| 0  | 0  | 1          | 1  | 1  | 0          | 1      | 0          | 1          | -3Vdc                |

| Table I: Switching pa    | attern for proposed | l Symmetrical MLI |

|--------------------------|---------------------|-------------------|

| i ubie i. b wittening pt | attern for proposed | * Symmetrical ML  |

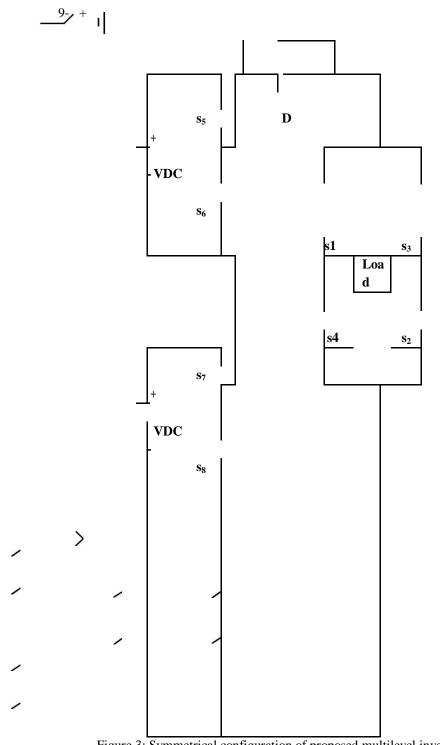

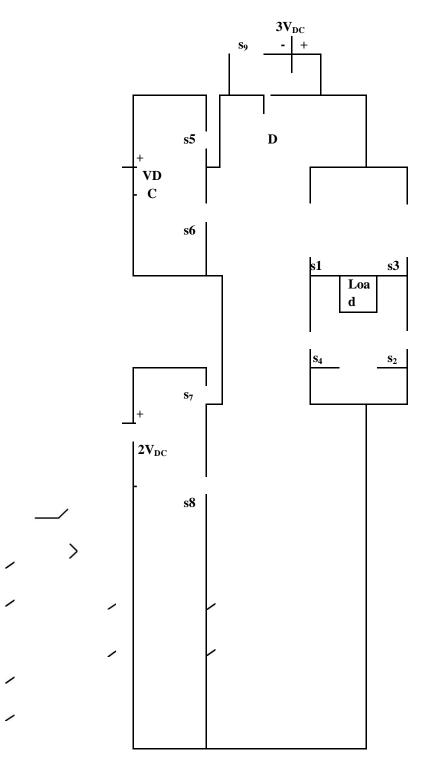

#### B. Asymmetrical Configuration

Asymmetrical configuration means the use of different dc voltage ratings. More number of levels can achieved with less number of switches is the main advantage of asymmetrical configuration. The following figure 5 shows the asymmetrical configuration of proposed multilevel inverter.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VIII, July 2017- Available at www.ijraset.com

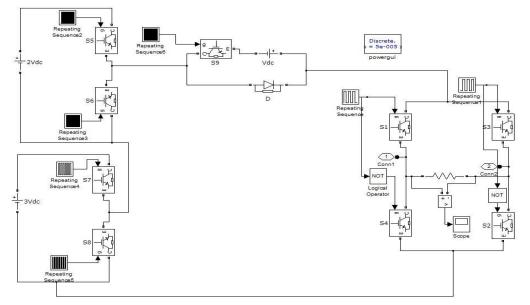

Figure 5: Asymmetrical configuration of proposed multilevel inverter

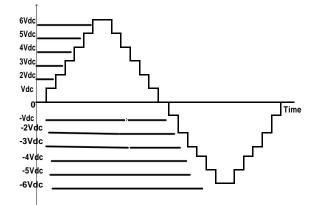

When compared to the asymmetrical configuration of cascaded H-bridge MLI, the proposed asymmetrical MLI uses only nine switches to generate thirteen level output voltage. The following figure 6 shows the ideal waveform of thirteen level output voltage.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VIII, July 2017- Available at www.ijraset.com

Figure6. Ideal thirteen level output voltage waveform

The output waveform consists of 13 levels:  $\pm$  6Vdc,  $\pm$  5Vdc,  $\pm$  4Vdc  $\pm$  3Vdc,  $\pm$  2Vdc,  $\pm$  Vdc and 0. The following table II shows the switching pattern for the proposed MLI in asymmetrical configuration. Table II: Switching pattern for proposed Asymmetrical MLI

| S1 | S2 | <b>S</b> 3 | S4 | S5 | S<br>6 | S<br>7 | S<br>8 | S<br>9 | Voltag<br>e level |

|----|----|------------|----|----|--------|--------|--------|--------|-------------------|

| 1  |    | 0          | 0  | 1  | 0      | 0      | 1      | 0      | +Vdc              |

| 1  | 1  | 0          | 0  | 0  | 1      | 1      | 0      | 0      | +2Vdc             |

| 1  |    | 0          | 0  | 1  | 0      | 1      | 0      | 0      | +3Vdc             |

| 1  | 1  | 0          | 0  | 1  | 0      | 0      | 1      | 1      | +4Vdc             |

| 1  | 1  | 0          | 0  | 0  | 1      | 1      | 0      | 1      | +5Vdc             |

| 1  | 1  | 0          | 0  | 1  | 0      | 1      | 0      | 1      | +6Vdc             |

| 0  | 1  | 0          | 1  | 0  | 0      | 0      | 0      | 0      | 0                 |

|    |    |            |    |    |        |        |        |        |                   |

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VIII, July 2017- Available at www.ijraset.com

| 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | -Vdc  |

|---|---|---|---|---|---|---|---|---|-------|

| 0 | 0 |   | 1 | 0 |   | 1 | 0 | 0 | -2Vdc |

| 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | -3Vdc |

| 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | -4Vdc |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | -5Vdc |

| 0 | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | -6Vdc |

Power electronic components required for the proposed MLI and cascaded H-bridge multilevel inverter is shown in the following table III.

Table III: Comparison between proposed MLI and cascaded H-bridge multilevel inverter in symmetrical configuration

| Type of MLI                            | Number of switches for 7-<br>level output voltage |

|----------------------------------------|---------------------------------------------------|

| Cascaded H-bridge MLI<br>(symmetrical) | 12                                                |

| Proposed MLI<br>(symmetrical)          | 9                                                 |

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VIII, July 2017- Available at www.ijraset.com

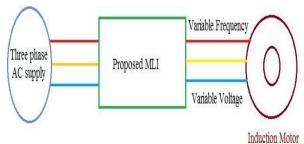

#### IV. INDUCTION MOTOR FED BY THE INVERTER

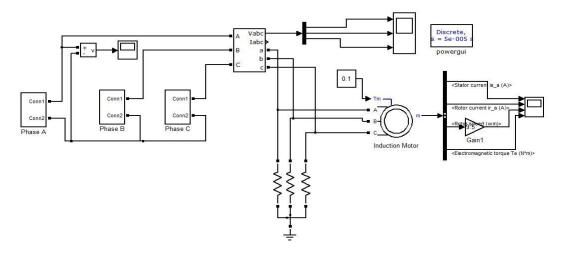

Speed control of induction motor can be achieved in three different ways. First one is to control the voltage applied to the stator of the IM, but this method gives the poor performance. Second method is to control the frequency of voltage, but this method may push the IM into saturation. In order to address the above concerns, third method known as V/F control, in which both voltage and current has to be varied. For this purpose we need an inverter to change the both frequency and voltage applied to IM. Conventional inverters can do this job, but these are having so many problems such as high THD, more switching losses and low efficiency. For eliminating the above disadvantages this paper proposes a new multilevel inverter topology. The following figure shows 7 the inverter fed induction motor.

Figure 7: Proposed MLI fed induction motor

| The following table shows the cost data for | or the proposed MLI  | [ topology and cascaded | d H-bridge MLI topology    |

|---------------------------------------------|----------------------|-------------------------|----------------------------|

| The following tuble shows the cost data it  | or the proposed with | i topology and caseaded | a ii ondge milli topology. |

|                |                      | 1 1 1                  |                  | 0 1 01             |

|----------------|----------------------|------------------------|------------------|--------------------|

|                | No of switches(IGBT) | Cost of switches(IGBT) | No of DC sources | Cost of DC sources |

| Type of MLI    |                      |                        |                  |                    |

|                | used                 | used in rupees         | Required         | Required           |

| Proposed MLI   |                      |                        |                  |                    |

|                | 9                    |                        |                  |                    |

| (Symmetrical   |                      | 9*200=1800/-           | 3                | 3*600 = 1800       |

| Configuration) |                      |                        |                  |                    |

| Cascaded H-    |                      |                        |                  |                    |

| bridge MLI     |                      |                        |                  |                    |

|                | 12                   | 12*200=2400/-          | 3                | 3*600 = 1800       |

| (Symmetrical   |                      |                        |                  |                    |

| Configuration) |                      |                        |                  |                    |

From the above table, the cost of IGBT switches used in the proposed MLI is less compared to cascaded MLI topologies, where as the cost of the DC sources is same for both the topologies.

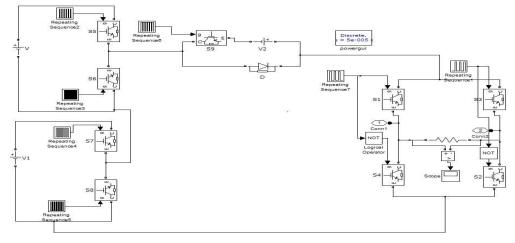

Figure8: Matlab/Simulink diagram of proposed seven level MLI in symmetrical configuration.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VIII, July 2017- Available at www.ijraset.com

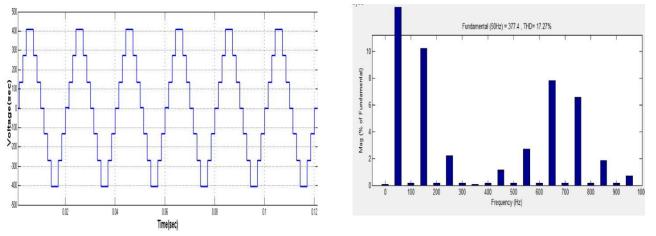

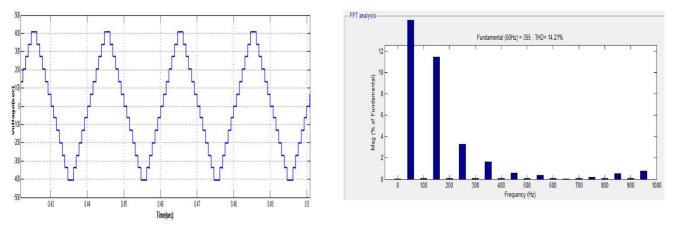

Figure9: Output voltage waveform and harmonic spectrum of proposed 7-level MLI (Asymmetrical topology)

#### V. INVERTER LOSSES

Mainly, two kinds of losses (i.e., conduction and switching losses) are associated with the switches [14]. As the switches reduced these losses are also reduced. In the proposed MLI topology, we are using nine switches which are less compared to cascaded MLI topology. Hence switching losses are less for the proposed MLI.

#### VI. SIMULATION RESULTS

Matlab/Simulink diagram of proposed seven level MLI (Symmetrical configuration) and its output voltage wave form is shown in the following figures 8 and 9. From figure 9, the wave form contains seven level output voltage and here the inverter uses nine switches. The proposed seven level MLI's harmonic spectrum is shown in figure 9 and THD value for this inverter is 17.27%. Matlab/Simulink diagram of proposed thirteen level MLI

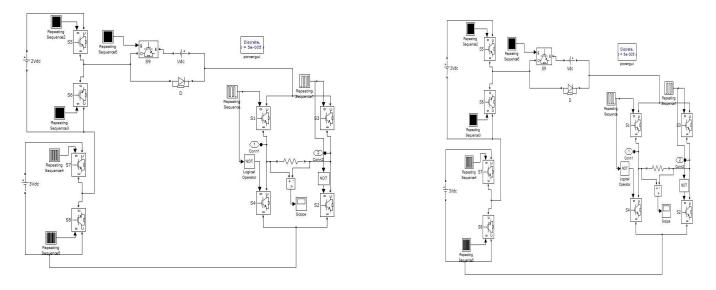

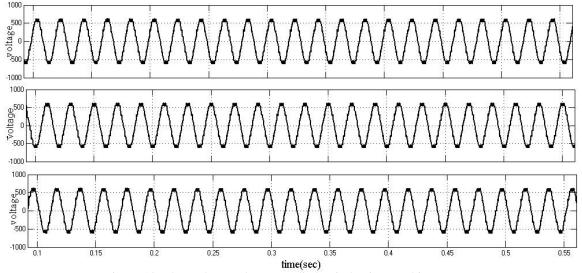

(Asymmetrical configuration) and its output voltage wave form is shown in the following figures 10 and 11. From the figure 11, the wave form contains thirteen level output voltage and here the inverter uses nine switches. The proposed thirteen level MLI's harmonic spectrum is shown in figure 11 and THD value for this inverter is 14.21%%. Finally the proposed MLI applied to a induction motor is shown in the figure 12. The corresponding waveforms (phase voltages, stator currents, rotor speed and the electromagnetic torque) are shown in the figures 13 and 14 respectively.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VIII, July 2017- Available at www.ijraset.com

figure10: Matlab/Simulink diagram of proposed thirteen level MLI in Asymmetrical configuration

Figure 11: Output voltage waveform and harmonic spectrum of proposed 13-level MLI (Asymmetrical topology)

Figure 12: Proposed MLI fed induction motor system

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VIII, July 2017- Available at www.ijraset.com

Figure 13: Three phase voltages applied to induction machine

The following table V shows the voltage and current THD content for the proposed multilevel inverter and cascaded NLI topologies.

|                    |                      | Current |

|--------------------|----------------------|---------|

| Type of MLI        | Voltage<br>THD value | THD     |

|                    |                      | value   |

| Proposed MLI in    |                      |         |

| symmetrical        | 17.27%               | 17.27%  |

| configuration      |                      |         |

| Cascaded H- MLI in |                      |         |

| symmetrical        | 18.2%                | 18.2%   |

| configuration      |                      |         |

#### VII. CONCLUSION

This paper proposes a new multilevel inverter topology for induction motor drive applications. The proposed MLI uses only nine switches in symmetrical and asymmetrical configuration to generate seven level and thirteen level output waveform respectively. As compared to conventional MLI the proposed inverter utilizes lees switches so that the switching losses and cost also is low. The proposed MLI can also used to drive the induction motor. Finally the proposed MLI feeding induction motor is proposed.

#### REFERENCES

- [1] "Modern power electronics and ac drives" by bimal k bose

- [2] Muhammad H Rashid, "Power Electronics: circuits, Devices and Applications", Pearson Education, Third Edition, 2004.

- [3] J.S. Lai and F.Z. Peng, "Multilevel Converters A new breed of power converters," Conference Record of the IEEE-IAS Annual Meeting, 1995, pp. 2348-235

- [4] M. Manjrekar and G. Venkataramanan, "Advanced topologies and modulation strategies for multilevel inverters," Conference Record of the IEEE-PESC, 1996, pp. 1013-1018

- [5] Ebrahim Babaei, Somayeh Alilu, and Sara Laali, "A New General Topology for Cascaded Multilevel Inverters With Reduced Number of Components Based on Developed H-Bridge", IEEE transactions on industrial electronics, vol. 61, no. 8, august 2014.

- [6] Y. Hinago and H. Koizumi, "A single-phase multilevel inverter using switched series/parallel dc voltage sources," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2643– 2650, Aug. 2010

- [7] -Mohan M. Renge and Hiralal M. Suryawanshi, "Five-Level Diode clamped Inverter to eliminate Common Mode Voltage and Reduced dv/dt in Medium voltage rating Induction Motor Drives, IEEE Transactions on Power Electronics, vol. 23, no.4, pp. 1598–1607

- [8] Mostafa Khazraei, Hossein Sepahvand, Keith A. Corzine, and Mehdi Ferdowsi, "Active Capacitor Voltage Balancing in Single-Phase Flying- Capacitor Multilevel Power Converters" IEEE Transactions on Industrial Electronics, VOL. 59, NO. 2, FEBRUARY 2012.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue VIII, July 2017- Available at www.ijraset.com

- [9] Dr. Obbu Chandra Sekhar Dr.K chandra sekhar Dr.G Durga sukumar, "An Enhanced DTC scheme for Induction Machine Control Fed by Seven-Level MPC Voltage Source Inverter", Journal of electrical engineering (JEE). Vol 14. No 2, Pp.180-185

- [10] Xu Lie, Jon C. Clare, Patrick W. Wheeler, Lee Empringham, and Li Yongdong, "Capacitor Clamped Multilevel Matrix Converter Space Vector Modulation" IEEE Transactions on industrial electronics, VOL. 59, NO. 1, JANUARY 2012.

- [11] Fernanda Carnielutti, Humberto Pinheiro, and Cassiano Rech, "Generalized Carrier-Based Modulation Strategy for Cascaded Multilevel Converters Operating Under Fault Conditions" IEEE Transactions on Industrial Electronics, VOL. 59, NO. 2, FEBRUARY 2012.

- [12] J. Rodriguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications," IEEE Trans. Ind. Electron., vol. 49, pp. 724 738, 2002

- [13] W. K. Choi and F. S. Kang, "H-bridge based multilevel inverter using PWM switching function," in *Proc. INTELEC*, 2009, pp. 1–5.

- [14] M. Farhadi Kangarlu and E. Babaei, "A generalized cascaded multilevel inverter using series connection of submultilevel inverters," IEEE Trans. Power Electron., vol. 28, no. 2, pp. 625–636, Feb. 2013.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)