IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 11 Issue: VIII Month of publication: Aug 2023

DOI: https://doi.org/10.22214/ijraset.2023.55260

www.ijraset.com

Call: 🕥 08813907089 🔰 E-mail ID: ijraset@gmail.com

# A Novel Spin Based Logic Circuitry Synthesis Using SS Gate

Shantanu Bhadra<sup>1</sup>, Jayanta Aich<sup>2</sup>, Suparna Karmakar<sup>3</sup>, Somnath Dey<sup>4</sup>, Sanjay Bhadra<sup>5</sup>, Soumyendu Banerjee<sup>6</sup>

<sup>1, 2, 3, 4</sup>Department of Computational Science, Brainware University, Kolkata, India 700125

<sup>5, 6</sup>Department of Electrical Engineering, Institute of Engineering and Management (Newtown campus), University of Engineering and Management Kolkata, India 700160

Abstract: Because of its perceived advantages, reversible logic has attracted a lot of study attention. It introduces commendable characteristics like low power consumption, minimized garbage output, and least propagation delay. Reversible logic integrated circuits (ICs) have been produced utilizing traditional CMOS topology in a number of published research endeavors up to this point. However, because CMOS technology is already experiencing a common scaling down issue, researchers are now focusing on post-CMOS devices for the manufacturing of reversible integrated circuits in the future. This particular research project is focused on related research projects that feature reversible IC design based on Spintronic. The authors first implemented spin-oriented conventional reversible logic gates and evaluated their effectiveness in terms of generated garbage values, power consumption, device integrity, and size. Later, in order to understand the benefits of the suggested Single Spin Logic based SS gate, the authors come across an SS gate that is singular in its kind and stick to its spin realization.

Index Terms: Reversible Logic; SS Gate; Single Spin Logic; Garbage Value; Low Power Consumption.

#### I. INTRODUCTION

Embryonically, Reversible Logic [12] geared exclusive curiosity in terms of Low Dimensional Structures (LDS). The promising esteems of reversible circuitry corroborates the notion of loss less information processing [17, 22, 29, 30-31], low power consumption, low power dissipation, high speed computing and least garbage value generation. Counting on these integrities Researchers strove Feynman, Double Feynman, Toffoli, Fredkin, Peres gates [15] and so on. To pace up with robust [18] technologies Researchers concurrently initialized several subsets such as multiplier [3] using Peres gate, adder [14] using DKG gate, binary to gray converter [10] using Feynman gate, ALU [33] using Feynman, Peres and Fredkin gate and so on. The goodliness of reversible topology [16] was soon benchmarked with its traditional counterpart. One imperative precondition is the elimination of garbage value. This in particular reduces the heat dissipation and power consumption. The quantum cost is an annexed feature of reversible logic which is largely pondered over. Categorically reversible logic circuitry is now enormously scaled to foster future ready computational ICs [19-21, 23-28], RAM, ROM, ASICs and FPGAs. Nonetheless the reversible circuits are comprised of CMOS composite materials and being indebted to intrinsic limitations of CMOS technology, the MOSFET reversible circuitry suffers the pitfall of scaling limitations. But contemporary research articles exhibit countless strives to ratify the scaling limitations of CMOS [5].

Spintronics is one such post CMOS versatile technology that discourse the obscurities of CMOS scaling. It preserves both intrinsic spin of electron and its conjoined magnetic momentum keeping aside the elementary charge of an electron. It indeed exercise maneuvering electron in metal, semiconductors and in heterostructures. Thus spin positioned information processing incorporates a stipulated technology to inject, store, control and manipulate information with the span of spin degree of freedom. Several spin based device proposal fortified spin based circuit realizations and logicalizations including Single Spin Logic (SSL) [32]. These elements mark the dawn of spintronics era.

The authors here realized reversible logic circuitry under the daybreak of SSL and subsequently ventured into a new paradigm of SSL reversible circuitry. Erstwhile the authors have reported such SSL reversible circuitry. In furtherance to such pain sticking endeavor here the authors put forward few noteworthy SSL reversible logicalizations and subsequently tender SSL SS gate and confer its modus operandi.

Accordingly, the authors adhere to SSL SS gate based Half adder and Full adder and outline the attributes of the modeled combinational circuits in terms of garbage value, power consumption, device integrity, robustness, heat dissipation and eventually the 'no requirement' of interconnections.

International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 11 Issue VIII Aug 2023- Available at www.ijraset.com

# II. THE ORTHOGONALITY OF SPIN REVERSIBLE LOGICALIZATION

The intrinsic spin of an electron steadfast two spin set i.e. spin up ' $\uparrow$ ' and spin down ' $\downarrow$ '. This two existing non-degenerate orthogonal spin state are ultimately parallel and anti-parallel to the magnetic field and mutually they encode classical bit '1' and '0'. The closest adjoining spin exchange information endowing a three phase clock is fed in unidirectional to the signal flow from input to output. This favors spintronics from conventional physical charge based devices and profoundly dissipates low or no heat even at higher processing speed. The spin degree of freedom in associations to spin interaction is customized for encoding qubit in quantum logic gates. This covalent structure enthuse SSL which detects and controls spin degree of freedom exchange amid ferromagnetic metallic or ferromagnetic semiconductor hetero-structures. Robustly SSL expanded plentifully to be seized in a quantum dot and substantial research has been reported so far to marshal spin in a low magnetic field. SSL based NAND gates (Agarwal et.al), Full Adder (S. Shukla et.al.), Multiplexer (T.K. Bhattacharyya) are designed beforehand [7]. To attain akin pinnacles authors here implement SSL know-how in BJN Gate [9], TR Gate [4], R Gate [2], MUX Gate [13], New Gate [1], NFT Gate [11] and SS Gate [6].

#### III. ARTICULATION OF SSL IN REVERSIBLE LOGIC DOMAIN

Spin composed electronic research quantized information processing in nano devices. Prior to this work the authors have proposed SSL based Reversible logic circuits as demonstrated in [8]. Authors here chronologically report the novel architectures of SSL synthesized other few notable Reversible Logic Gates (RLG) in which green arrow indicates the input and blue arrow provides the output.

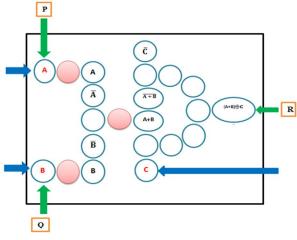

#### A. BJN Gate

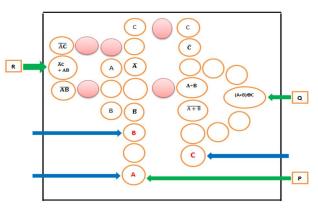

Fig. 1 is the SSL realization of  $3\times 3$  BJN gate with three inputs (A, B, C) and three outputs given by P=A, Q=B,  $R=(A+B) \oplus C$ , respectively. It's quantum cost is 5 and the Garbage Value is limited to zero.

Fig. 1. SSL based BJN gate.

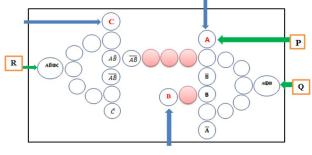

#### B. TR Gate

Fig. 2. is another  $3\times3$  SSL based TR Gate having inputs A,B,C and its corresponding outputs are P = A,  $Q = A \oplus B$ ,  $R = AB \oplus C$ . It has Quantum Cost 6 and the garbage value is limited to zero.

Fig. 2. SSL based TR gate.

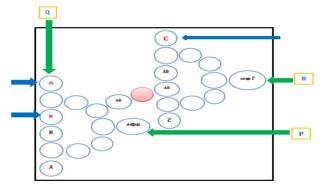

#### C. R Gate

Apart SSL-BJN and SSL-TR gate, R gate is a crucial  $3\times3$  reversible gate and its SSL realization is shown in Fig. 3. This gate is generally commissioned to invert a signal and also to duplicate a signal. The inputs are (A, B, C) and outputs are  $P=A\oplus B$ , Q=A,  $R = AB \oplus C$  Similar to prior gates the R gate does not possess any garbage value.

Fig. 3. SSL based R gate.

#### D. MUX Gate

Fig. 4 shows  $3\times 3$  MUX Gate having inputs (A, B & C). The outputs are expressed by  $P=A, Q = A \oplus B \oplus C$ ,  $R = \overline{A}C + AB$  in SSL domain and its Quantum Cost is 4. It produces merely 2 garbage values.

### E. New Gate

The New gate is a 3×3 Gate shown in Fig. 5. The inputs are (A, B, C) and outputs are  $P=A, Q = AB \oplus C$ ,  $R = \overline{A}\overline{C} \oplus \overline{B}$ . The fragility of this gate is that its Quantum Cost is still unknown. Its garbage value is limited to one.

Fig. 5. SSL based New gate.

International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538 Volume 11 Issue VIII Aug 2023- Available at www.ijraset.com

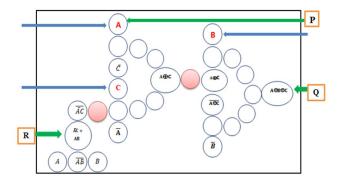

F. NFT Gate

Noval Fault Tolerant or NFT reversible gate is a 3×3 reversible gate shown in Fig. 6. The inputs are given by (A, B, C) and outputs are taken as  $P = A \oplus B$ ,  $Q = \overline{B}C + A\overline{C}$ ,  $R = BC + A\overline{C}$ . Its Quantum Cost is 5 and the garbage value is two.

The credentiality of such RLGs are largely co-related to fundamental of spin. In order to disseminate the garbage value enough care is taken upon in realizing the SSL RLG circuits. Eventually the authors with the cost for highest accuracy in reversibility proposed SS gate and its nobilities are low quantum cost, production of less garbage value, high processing and other few merits. Basically the authors resonate an amicable model that is to be incorporate in future ICs [34].

#### IV. SS SPIN GATE REALIZATION

This is a new reversible gate named after first letter of the authors' name. This is a  $3\times3$  reversible gate. Primarily the authors conclave a stochastic approach and substantiate the model with its CMOS counterpart.

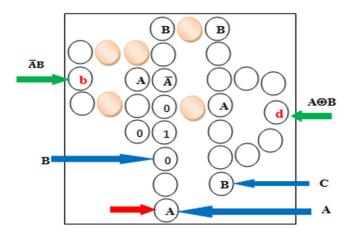

Fig. 7. SS gate in SSL domain.

The SSL realization of SS model is shown in Fig. 7. It has inputs A, B, C and outputs P = A,  $Q = A \oplus B \oplus C$ ,  $R = \overline{A}C + AB$ .

Now to validate SS gate the Half adder, Half subtractor and 1-bit comparator are devised and then after introspection of the attributes of the designed Half adder, Half subtractor and 1-bit comparator are compared with their conventional counterpart. The main advantage of this gate is it can work as a half subtractor if one of the input is turned to zero as shown in Fig. 8. Here the garbage value is maximized to 'one' only as JMS gate itself upholds all the requisite criterion itself of the Half subtractor marked by red arrow.

#### V. CONCLUSION

The authors earlier analytically studied the approximation of SSL in the reversible vicinity. This particular research endeavor is a frame work to deliberate the notion of SSL in variety of reversible circuitry and above all the proposed SS gate is realized using SSL to perpetuate the heterogeneity of spin degree of freedom. The linearity of such model is bestowed upon the physiognomies of spin structure in ferromagnetic metal as well as in ferromagnetic semiconductor.

The inheritance of such circuits is vested upon the users' proficiency in improvising spin in the nano region. Moreover, the comparative analysis postulate all benevolence of spin technology uninterruptedly and uncompromisingly.

Fig. 8. SS gate based SSL Half Subtractor.

Thus the authors adhere to such reversible logic invention using spin topology and anticipate to maximize its incorporation for future elegant solution of the dead end of CMOS. Lastly the authors acknowledge this specific research maneuver as a fascinating but challenging series of action.

#### REFERENCES

- [1] B. Dehghan, A. Roozbeh, J. Zare, "Design of low power comparator using DG gate", Sci. Resea. Cir. and Sys., vol. 5, pp. 7-12, 2014.

- [2] Dilip P. et al., "Reversible-logic design with online testability", IEEE Trans. Instrum. Meas, vol. 55, April 2006, pp. 406-414.

- [3] H. R. Bhagyalakshmi, M. K. Venkatesha, "An improved design of a multiplier using reversible logic gates", Intern. J. Eng. Sc. Tech., vol. 2, pp. 3838-3845, 2010.

- [4] H. Thapliyal and N. Ranganathan, "A New Design of The Reversible Subtractor Circuit", in proc. of 11th IEEE Intern. Conf. Nano., USA, pp. 1430-1435, 2011.

- [5] H.-S.P. Wong, D.J. Frank, P.M. Solomon, "Nanoscale CMOS", IEEE Proc., vol. 87, no.4, pp. 537-570, 2002.

- [6] J. Gope, et al., "A hypothetical approach of designing novel reversible combinational logic", IOSR J. Mech. Civ. Eng., pp. 16-19, 2016.

- [7] J. Gope, S. Chowdhury (Kolay), "Exploration of Single Spin Logic (SSL) Based Expandable Hardware Design," Intern. J. Sci. Eng. Resea., vol. 7, no. 4, pp. 146-148, 2016.

- [8] J. Gope, S. Mondal, M. Kundu, S. Chowdhury (Kolay), S. Bhadra, Mahuya Panda, "Single Spin Modelling of Reversible Logic Gates", Springer, in press.

- [9] Jayashree H V, Nagamani A N, Bhagyalakshmi H R, "Modified Toffoli gate and its applications in designing components of reversible arithmetic and logic unit," Intern. J. Adv. Resea. Comp. Sci. Soft. Eng., vol. 2, pp. 207-210, 2012.

- [10] K. Kamani , S.Koneti , U. Bollampalli and S. Shankara, "Energy efficient reversible logic design for code converters", Intern. J. Resea. App., vol. 1, pp. 132-136, 2014.

- [11] M. S. Islam, et al., "Synthesis of Fault Tolerant Reversible Logic Circuits," in proc. of IEEE Cir. Sys. Intern. Conf. Test. Diag., pp. 1-4, 2009, China.

- [12] P. R. Yelekar, S, S. Chiwande, "Introduction to reversible logic gates & its application," 2<sup>nd</sup> Nation. Conf. Inform. Comm. Techn., Proceedings published in Intern. J. Comp. App. Proc., pp. 5-9, 2011.

- [13] P. Singhla, N. K. Malik, "Reversible programmable logic array (RPLA) using Feynman & MUX gates for low power industrial application", in proc. of 1<sup>st</sup> Intern. Conf. Inno. Adv. Inform. Comm. Tech., pp. 411-419, 2012.

- [14] Patel Fenil S., Tarunkumar C. Lad, "VHDL implementation of 4-bit full adder using reversible logic gates", Intern. J. Sci. Resea. Dev., vol. 1, pp. 2279-2283, 2013.

- [15] R. Garipelly, P. M. Kiran, A. S. Kumar, "A review on reversible logic gates and their implementation", Intern. J. Emerg. Techn. Adv., vol. 3, pp. 417 -423, 2013.

- [16] S. Banerjee and G. K. Singh, "A new approach of ECG steganography and prediction using deep learning," Biomed. Sig. Proc. Cont., vol. 64, 102151, 2020.

- [17] S. Banerjee and G. K. Singh, "A new real-time lossless data compression algorithm for ECG and PPG signals," Biomed. Sig. Proc. Cont., vol. 79, 104127, 2022.

- [18] S. Banerjee and G. K. Singh, "A Robust Bio-signal Steganography with Lost-data Recovery Architecture using Deep Learning," IEEE Trans. Instrum. Meas., vol. 71, pp. 1-10, 2022, Art no. 4007410, 2022.

- [19] S. Banerjee and G. K. Singh, "Agent-based beat-by-beat compression of 12-lead electrocardiogram signal using adaptive Fourier decomposition," Biomed. Sig. Proc. Cont., vol. 75, 103628, 2022.

- [20] S. Banerjee and G. K. Singh, "Deep neural network based missing data prediction of electrocardiogram signal using multiagent reinforcement learning," Biomed. Sig. Proc. Cont., vol. 67, 102508, 2021.

- [21] S. Banerjee and G. K. Singh, "Monte Carlo Filter based Motion Artifact Removal from Electrocardiogram Signal for Real-time Telecardiology System, " IEEE Trans. Instrum. Meas, Vol. 70, 4006110, 2021.

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 7.538

Volume 11 Issue VIII Aug 2023- Available at www.ijraset.com

- [22] S. Banerjee and G. K. Singh, "Quality Aware Compression of Multilead Electrocardiogram Signal using 2-mode Tucker Decomposition and Steganography," Biomed. Sig. Proc. Cont., vol. 64, 102230, 2020.

- [23] S. Banerjee and G. K. Singh, "Quality Guaranteed ECG Signal Compression using Tunable-Q Wavelet Transform and Möbius Transform based AFD," IEEE Trans. Instrum. Meas., vol. 70, 4008211, 2021.

- [24] S. Banerjee and G. K. Singh, "Comparative Study on R-peak Detection over Noisy and Denoised ECG Signal using Wavelet Transform," in proc. of 2021 Third Intern. Conf. Invent. Res. Comp. App. (ICIRCA), 2021, pp. 659-663, India.

- [25] S. Banerjee and G. K. Singh, "Feedback Control Topology of n-DOF Robotic Manipulator and Optimal Positioning of End-Effector using PSO," in proc. of 2020 IEEE Appl. Sig. Proc. Conf. (ASPCON), 2020, pp. 41-45, India.

- [26] S. Banerjee et al., "Arduino UNO and GSM Based Real-Time Home Security System Using Self-Generated Password Protection", Intern. J. Sci. Resear. Public., vol. 9, no. 4, pp. 177-181, 2019.

- [27] S. Banerjee, D. Das, S. Bhadra, & D. Ghosh, "Arduino Uno and Bluetooth based Speed Control of DC Stepper Motor with Reduced Jerking Level," Intern. J. Inn. Sci. Res. Tech., vol. 7, no. 9, pp. 596-599, 2022.

- [28] S. Banerjee, et al., "Real-Time Monitoring and Control of Consumed Power for Household Appliances using Arduino Uno through Bluetooth and Android Application," in proc. of IEEE 3rd Intern. Conf. Tre. Elec. Infor., pp. 529-533, 2019, Indi.

- [29] S. Banerjee, R. Gupta, J. Saha, "Compression of Multilead Electrocardiogram Using Principal Component Analysis and Machine Learning Approach," in proc. of IEEE App. Sig. Proc. Conf., pp. 24-28, 2018, Kolkata, India

- [30] S. Banerjee, "A First Derivative Based R-Peak Detection and DWT Based Beat Delineation Approach of Single Lead Electrocardiogram Signal," in proc. of IEEE Region 10 Symposium (TENSYMP), Kolkata, India, 2019, pp. 565-570.

- [31] S. Banerjee and G. K. Singh, "A New Moving Horizon Estimation Based Real-Time Motion Artifact Removal from Wavelet Subbands of ECG Signal Using Particle Filter", J. Sign. Process. Syst., 2023. <u>https://doi.org/10.1007/s11265-023-01887-3</u>

- [32] S. K. Sarkar et al., "Spintronics device based power efficient VLSI chip design for universal code converter", Canad. J. P. Appl. Sci., SENRA Academic Publishers, Burnaby, British Columbia, vol. 2, pp 595-600.

- [33] S. Mamataj, B. Das, A. Rahaman, "An optimized realization of ALU for 12-operations by using a control unit of reversible gates", Intern. J. Adv. Resea. Comp. Sci. Soft. Eng., vol. 4, pp. 496-502, 2014.

- [34] S. Bhadra, S. Banerjee, S. Das, H. Mukherjee, & S. Mukherjee, "Smart implementation of SS Hybrid Single Electron Model and its simulation using MATLAB," Intern. J. Res. App. Sci. Eng. Tech., vol. 10, no. 9, 2022, pp. 1361–1364.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)