# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: X Month of publication: October 2017

DOI: http://doi.org/10.22214/ijraset.2017.10180

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

### Crosstalk Analysis In Carbon Nanotube Bundle Interconnects

Parthivi Vyas<sup>1</sup>, Anup kumar<sup>2</sup>

<sup>1,2</sup>Department of Electronics & Communication Engineering, Ajay Kumar Garg Engineering College, Ghaziabad

Abstract: With the advanced technology nodes, huge number of functionalities is integrated in a Very Large Scale Integration (VLSI) chip. Thus, the density of long interconnects is increased exponentially that connect millions of active devices on a chip, is posing a serious bottleneck in terms of substantial capacitive and inductive couplings. Hence there appears a dire need to search a potential material for future generation of VLSI interconnects that will be capable of exhibiting minimized propagation delay, power dissipation and crosstalk effects. Many researchers show that carbon nanotubes are the best promising candidates for next generation of VLSI interconnect. Carbon nanotubes are preferred over copper interconnect due to their high current carrying capacity and high thermal conductivity. The present work explores the possibilities of alternative interconnect material for future VLSI interconnects. The most promising alternative for copper interconnects turns out to be Carbon Nanotube (CNT). An investigation of the control of crosstalk induced noise voltage (functional crosstalk noise) in capacitively coupled interconnects of SWCNT bundle, at the far-end of victim line, for fixed pitch and varying interconnect dimensions at 22nm technology node, have been carried out. A similar analysis is performed for copper interconnects. Result reveals that, compared to SWCNT bundle interconnects, copper interconnects has higher coupled noise voltage levels.

Keywords: Carbon nanotube, Very large scale integration, Copper, Single wall carbon nano tube, Crosstalk.

### I. INTRODUCTION

Interconnects are the metal wire that is accustomed connect element on a VLSI chip, to attach multiple structures on a system board. It controls noise, reliability, timing, design, functionality and power.

Fig.1 Carbon nanotube

Carbon nanotubes (CNTs) are carbon molecules with cylindrical shape having properties such as great mechanical, thermal, chemical, and electrical properties. They are best field emission emitters, 100 times stronger than steel and can withstand a current density of more than  $10^{10}$  A/cm<sup>2</sup>.[4]

Carbon nanotubes are of two types: single-walled carbon nanotubes (SWCNTs) and multi-walled carbon nanotubes (MWCNTs). SWCNTs were discovered in 1993, having a diameter nearly 1 nm and length thousand times larger and of the order of centimeters. The structure of SWCNT can be anticipated by bundling a thick layer of graphite into a consistent cylinder. The way the graphene sheets wrap can be

denoted by a duo of indices (n, m) named as chiral vector. The relationship between n and m defines the three categories of CNTs namely, zigzag, chiral, and arm chair.

MWCNTs consist of several layers of graphite rolled in to form a tube with an interlayer spacing of 3.4 Å. The outlying diameter of MWCNTs ranges from 1 to 50 nm while the inner diameter is of few nanometers.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 5 Issue X, October 2017- Available at www.ijraset.com

### II. EQUIVALENT CIRCUIT MODEL FOR AN ISOLATED SINGLE WALLED CARBON NANOTUBE (SWCNT)

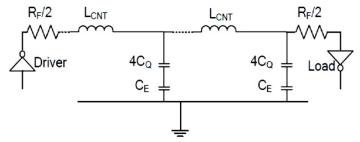

Fig.2 Equivalent circuit model for an isolated SWCNT

A. The equivalent circuit model for an isolated single-walled

CNT is shown schematically in Figure 2

- 1) R<sub>F</sub> is the fundamental resistance,

- 2) L<sub>CNT</sub> is the total inductance,

- 3) C<sub>E</sub> is electrostatic capacitance

- 4) C<sub>Q</sub> is quantum capacitance

The fundamental resistance R<sub>F</sub>, is equally divided among the two contacts on both side of the nanotube. It can be given as

$$R_F = \frac{h}{4e^2}$$

- B. The total capacitance of a nanotube consists of two component

- 1) Electrostatic capacitance (C<sub>E</sub>)

- 2) Quantum capacitance (C<sub>0</sub>)

Electrostatic capacitance is the intrinsic plate capacitance of an isolated carbon nanotube, whereas the quantum capacitance accounts for the electrostatic energy stored in the CNT when it carries current.

$$C_E = \frac{2\pi \epsilon}{\ln \frac{y}{d}}$$

$$C_Q = \frac{2e^2}{hV_f}$$

Here y is distance of CNT from ground plane,  $V_F$  is Fermi velocity in graphite (8 × 10<sup>5</sup> m/s),  $\epsilon$  is dielectric permittivity, and d is CNT diameter.

- C. The total inductance of a CNT consists of two components

- 1) Magnetic inductance (L<sub>M</sub>)

- 2) Kinetic inductance (L<sub>K</sub>)

The magnetic inductance per unit length is given by:

$$L_M = \frac{\mu}{2\pi} \ln \frac{y}{d}$$

Apart from magnetic inductance, another inductive component exists due to the kinetic energy of the electrons. The kinetic inductance per unit length can be give as [4]

$$L_K = \frac{h}{2eV_f}$$

### III. EQUIVALENT CIRCUIT MODEL OF COPPER INTERCONNECT

The resistance of the copper interconnects of length L is given by following equation

$$R = \frac{\rho l}{wt}$$

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 5 Issue X, October 2017- Available at www.ijraset.com

Where,  $\rho$  is the resistivity of material (in  $\Omega$ -m), l is the length of interconnect w is the width of interconnect and t is the thickness of interconnect. The total effective capacitance of the copper interconnect is given by

$$C_g = \epsilon \left[ \frac{W}{h} + \left\{ 2.22 \left( \frac{S}{S + 0.7h} \right)^{3.19} \right\} + \left\{ 1.17 \left( \frac{S}{S + 1.51h} \right)^{0.76} \left( \frac{t}{t + 4.53h} \right)^{0.12} \right\} \right]$$

Where E is the dielectric permittivity, s is the inter wire spacing of copper. Inductance associated with copper interconnect is given by

$$L_{s} = \frac{\mu_{0}I}{2\pi} \left[ \ln \frac{2I}{w+t} + \frac{1}{2} + \frac{0.22(w+t)}{I} \right]$$

Where  $\mu_0$  is the permeability.

### IV. CROSSTALK ANALYSIS

Crosstalk effect between coupled interconnects becomes increasingly valuable in a VLSI chip as technology advances to Giga Scale Integration (GSI) level. This is due to the fact that the interconnect density has grown and dimensions have shrunk, as the chip size increases in scaled Deep submicron (DSM) CMOS technologies. These wires do not scale in length with technology scaling and parasitic impedance parameters of these wires increase with the length of interconnects. The parasitic impedance parameters of interconnect and device depend on materials, geometry and technology. Hence, the long interconnects pose severe challenges viz. crosstalk, delay and power dissipation for high performance VLSI design.

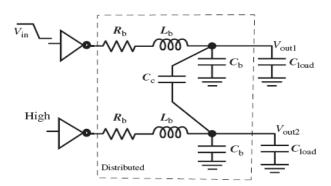

Fig.3 CMOS gate driven capacitive coupled interconnects

The above circuit parameters and coupling capacitance of coupled interconnect of copper are calculated by appropriate use of the expressions from Equations and data obtained from Table1. For overshoot analysis, the victim net (i.e. the crosstalk affected net) is kept fixed at logic 1 and the aggressor net (i.e. the net that cause crosstalk on victim) is switched from logic  $1\rightarrow 0$ . The aggressor line CMOS driver has pMOS width  $(W_p)$  double than nMOS width  $(W_n)$  while the victim line is grounded at the input through a linear region equivalent driver resistance and the size of CMOS driver nMOS is set to the minimum size of transistor. In this analysis, the width (w) and thickness (H) of interconnect are assumed to be 32nm and 96nm respectively, and space(s) between two interconnect is assumed to be 32nm.

The simulation for interconnects are carried out on Tanner EDA tool at 22nm technology at 1GHz frequency. We analyzes how crosstalk noise voltage (functional crosstalk noise) in capacitively coupled Single Walled Carbon Nanotube (SWCNT) bundle interconnects, at the far end of victim line, is controlled under the influence of interconnect dimensions such as space(s) and width(w) for fixed pitch, using proposed inter coupling capacitive model. A similar analysis is performed for copper based interconnect and comparison is made with result obtained for CNT based interconnect at 22nm technology. The SPICE simulation results reveal that the crosstalk noise voltage level at the far end of victim line in CNT bundles is significantly low compared to that in conventional metal(copper) conductors in three different cases to keep the pitch (s+w) fixed but varying the value of interconnect spacing and width.

Case-1: Space (s) between two interconnect equals to s + w/2 = (3w)/2 = 48nm and Width (w) = w - w /2 = w/2 = 16nm.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue X, October 2017- Available at www.ijraset.com

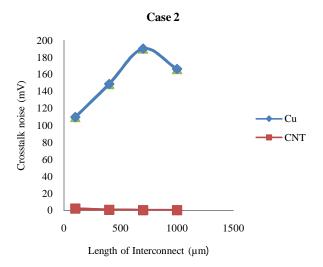

Case-2: Space (s) between two interconnect equals to 32nm and Width (w)=32nm.

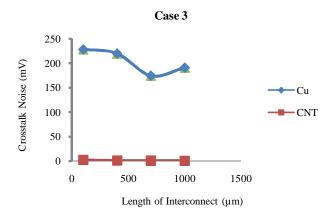

Case-3: Space (s) between two interconnect equals to s - (w/2) = w/2 = 16nm and Width (w) = w + (w/2) = 3w/2 = 48nm.

In all three cases pitch (s + w) is kept fixed at 64nm but interconnect dimensions are varied. Data given in Table1 are used for the calculations of Resistance, Induction, Capacitance and coupling capacitance for CNT and Cu.

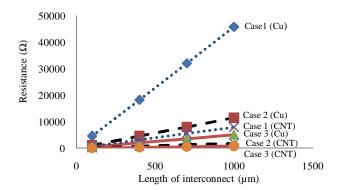

Fig.4 Variation of resistance as a function of interconnect length at different dimension between adjacent interconnects for 22nm technology.

The above fig.4 shows how the resistance varies with interconnect length for three different dimensions. It can be seen that interconnect of larger width in case 3, when used as interconnect will have smaller line resistance for both CNT and copper. It shows that in various length and width of interconnects the resistance of bundle SWCNT is several times lower than that of copper based interconnects.

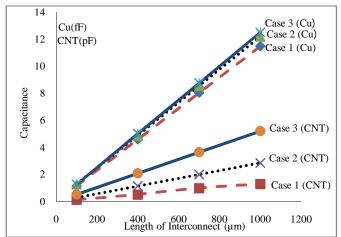

Fig.5 Variation of capacitance as a function of interconnect length at different dimension between adjacent interconnects for 22nm technology.

Fig.5 shows the variation of total interconnect effective capacitance (equivalent ground capacitance) as a function of interconnect length for different adjacent interconnects dimension. Interconnect capacitance increases with decrease in space between adjacent interconnects and decreases with scaled down dimensions.

It is observed that a bundle composed of tubes has larger effective capacitance in all three cases compared to the copper based interconnect. Since, the cylindrical surface area of the CNTs at the edge of a bundle exposed to the surrounding interconnects is larger than the corresponding surface area for a copper (Cu) interconnect with straight edges. Therefore SWCNT bundle has larger effective capacitance as compared to copper of equivalent dimension.

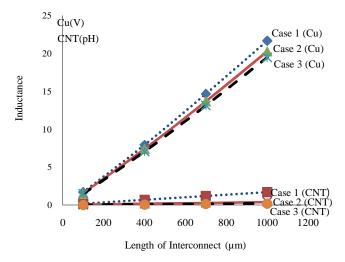

Fig.6 illustrates the dependence of inductance on interconnect length. Inductance increases with increase in space between interconnects and decreases with increase in width of interconnects in all three cases. It has been observed that a bundle composed of tubes has smaller inductance in all three cases as compared to copper.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887

Volume 5 Issue X, October 2017- Available at www.ijraset.com

Fig.6 Variation of Inductance as a function of interconnect length at different dimension between adjacent interconnects for 22nm technology.

Results are obtained in Fig.4, 5 and 6 indicate that a densely packed interconnects have larger capacitance but reverse is true for inductance and resistance.

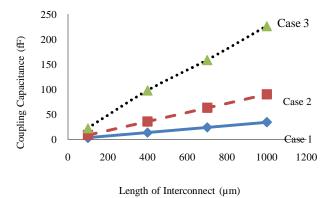

Fig.7 Variation of coupling capacitance as a function of interconnect length at different dimension between adjacent interconnects. Fig.7 shows how inter coupling capacitance between adjacent interconnects vary as a function of interconnect length for three different dimensions. Coupling capacitance increases with decrease in space between adjacent interconnects and decreases with scaled down the width of interconnects. Coupling capacitance increases significantly with increase in length of interconnect. Results also reveal that copper based interconnect has higher value of coupling capacitance than a CNT bundle counterpart in three different cases.

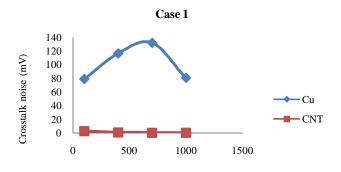

Table 6.5 Comparison between the crosstalk noise of Cu and CNT. Length of interconnect=1mm, C<sub>Load</sub>=0.14fF, Technology:22nm

| Interconnect | Coupling  | COPPER | CNT   |

|--------------|-----------|--------|-------|

| Dimensions   | Capacitor | (mV)   | (mV)  |

| Case 1       | 0.034pF   | 80.76  | 0.205 |

| Case 2       | 0.0903pF  | 166.37 | 0.219 |

| Case 3       | 0.227pF   | 190.99 | 0.191 |

The table 2 also provides an account of crosstalk noise voltage corresponding to three different cases of copper coupled interconnects.

As compared to SWCNT bundle interconnect for all three cases, copper has higher coupled noise voltage levels due to larger value of coupling capacitance as shown in Fig.7.

Length of Interconnect (µm)

Fig. 8 Crosstalk noise voltage as a function of length for different interconnect

Fig. 9 Crosstalk noise voltage as a function of length for different interconnect

Fig. 10 Crosstalk noise voltage as a function of length for different interconnect

Fig. 8, 9 and 10 shows the comparison of crosstalk noise for copper and CNT bundle interconnect for L segment RLC. It reveals that crosstalk noise in the case of CNT bundle interconnect is much less than the copper interconnect which means that CNT bundle introduces less noise than copper interconnect and gives better performance.

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887

Volume 5 Issue X, October 2017- Available at www.ijraset.com

### V. CONCLUSION

The control of crosstalk induced noise voltage (functional crosstalk noise) in capacitively coupled interconnects of SWCNT bundle, at the far-end of victim line, for fixed pitch and varying interconnect dimensions under three different cases, for the proposed inter coupling capacitance model and the conventional model, at 22nm technology node, have been analyzed. It has been observed that the proposed model of coupling capacitance provides better reduction in crosstalk noise voltage compared to conventional counterpart in all three different cases. A similar analysis performed for copper interconnects showed that, compared to coupled interconnects of SWCNT bundle, copper interconnects has higher coupled noise voltage levels due to larger coupling capacitanceFurthermore, a comparative analysis of the effect of interconnect resistance, self inductance and ground capacitance of interconnect on positive coupled peaks at the far end of victim line in capacitively coupled interconnects of SWCNT bundle and copper has been studied. It is observed that, with increase in line resistance or ground capacitance, while the noise voltage peak reduces for both CNT and copper, there are more noise voltage peaks in the copper.

### VI. FUTURE SCOPE

This work can continue in many different directions, Crosstalk and variation effects must be considered in designing the circuitry. New novel device and advanced circuit technologies enhance the performance while reducing power. The system's impact of these devices should be investigated. Resistivity of copper increases due to effect of electro migration and surface scattering in deep submicron technologies. To overcome these problems various alternative are used, but carbon nanotubes are found to be better alternative than copper interconnect. It is believed that CNT shall outperform copper interconnects in near future.

### REFERENCES

- [1] Krishna C. Saraswat, 1982,"Effect of scaling of interconnection on the time delay of VLSI circuits", IEEE Journal of solid state circuits, Vol. SC-17, No. 2, pp. 275-280.

- [2] Takayasu. Sakurai and A. R. Newton, 1990,"Alpha power law MOSFET model and its application to CMOS inverter delay and other formula", IEEE journal of solid state circuit, Vol. 25, No. 2, pp. 584-94.

- [3] Takayasu Sakurai, 1993, "Closed from expressions for interconnection delay, coupling and crosstalk in VLSI's", IEEE transactions on electron devices, Vol. 40, No. 1, pp. 118-124.

- [4] H.B.Bakoglu, James D. Meindl, 1985, "Optimal Interconnection Circuits For VLSI", IEEE transaction on electron devices, Vol. ED-32, No. 5, pp. 903-909.

- [5] Shyh-Chyi Wong, Gwo-Yann Lee, and Dye-Jyun Ma, 2000, "Modeling of Interconnect Capacitance, Delay, and Crosstalk in VLSI", IEEE transactions on semiconductor manufacturing, Vol. 13, No. 1, pp. 108-111.

- [6] George Deltoro, Nagib Sharif, 1999, "Copper Interconnect: Migration or Bust", IEEE transaction on electronics manufacturing technology symposium, Vol , No. , pp.

- [7] Paul L. McEuen, Michael S. Fuhrer, and Hongkun Park, 2002, "Single-walled carbon nanotube electronics", IEEE transactions on nanotechnology, Vol. 1, No. 1, pp. 78-85.

- [8] Navin Srivastava and Kaustav Banerjee, 2004, "A Comparative Scaling Analysis of Metallic and Carbon Nanotube Interconnections for Nanometer Scale VLSI Technologies", International VLSI Multilevel Interconnect Conference, pp. 393-398.

- [9] A. Naeemi and J. D. Meindl, 2005, "Monolayer metallic interconnects promising candidates for short local interconnects", Electron device letters, Vol. 26, No. 8, pp. 544-546.

- [10] A. Maffucci, G. Miano, and F. Villone, 2007, "Comparison between metallic carbon nanotube and copper nano-interconnects", IEEE transactions on advanced packaging, Vol. 31, No. 4, pp. 29–32.

- [11] A. Deush, G. V. Kopesay, and P.Restle, 1997, "Analysis of on chip inductance effect for distributed RLC interconnect", IEEE transaction on computer-aided design of integrated circuits and system, Vol. 21, Issue 8, pp. 904-915.

- [12] P. J. Burke, 2002, "Lüttinger liquid theory as a model of the gigahertz electrical properties of carbon nanotubes", IEEE transactions on nanotechnology, Vol. 1, No. 3, pp. 129-144.

- [13] Devendra Kumar Sharma, B. K. Kaushik and R. K. Sharma, 2010, "Effect of Mutual Inductance and Couplig Capacitance on Propagation Delay and Peak Overshoot in Dynamically Switching Inputs", ICETET 2010, pp. 765-769.

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)