# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: XI Month of publication: November 2017

DOI:

www.ijraset.com

Call: © 08813907089 E-mail ID: ijraset@gmail.com

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887

Volume 5 Issue XI November 2017- Available at www.ijraset.com

## A Design for Improved Very Low Power Static Flip Flop Using Two Inverters and Five NORs

Jogi Prakash<sup>1</sup>, G. Someswara Rao<sup>2</sup>, Ganesan P<sup>3</sup>, G. Ravi Kishore<sup>4</sup>, Sandeep Chilumula<sup>5</sup>

<sup>1</sup>M Tech Student, <sup>2, 4, 5</sup> Assistant Professor, <sup>3</sup>Professor, ECE Department, Vidya Jyothi Institute of Technology (VJIT)

Abstract: This article proposed an improved very low-power static flip-flop (IVLPSFF) for very low power VLSI applications. The proposed IVLPSFF has two numbers of NOTs (inverter) and five numbers of NORs. It has a root clock for the generation of the positive edge triggered clock signal for the purpose of transmitting the data into the master flip flop. Whereas the negative edge triggered clock signal for the holding of data in the slave flip flop. The proposed method utilized 24 transistors. The simulation results for the 45nm standard CMOS procedure revealed that our method IVLPSFF attained delay in the order of 1.558 ns, power dissipation of 0.915 nW at 1.11 to 2 MHz clock frequency and 0.35V power supply. For the proposed design the layout area is 8.568µm which is very narrow as compared to other methods.

Keywords: Improved Very Low-Power Static Flip-Flop (IVLPSFF), Flip Flop, Logic Gate, Power, Delay, Area, DRC, LVS.

#### I. INTRODUCTION

Low-power CMOS VLSIs have involved much attention for use in control aware applications, for example, wireless smart sensor networks and implantable bio-medical systems. Several low power techniques have been investigated. Among them, lessening the supply voltage for digital circuits is the most immediate and compelling way to achieve low power dissipation, because of the quadratic reliance of the power dissipation on the supply voltage. One major issue for low voltage digital circuits is in the designing of a flip-flop circuit. Because FFs are broadly utilized as a part of present day digital VLSI systems for example, a general purpose register, a pipeline register, and a finite state machine.

In this article, we herein propose an Improved Very Low-Power Static Flip-Flop (IVLPSFF) for extremely low power digital circuits. The IVLPSFF has two numbers of NOTs (inverter) and five numbers of NORs. The count of transistors is twenty four, which is the same as the conventional circuit shared static flip flop (CSSFF). Our proposed IVLPSFF attained delay in the order of 1.558 ns, power dissipation of 0.915 nW at 1.11 to 2 MHz clock frequency and 0.35V power supply. For the proposed design the layout area is 8.568  $\mu$ m which is very narrow as compared to other methods.

#### II. RELATED WORK

Existing Techniques areCircuit Shared Static Flip Flop (CSSFF), Tri-state buffer based flip-flop (TBFF), NAND latch based flip-flop (NLFF), Contention less flip-flop (CLFF). The CSSFF is the most useful technique when compared to other conventional techniques, but the power dissipation and delay was not optimized. The CSSFF consist of same 24 transistors like TBFF. TBFF is used in most standard cell libraries. However the use of the TBFF becomes difficult to operate at lower voltage like below the  $V_{th}$ . The main reason behind this is the yield of the tri state buffers are connected in wired-Or which leads to the increase of the power dissipation. The NLFF and CLFF consist of more number of transistors when compared to TBFF and CSSFF. If the transistor count was increased the area and power dissipation also increases. To achieve low power and less delay FF, we propose an Improved Very Low-Power Static Flip-Flop consists of NORs and INVERTERs with a small number of Transistors. Which can be operates at lower voltages.

#### III.PROPOSED METHOD

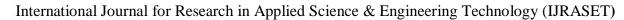

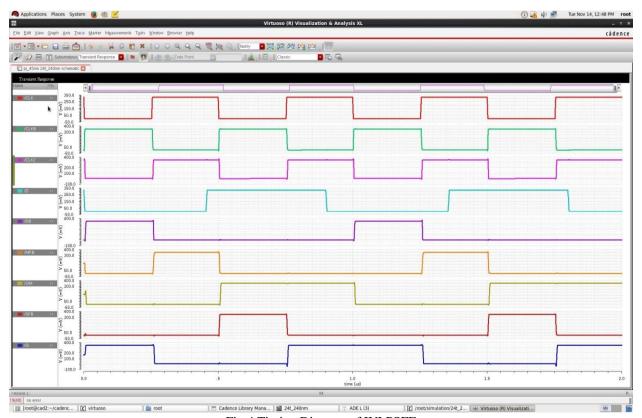

The Improved Very Low-Power Static Flip-Flop (IVLPSFF) has two numbers of NOTs (inverter) and five numbers of NORs (NOR<sub>1</sub>-NOR<sub>5</sub>) and the total number of transistors is 24 as shown in Fig. 1. The NOTs are used to generate control signals of CLKB and CLK<sub>2</sub> from root clock of CLK. NOR<sub>1</sub>, NOR<sub>2</sub>, and NOR<sub>3</sub> form a master flip flop, while NOR<sub>3</sub>, NOR<sub>4</sub>, and NOR<sub>5</sub> form a slave flip flop. Note that NOR<sub>3</sub> is shared both in the master and slave flip flops, and is used to acquire data in the master and transfer it to the slave. In this way Low-Power Static Flip-Flop (IVLPSFF) works. The timing diagram of circuit operation is shown in the fig.4. The master operates using a positive edge of control signal of CLK<sub>2</sub>. NOR<sub>2</sub> and NOR<sub>3</sub> form the master flip flop. Meanwhile, the slave operates using a negative edge of clock signal of CLK. Therefore, NOR<sub>4</sub> and NOR<sub>5</sub> form the slave flip flop, and the data is

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 5 Issue XI November 2017- Available at www.ijraset.com

held at Q as Data (D0). This way our proposed Improved Very Low-Power Static Flip-Flop (IVLPSFF) operates as a master-slave flip-flop with a small number of transistors.

#### IV.RESULT AND DISCUSSION

Fig. 1. Schematic diagram of our proposed Improved Very Low-Power Static Flip-Flop (IVLPSFF)

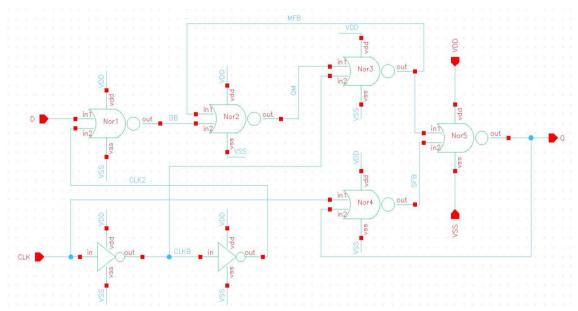

#### A. NOR Gate

NOR gate belongs to logic family. It is the universal gate. The digital NOR logic gate which performs logical NOR operation  $Y=\sim$  (A+B). Whenever the both inputs are low, then the output will be high, for remaining input conditions the output will be low. With NOR gate we can design any logic gate, the operation of NOR gate is exactly negation of OR operator. The static NOR is designed with the combination of PMOS and NMOS, which is known as CMOS. The transistor size in the NOR is  $L_{P=}0.045$ ,  $W_{P}=0.24$ ,  $L_{N=}0.045$ ,  $W_{N}=0.12~\mu m$ , respectively.

Fig.2NOR Schematic of IVLPSFF

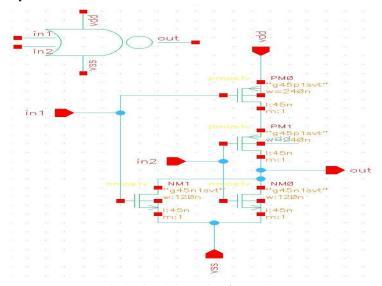

#### B. NOT Gate

NOT gate belongs to logic family. It is called INVERTER. The digital NOT logic gate which performs logical NOT operation Y= ~A. whatever the input may be the output will be exactly negative of input. With the help of two INVERTER connections in a series

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 5 Issue XI November 2017- Available at www.ijraset.com

can form a buffer. In the conversion of NOR logic to OR and NAND logic to AND we need NOT gate. The static NOT gate is designed with the combination of PMOS and NMOS, which is known as CMOS. The transistor size in the NOT is  $L_{P\,=}\,0.045,\,W_{P}\,=\,0.24,\,L_{N\,=}\,0.045,\,W_{N}\,=\,0.12\,\mu m$ , respectively.

Fig.3 NOT Schematic of IVLPSFF

Fig.4 Timing Diagram of IVLPSFF

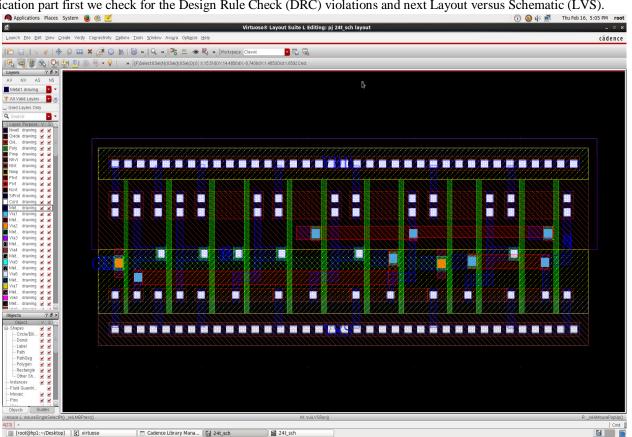

#### C. Full Custom Layout

Full custom Layout of Improved Very Low-Power Static Flip-Flop (IVLPSFF) as shown in fig.5, full custom designs are done by drawing stick diagram of a schematic and choosing the technology. For particular technology there are set of rules. Likewise for

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 5 Issue XI November 2017- Available at www.ijraset.com

45nm there are different rules when compared to different technologies, which means every technology is unique. Full custom design is very difficult. Why because, manually task should be done by us by taking the layers, placing of cells and routing of metals while designing the full custom layout. After designing of layout we need to do physical verification (Assura) for the layout. In verification part first we check for the Design Rule Check (DRC) violations and next Layout versus Schematic (LVS).

Fig.5 Full custom Layout of IVLPSFF

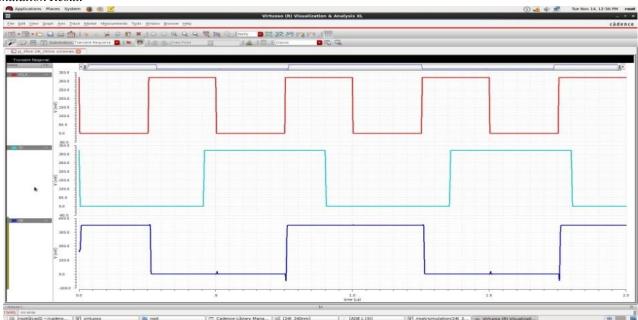

#### D. Simulation Result

Fig.6 Simulated Waveform of IVLPSFF

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor: 6.887

Volume 5 Issue XI November 2017- Available at www.ijraset.com

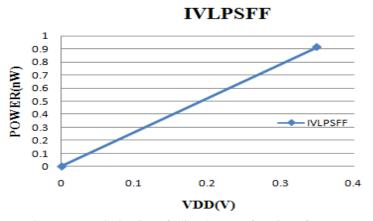

Figure.7 illustrates the power dissipation of the IVLPSFF as a function of VDD 0.35V. Our proposed technique power by 0.9154nW.

Fig.7 Power Dissipation of Flip Flop as a function of VDD

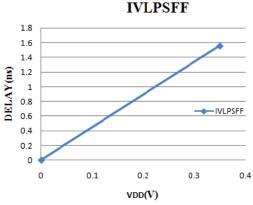

Figure 8 depicts the clock to Q delay of the IVLPSFFas function of VDD 0.35V.Our proposed technique delay by 1.55 ns.

Fig.8 Delay of Flip Flop as a function of VDD

The function of the flip flop can be explained based on the parameters such as Frequency, PMOS Width, NMOS Width, Power, Delay and Area. The operating frequency of IVLPSFF was good when compared to other methods at 0.35V. This is illustrated in table 1.

TABLE I PERFORMANCE COMPARISON AT 0.35V

| FF      | Frequency | PMOS       | NMOS      | Power | Delay | Area  |

|---------|-----------|------------|-----------|-------|-------|-------|

|         | (MHz)     | Width (µm) | Width(µm) | (nW)  | (ns)  | (µm)  |

| IVLPSFF | 1.11-2    | 0.24       | 0.12      | 0.91  | 1.55  | 8.568 |

| IVLPSFF | 1.11-2    | 0.12       | 0.12      | 0.65  | 2.9   | 7.996 |

Table 2 shows the 180, 130, 90 and 45nm technology results of IVLPSFF along with CSSFF and ECSSFF.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887

Volume 5 Issue XI November 2017- Available at www.ijraset.com

### TABLE 2 PERFORMANCE COMPARISON AT VARIOUS NANO METRE TECHNOLOGIES

| FF      | PMOS<br>Width (μm) | NMOS<br>Width<br>(µm) | Frequency (MHz) | Voltage (V) | Power (nW) | Delay (ns) | Area(µm) |

|---------|--------------------|-----------------------|-----------------|-------------|------------|------------|----------|

| CSSFF   | 1.37               | 1                     | 1               | 0.347       | 6.61       | 586        | 50.5     |

| (180nm) |                    |                       | 1               | 0.5         | 15.4       | 17.4       |          |

| ECSSFF  | 1.37               | 1                     | 1               | 0.347       | 12.1       | 4.957      | -        |

| (130nm) |                    |                       |                 |             |            |            |          |

| ECSSFF  | 0.12               | 0.12                  | 2               | 0.5         | 5.253      | 254.4      | -        |

| (90nm)  |                    |                       |                 |             |            |            |          |

| IVLPSFF | 0.24               | 0.12                  | 1.11-2          | 0.35        | 0.9154     | 1.558      | 8.568    |

| (45nm)  |                    |                       |                 |             |            |            |          |

#### V. CONCLUSION

Cadence simulation results for 45nm technology. Our proposed IVLPSFF achieved power-dissipation of 0.9154 nW and clock to Q delay of 1.55 ns at 0.35-V and 1.11-2.0 MHz clock frequency. For the proposed design the layout area is 8.568µm which is very narrow as compared to other methods. This project can also be implemented in FIN-FET to optimize power, delay and area.

#### **REFERENCES**

- [1] YuzuruShizukuy, Tetsuya Hirosey, Nobutaka Kurokiy, Masahiro Numay, and MitsujiOkadaz, A 24t static flip flop using nors and inverters for low power digital VLSIs

- [2] Efficient implementation to optimize power and delay using enhance cssff with 24 transistors

- [3] A. P. Chandrakasan, S. Sheng, and R. W. Brodersen, "Low-power CMOS digital design," IEEE Journal of Solid-State Circuits, vol. 27, pp. 473 484, 1992.

- [4] R. J. Baker, CMOS Circuit Design, Layout, and Simulation, Second Edition, IEEE Press, 2004.

- [5] N. Weste and D. Harris, CMOS VLSI design, 4th Edition, Addison-Wesley, 2010.

- [6] A. Wang, B.H. Clhoun, and A.P. Chandrakasan, Sub-threshold Design for Ultra Low-Power Systems, Springer, 2006.

- [7] J. Warnock, L. Sigal, D. Wendel, K.P. Muller, J. Friedrich, V. Zyuban, and E. Cannon, A.J. KleinOsowski, "POWER<sup>7TM</sup> local clocking and clocked storage elements," in IEEE ISSCC Dig. Tech. Papers, 2010, pp. 178 179.

- [8] H. Kaul, M. Anders, S. Hsu, A. Agarwal, R. Krishnamurthy, and S. Borkar, "Near-threshold voltage (NVT) design Opportunities and challenge," in Proc. the 49th Annual Design Automation Conference, pp. 1153 1158, 2012.

- [9] H. Fuketa, K. Hirairi, T. Yasufuku, M. Takamiya, M. Nomura, H. Shinohara, T. Sakurai, "12.7-times Energy Efficiency Increase of 16-bit Integer Unit by Power Supply Voltage (VDD) Scaling from 1.2V to 310mV Enabled by Contention-less Flip-Flops (CLFF) and Separated VDD between Flip-Flops and Combinational Logics," Int. Symp. Low Power Electronics and Design (ISLPED), pp. 163-168, 2011.

- [10] J. Kwong, Y. Ramadass, N. Verma, M. Koesler, K. Huber, H.Moormann, and A. Chandrakasan, "A 65 nm sub-Vt microcontroller with integrated SRAM and switched capacitor DC-DC converter," IEEE J. Solid-State Circuits, vol. 44, pp. 115-126, 2009.

- [11] S. Hanson, B. Zhai, K. Bernstein, D. Blaauw, A. Bryant, L. Chang, K. K. Das, W. Haensch E. J. Nowak, D. M. Sylvester, "Ultralow-voltage, minimum-energy CMOS," IBM J. RES. & DEV., vol. 50, No. 4/5, 2006.

ISSN: 2321-9653; IC Value: 45.98; SJ Impact Factor:6.887 Volume 5 Issue XI November 2017- Available at www.ijraset.com

#### A. Author Profile

JOGI PRAKASH, M Tech Student in Department of Electronics and Communication Engineering, VidyaJyothi Institute of Technology, Autonomous (Affiliated to JNTUH), Aziz Nagar Gate, C.B. Post, Hyderabad-500075, Telangana, Email: <a href="mailto:prakashakash75@gmail.com">prakashakash75@gmail.com</a>

#### B. Author Profile

G. SOMESWARA RAO, Assistant Professor in Department of Electronics and Communication Engineering, VidyaJyothi Institute of Technology, Autonomous (Affiliated to JNTUH), Aziz Nagar Gate, C.B. Post, Hyderabad-500075, Telangana, Email: someshg.somu@gmail.com

#### C. Author Profile

GANESAN P, Professor in Department of Electronics and Communication Engineering, VidyaJyothi Institute of Technology, Autonomous (Affiliated to JNTUH), Aziz Nagar Gate, C.B. Post, Hyderabad-500075, Telangana, Email: gganeshnathan@gmail.com

#### D. Author Profile

G. RAVI KISHORE, Associate Professor in Department of Electronics and Communication Engineering, VidyaJyothi Institute of Technology, Autonomous (Affiliated to JNTUH), Aziz Nagar Gate, C.B. Post, Hyderabad-500075, Telangana, Email: ravikishore@vjit.ac.in

#### E. Author Profile

SANDEEP CHILUMULA, Assistant Professor in Department of Electronics and Communication Engineering, VidyaJyothi Institute of Technology, Autonomous (Affiliated to JNTUH), Aziz Nagar Gate, C.B. Post, Hyderabad-500075, Telangana, Email: sandi.lds@gmail.com

10.22214/IJRASET

45.98

IMPACT FACTOR: 7.129

IMPACT FACTOR: 7.429

## INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call: 08813907089 🕓 (24\*7 Support on Whatsapp)