IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Volume: 5 Issue: VI Month of publication: June 2017 DOI:

www.ijraset.com

Call: 🛇 08813907089 🕴 E-mail ID: ijraset@gmail.com

www.ijraset.com IC Value: 45.98 *Volume 5 Issue VI, June 2017 ISSN: 2321-9653*

## International Journal for Research in Applied Science & Engineering Technology (IJRASET) Design of 12-Bit DAC Using CMOS Technology

Payal Jangra<sup>1</sup>, Rekha Yadav<sup>2</sup>

<sup>1</sup>M. Tech. (VLSI) Student, <sup>2</sup>Assistant Professor Department of ECE, DCRUST, Murthal

Abstract: Digital-to-Analog Converter (DAC) is used to convert a digital form of input into an analog form of output. In this paper, a digital-to-analog converter which is based on the R-2R ladder is analyzed for low power consumption i.e. 27.04 mW, low active chip area i.e. .054 mm<sup>2</sup> and low DNL i.e. 0.03. R-2R DAC is implemented using cadence virtuoso tool in 180nm CMOS process. The main components used are an operational amplifier and R-2R ladder network. Op-amp is made up of two stages. The first stage of op-amp consists of a differential amplifier and the second stage consists of common source amplifier. The first stage is used to get high gain and the second stage increases output swing and gain of the first stage. Keywords: operational amplifier; CMOS; R-2R ladder; DNL; DAC

#### I. INTRODUCTION

An R-2R Ladder is a basic and sensible method for performing digital to analog transformation. R-2R ladder comprises of an arrangement of resistors in ladder-like structure. It changes over a parallel digital input into an analog output voltage. Individual digital input (B0, B1, B2, and so forth.) includes its own particular weighted commitment to the analog output yield.

- A. The features of this network

- 1) It can be easily designed for any number of bits

- 2) This DAC uses only two values of resistors.

- 3) The output impedance of this DAC is fixed i.e. R, irrespective of a number of resistors [1].

Resistance ladder or resistor string converter is a basic type of DAC. This DAC comprises of resistor string of indistinguishable resistors, and parallel switch exhibit whose sources of input are the binary word. The simple output is the voltage division of the resistors streaming through pass switches. The output is associated with at most N switches on and N turns off [2]. In this paper, 12-bit digital input (D0 to D11) is converted into analog output  $V_{dac}$ . The supply voltage used is 2.5V and the technology used is CMOS 180nm process. Voltage step for N-bit DAC can be expressed as in equation (1)

$$\Delta v = \frac{V dac}{2^N} \tag{1}$$

For a 12-bit DAC, the value of output voltage will change in steps of 0.6mV. In R-2R ladder DAC, nonlinearity occurs for resistor ladder network as they do not create regular resistance values.

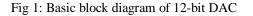

It is very difficult to construct resistor based DAC with high resolution because it requires a large number of resistors. A better choice will be the use of R-2R ladder configuration. Fig 1 shows the basic block diagram of 12-bit DAC.

The design here is a 12-bit R-2R architecture DAC implemented using cadence virtuoso tool in 180nm CMOS technology. The

#### www.ijraset.com IC Value: 45.98

*Volume 5 Issue VI, June 2017 ISSN: 2321-9653*

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

main features of the 12-bit R-2R DAC design are discussed in the next sections. In Section II an overview of the design of the DAC is discussed. In Section III obtained simulation results and waveforms are presented. The main conclusion result is presented in Section IV.

#### **II. DAC DESIGN**

In this work, a 12-bit digital to analog converter is designed. The implementation of 12-bit R-2R DAC is shown in Fig 2. An R-2R resistor network and an operational amplifier are the major components used to build the circuit.

Fig 2: Implementation of 12-bit R-2R DAC

#### A. Design of op-amp

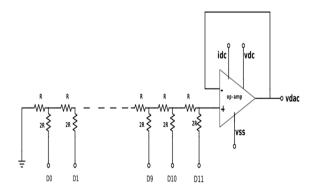

An op-amp is an amplifier having high gain and input impedance which is used to perform mathematical operations on an input voltage. This op-amp consists of two stages namely differential amplifier stage and common source stage. The schematic of the op-amp is shown in Fig3. The inputs given for op-amp are idc  $5\mu$ V, Vdd 2.5V, Vss -2.5V, vninv gnd and vinv is given Vsin pulse with amplitude 5mV and frequency 1k. Finally, the output is taken from transient, AC and dc analysis. Gain and bandwidth of op-amp are also calculated.

Fig 3: Schematic of op-amp

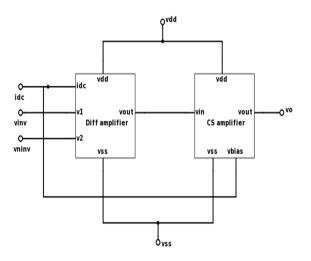

#### B. Design of differential amplifier

A differential amplifier is an electronic amplifier which amplifies the difference between two input voltages and suppresses the common voltage. The differential amplifier is the first stage in designing op-amp. This stage is used to get high gain. The schematic of the differential amplifier is shown in Fig4. The inputs given for differential amplifier are ide  $5\mu$ V, Vdd 2.5V, Vss -2.5V, vninv gnd and vinv is given Vsin pulse with amplitude 5mV and frequency 1k. Finally, the output is taken from transient, AC and dc analysis.

## International Journal for Research in Applied Science & Engineering Technology (IJRASET)

Fig 4: Schematic of the differential amplifier

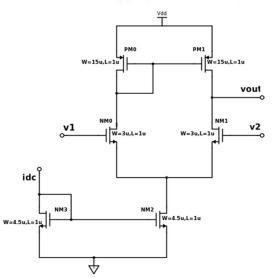

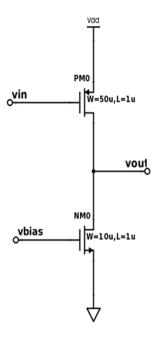

#### C. Design of CS amplifier

Common source amplifier is the second stage used in the design of op-amp. This stage is used to improve gain and output swing of the first stage i.e. differential stage. The schematic of cs amplifier is shown in Fig5. The inputs given for cs amplifier are idc  $5\mu$ V, Vdd 2.5V, Vss -2.5V, vninv gnd and vinv is given Vsin pulse with amplitude 5mV and frequency 1k. Finally, the output is taken from transient, AC and dc analysis.

#### **III.SIMULATION RESULTS AND WAVEFORMS**

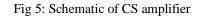

#### A. DAC output

To obtain the output of DAC, its transient analysis has been done. The input value of idc is  $5\mu$ V and Vdd is 2.5V. Simulation result

IC Value: 45.98 International Journal for Research in Applied Science & Engineering Technology (IJRASET)

of 12-bit R-2R DAC is shown in Fig 6.

www.ijraset.com

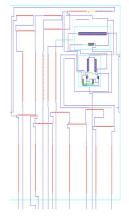

B. DAC layout

Fig 7: Physical layout of 12-bit R-2R DAC

#### C. DAC parameters

DAC parameters like power consumption, area, delay and DNL has been calculated as shown in TABLE I.

| D                       | AC PARAMET | ERS  |           |

|-------------------------|------------|------|-----------|

| Parameters              | [10]       | [9]  | This work |

| Technology (µm)         | 0.13       | 0.18 | 0.18      |

| Resolution (bits)       | 12         | 12   | 12        |

| Supply voltage (V)      | 0.72-1.2   | 1.8  | 1.8-2.5   |

| Power consumption       | 13.4       | 48.6 | 27.04     |

| (mW)                    |            |      |           |

| Area (mm <sup>2</sup> ) | 0.072      | -    | 0.054     |

| DNL                     | 0.7        | 0.6  | 0.03      |

| - | <b>FABLE I</b> |

|---|----------------|

| C | DADAMETE       |

www.ijraset.com IC Value: 45.98 *Volume 5 Issue VI, June 2017 ISSN: 2321-9653*

### International Journal for Research in Applied Science & Engineering Technology (IJRASET)

#### **IV.CONCLUSIONS**

A 12-bit R-2R DAC is designed and implemented in cadence virtuoso tool using 180nm CMOS process. This DAC is designed for low power consumption, low active chip area, and low DNL. As compared to previous work in 180nm technology, power is reduced from 48.6 to 27.04mW and DNL is reduced from 0.6 to 0.03. Comparing from 130nm technology, DNL is reduced from 0.7 to 0.03 and active chip area is reduced from 0.072 to 0.054mm<sup>2</sup>.

#### REFERENCES

- [1] Tutorial: Digital to Analog Conversion The R-2R DAC, Alan Wolke, May 2013.

- [2] Anshul Agarwal, Design of Low Power 8-Bit Digital-to-Analog Converter with Good Voltage-Stability, Center for VLSI and Embedded System Technologies International Institute of Information Technology Hyderabad, India May 2013.

- [3] Arpit Kumar Baranwal, "Design and Analysis of 8 Bit Fully Segmented Digital to Analog Converter" IEEE 2nd International Conference on Recent Advances in Engineering & Computational Sciences (RAECS), Dec 2015.

- Hong Liu; Ning Tang; Mingliang Wang; Zhao Xia; Ke Zhang; Tian Tong"A Monolithic 12-Bit Digitally CalibratedD/A Converter" IEEE 20th International Conference on Electronics, Circuits, and Systems (ICECS), Dec 2013, pp. 449-452.

- [5] Hicham Akhamal, Hassan Qjidaa, "A low power 6-bit current-steering DAC in 0.18-µm CMOS process" IEEE Intelligent Systems and Computer Vision (ISCV), 2015, pp. 1-5.

- [6] Aiman Abdullah Noorwali; Syed Manzoor Qasim; Ahmad Samim Doost; Anh Huynh, "A 16-bit 4 MSPS DAC for lock-in amplifier in 65nm CMOS" IEEE 13th International Conference on Networking, Sensing, and Control (ICNSC), April 28-30, 2016, pp. 1-6

- [7] Rudy J Van de Plassche. CMOS integrated analog-to-digital and digital-to-analog converters, volume 2. Kluwer Academic Publishers Dordrecht, 2003.

- [8] C. Joo, S. Kim, K. Yoon, "A low-Power 12-Bit 80MHz CMOS DAC Using Pseudo-Segmentation", GLSVLSI 2008, May 2008, pp. 219-222

- [9] Guoyuan Fu, H. Alan Mantooth, and Jia Di, "A 12-Bit CMOS Current Steering D/A Converter with a Fully Differential Voltage Output" IEEE, May 2011.

- [10] B. Razavi, —Design of Analog CMOS Integrated Circuits, New York: Mc-Graw Hill,2001.

- [11] ] D. Johns and Ken Martin Analog Integrated Circuit Design, Wiley India Pvt. Ltd, 1997.

- [12] Kang Sung-Mo, Leblebici Yusuf, Cmos digital integrated circuits, analysis and design (Tata McGraw-Hill Edition 2003, Third Edition).

- [13] P. Allen and D. Holberg, CMOS Analog Circuit Design. New York: Holt Rinehart and Winston, 1987.

- [14] Sonu kumar, Anjali sharma, Payal jangra, Pooja Rathee, Rekha yadav, "Design of CMOS operational amplifier in 180nm technology", Volume5, Issue4, April2017, doi:10.15680/IJIRCCE.2017.0504001.

45.98

IMPACT FACTOR: 7.129

# INTERNATIONAL JOURNAL FOR RESEARCH

IN APPLIED SCIENCE & ENGINEERING TECHNOLOGY

Call : 08813907089 🕓 (24\*7 Support on Whatsapp)