Ijraset Journal For Research in Applied Science and Engineering Technology

- Home / Ijraset

- On This Page

- Abstract

- Introduction

- Conclusion

- References

- Copyright

An Enhanced Strong ARM Comparator Circuit for Analog to Digital Converter Architectures

Authors: M. Adhithya, K. Lokesh Krishna

DOI Link: https://doi.org/10.22214/ijraset.2024.59057

Certificate: View Certificate

Abstract

Technological innovations in the current century period have motivated professionals to make electronic gadgets smarter. These advancements are progressing at a brisk pace, facilitating faster changes and increase in computing power. Various technologies such as virtual reality, augmented reality, mobile internet, artificial intelligence, cloud computing, biometric devices, 3D printing machines, genomics, quantum computing, block-chain, industrial automation and robotics. In all these technologies, communications with nearby devices play a major role in its effective functioning. The demand for realizing a smart and better usage experience puts forth strict requirements on the design aspects of next-generation high speed low power CMOS receiver design. One of the major modules in the implementation of high speed low power CMOS receiver device is the analog to digital converter (ADC) architecture. In the process of conversion from analog to digital signals, Quantization and sampling operations are vital and are realized using comparator circuits. The comparator design has a significant role in the design of data converter architecture. Several comparator architectures exist, but StrongARM topology is discussed and implemented in this work due to its negligible static power dissipation and rail to rail output voltages. The proposed novel comparator architecture is designed and simulated in 180nm CMOS process using Cadence Virtuoso tool and operated at supply voltage of VDD=1.8V, a clock frequency of 50MHz.

Introduction

I. Introduction

Integrated circuit innovations in the current century period have inspired specialists to make electronic appliances smarter. These advancements are progressing at a brisk pace, facilitating faster changes and increase in computing power. Various technologies such as virtual reality, augmented reality, mobile internet, artificial intelligence, cloud computing, biometric devices, 3D printing machines, genomics, quantum computing, block-chain, industrial automation and robotics. In all these technologies, communications with nearby devices play a major role in its effective functioning. The fourth generation and fifth generation communications evolved to offer reliable and steadfast data transfer globally. At present the usage of high performance electronic gadgets enables high speed and safe access to the internet. The ever increasing demand of lower latency values, better connectivity, stable and high speed data transmission poses stringent requirements for next level high speed communication designs. The above high performance requirements are met by the inclusion of an efficient Analog to Digital Converter (ADC) architecture in the communication transceiver hardware. ADC architectures are essential and omnipresent in all receiver architectures.

Data converter architectures are key modules and are crucial in the implementation of various electronic equipment. Data converter architectures are classified as analog to digital converter (ADC) and digital to analog converter. ADCs transform continuous time voltage signals (i.e. real time measurement) to discrete time voltage signals (i.e. digital), whereas the DACs convert discrete time voltage signals (i.e. discrete in nature) to continuous time signals. Mixed mode architecture implementation requires both the ADC and DAC circuits on the same chip. The converter architectures operate on the principle of Nyquist theorem. The theorem specifies that the original analog signal voltage can be accurately restored from the obtained samples of the input analog voltage waveform only if waveform sampling rate is greater than or equal to two times the highest bandwidth of the input analog signal. This statement is very important in the signal conversion techniques and it also corresponds to the operating speed of the whole integrated circuit. Applications that demand high speed operation are augmented reality, mobile internet, artificial intelligence, cloud computing, home automation, biometric devices, virtual reality, 3D printing machines, genomics, quantum computing, block-chain, industrial automation and robotics. Thus the efficient design of a analog to digital converter circuit architecture is very important module to be considered in the implementation for these applications. In literature, several ADC architectures exist such as Flash type, successive approximation register type, sigma-delta type, two-step flash type, single slope and dual slope type etc., although the proposed comparator design is targeted for Flash type ADC architecture. The flash ADC is a very fast data converter architecture used for conversion of input analog signal voltages to digital signal voltages.

The conversion of signal takes place in one cycle time-period. Even though the speed of operation is very high; it does suffer from drawbacks such as increased circuit complexity due to increase in resolution size, and inclusion of additional circuit block namely thermometer to binary code which inevitably rises the power consumption of the whole circuit..

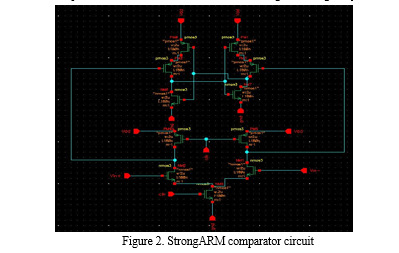

Several comparator architectures are available in the previous works such as Single-stage, Two-stage, Open-loop, Push-pull, comparator driving large capacitive loads, Singe-tail, Double-tail, Triple-tail latch, Switched capacitor comparator, StrongARM comparators, Regenerative comparators, Fully-differential two and three stage latch comparators, and high speed comparator circuits comprising of cascaded preamplifiers, latches and output driver circuits. Circuit designers often trade-off with different specifications and prefer double-tail comparators for use in high speed data converter circuits. On the whole a comparator circuit is realized by a differential input pair consisting of PMOS and NMOS transistors followed by an active load stage, decision stage and an amplifying stage. For high speed circuits additional amplification stage may be added to the circuit. The different stages in a classic comparator circuit are presented in Fig.1.

In general, a comparator circuit equates two signals (given input voltage with a standard reference voltage) and delivers a output discrete value i.e. logic or high levels.

The comparator circuits can also be used to detect a random signal whenever it crosses above zero or below zero reference voltage levels. The input preamplification stage circuit provides sufficient signal amplification levels before it is being fed at the output stage. This stage reduces the inherent kick-back voltage produced by the decision stage. The amplification of the circuit should be higher so as to provide necessary positive feedback in the circuit. The final stage also known as post-amplification stage is necessary to avoid the loading effect of the next following stages.

Kobayashi et. al. of Toshiba corporation has initially proposed the original StrongARM latch configuration for a 0.512MB high-speed static RAM circuit [1]. It includes a low powered current controlled latch sense amplifier for memory and interface circuits and the simulation results demonstrate the access time (pico-seconds) is minimized. The StrongARM comparator circuit is a familiar and extensively used topology in data converter architectures and flip-flop circuits for various high speed and low power transceiver circuits. It is a unique and robust circuit with features such as high sensitivity, offers rail-to-rail output voltage, very high input impedance for time varying signals, low input referred offset voltage arising due to only one differential pair and virtually no static power dissipation [2]- [3]. The authors in [4] describe a novel and simple dynamic bias comparator in 0.065micrometer CMOS technology. A complete mathematical analysis is carried out in both weak inversion and strong inversion operating regions of the comparator. The simulation results in this work demonstrate that the DC power consumption reduces by a factor of 2.5 times at an input common mode level of half the VDD. Mohtashemi et al., presented a novel comparator circuit exhibiting wider bandwidth [5]. The circuit doesn’t use spiraled inductors and simulated at VDD=1.2Vdc and implemented in 130nm CMOS process. The authors in [6] compare strongARM and double-tail comparator circuits which include offset voltage compensation circuits. A parallel path based strongARM latch circuit is proposed in [7]. The simulation results in 0.065micrometer technology report that the operating speed enhances by almost 50% at a bandwidth of 3gigahertz. K.S.Kumar et al. described the design of a low offset voltage and high speed double-tail comparator for use in comparator array of a flash analog to digital converter architecture [8]. The comparator circuit is operated at VDD=1.8V and consumes power of 0.124mW. Ramamurthy et al. proposed a digital calibration technique to enhance the signal to noise distortion ratio almost to 20dB [9]. The authors in [10] present a novel pipelined ADC architecture in 180nm CMOS process. The methodology is based on by inserting a buffer circuit in second stage due to which offset voltage is eliminated without any delay.

The proposed circuit was able to detect differences at the input differential stage. Khorami et al. describes the design of a two stage dynamic bias comparator which consists of p-channel MOS transistors in both the stages of the comparator architecture [11]. The modified strongARM comparator architecture along with its working details are discussed in Section-2, while Section-3 provides the simulated results and its discussion. To sum up Section-4 presents the conclusions of the presented work.

II. Implementation of THE PROPOSED STRONGARM comparator architecture

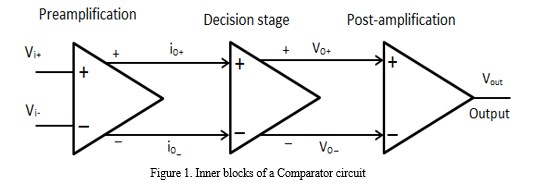

The proposed modified StrongARM comparator circuit shown in Figure 2 operates in different phases namely reset, amplification and regeneration. The circuit consists of MOS switches MS1, MS2, MS3 and MS4, a differential pair with a clock source (VCK) and triple cross-coupled differential pairs (M1 & M2), (M3 & M4) and (M5 & M6) [12]- [13]. The tail transistor is driven with a clock source. The differential output voltage is taken at the drain nodes of M5, M6, M7 and M8. Correspondingly, the voltage at these nodes is designated as VA and VB. The main feature of this proposed StrongARM configuration is that it delivers rail-to-rail output voltages at nodes A and B.

The circuit responds to difference in the input voltages (Vi1-Vi2). In the first phase when the clock voltage is low i.e. VCK=low, then the transistors M1 and M2 are off and accordingly the internal capacitances at nodes A, B, X and Y are precharged to the supply voltage VDD through the MOS switches MS1, MS2, MS3 and MS4.The next stage is the amplification phase, which gets initiated, when the clock voltage is high i.e. VCK=high. With these connections, the MOS switches MS1, MS2, MS3 and MS4 are off and the charged voltage gets discharged through M7, while M1 and M2 are conducting [14]- [16]. Transistors M1 and M2 are biased by a constant common mode voltage (VCM). When there is a small difference in differential currents applied at M1 and M2 due to minute differences in (Vi1-Vi2), then the capacitances at the nodes X and Y are discharged at marginally different discharging rates.

When voltages at X and Y drop to (VDD-Vtn), transistors M5 and M6 turn ON. In this phase, the voltage |VX-VY| increases and certainly beyond (Vi1-Vi2). Hence in this stage, voltage amplification is achieved. The MOS transistors M3 and M4 are ON and its drain nodes are precharged to VDD. Next when clock is its high level, the MOS transistors M3 and M4 are switched OFF. The transistor at the lower end of the circuit i.e. the tail transistor is switched ON and the capacitances at the drain nodes of M3 and M4 are discharged rapidly. Under these discharging conditions, the resulting common mode current flows through the tail transistor. Due to this the gate to source voltage of the input differential paper consisting of MOS transistors M1 and M2 is reduced, and thus creates a dynamic biasing voltage for the input differential pair [17]- [18]. The voltage keeps reducing until the effective voltage at the source of both the M1 and M2 transistors reach the minimum value of difference between inverting input, non-inverting input and threshold voltages. Correspondingly at this instant of time one of the input transistors either M1 or M2 is switched off. The other transistor which is conducting at the same instant of time will continue to discharge through its drain node. The preamplification stage consumes around (60 to 70) % of the total power dissipation of the circuit. To get lower noise, the overdrive voltage of the input differential transistors must be minimized.

Conclusion

Due to the ever-increasing requirement of high performance comparator architectures, there is a strong need to make the transistor to operate at their saturation limits. The need for low voltage operation enforces severe requirements on the detection of quantized voltage levels. The presented work shows a modified novel strongARM latch circuit for analog to digital converter architectures. The comparator circuit is designed and simulated in 180nm CMOS process using Cadence Virtuoso tool and operated at supply voltage of VDD=1.8V, a clock frequency of 100MHz. Consequently the proposed comparator architectural design would be an important choice in the implementation of a comparator bank in high speed flash analog to digital converter.

References

[1] T. Kobayashi, K. Nogami, T. Shirotori and Y. Fujimoto, \"A current-controlled latch sense amplifier and a static power-saving input buffer for low-power architecture,\" in IEEE Journal of Solid-State Circuits, vol. 28, no. 4, pp. 523-527, April 1993. [2] Phillip E. Allen and D.R. Holberg, “CMOS Analog Circuit Design”, Oxford University Press, Third edition 2018. [3] B Razavi, \"Design of Analog CMOS Integrated Circuits\", Second edition, McGraw Hill (MGH)-Science/Engineering, 2017. [4] H. S. Bindra et al., \"A 30fJ comparison dynamic bias comparator,\" ESSCIRC 2017 - 43rd IEEE Euro. Solid State Ckts. Conf., Leuven, Belgium, 2017, pp. (71-74). [5] D. Mohtashemi and M. M. Green, \"A Low-Power 8-GS/s Comparator for High-Speed Analog-to-Digital Conversion in $0.13\\mu$ m CMOS Technology,\" in IEEE Trans. on Ckts.& Systms.-II: Exp. Briefs, vol. 66, no. 4, pp. 557-561, April 2019. [6] H. Xu and A. A. Abidi, \"Analysis and Design of Regenerative Comparators for Low Offset and Noise,\" in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 8, pp. 2817-2830, Aug. 2019. [7] R. K. Siddharth et al., \"A 1-V, 3-GHz Strong-Arm Latch Voltage Comparator for High Speed Applications,\" in IEEE Trans. on Ckts. & Systs-II: Express Briefs, vol. 67, no. 12, pp. 2918-2922, Dec. 2020. [8] K. S. Kumar, et al., \"A High Speed Flash Analog to Digital Converter,\" 2018 2nd International Conference on I-SMAC (IoT in Social, Mobile, Analytics and Cloud) (I-SMAC)I-SMAC (IoT in Social, Mobile, Analytics and Cloud) (I-SMAC), 2018 2nd Intern. Conf., 2018, pp. 283-288. [9] Ramamurthy, C. et al., “Deterministic Digital Calibration Technique for 1.5 bits/stage Pipelined and Algorithmic ADCs with Finite op-amp Gain and Large Capacitance Mismatches”, Ckts. Syst Signal Process 40, 3684–3702 (2021). [10] Arash Rezapour et al., \"Design and Improved Structure for 10-Bit Pipeline Analog to Digital Converter Based on 0.18µm CMOS Technology\", Journ. of Appl. Engg. Sci., vol.9, no.2, pp.169, 2019. [11] A. Khorami et al. \"A low-power high-speed comparator for analog to digital converters,\" 2016 IEEE Intern. Symp. on Ckts. & Systs. (ISCAS), Montreal, QC, Canada, 2016, pp. 2010-2013. [12] A. Parthipan, et al. \"A High Performance CMOS Operational Amplifier,\" 2019, Third Intern. Conf. on Compu. Methodologies and Comm. (ICCMC), Erode, India, 2019, pp. 702-706. [13] A. Yadav et al., \"Design of Flash ADC using low offset comparator for analog signal processing application,\" 2021-Eighth Intern. Conf. on Sig. Proc. and Integ. Net. (SPIN), Noida, India, 2021, pp. 76-81. [14] K. L. Krishna et al., \"A 1V second order delta sigma ADC in 130nm CMOS,\" Intern. Conf. on Inform. Comm. & Embd. Sys., (ICICES2014), Chennai, India, 2014, pp. 1-5. [15] Daehwa PAIK, Masaya MIYAHARA, Akira MATSUZAWA, An Analysis on a Dynamic Amplifier and Calibration Methods for a Pseudo-Differential Dynamic Comparator, IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences, 2012, Volume E95.A, Issue 2, Pages 456-470 [16] Li, S., Xu, Z. & Iizuka, T. Analysis of strong-arm comparator with auxiliary pair for offset calibration. Analog Integr. Circ. Sig. Process. 110, 535–546 (2022). [17] K. R. Surendra et al., \"A Modified Low-Offset High Speed Comparator Circuit for Flash Converter Architecture,\" 2023 International Conference on Self-Sustainable Artificial Intelligence Systems (ICSSAS), Erode, India, 2023, pp. 1649-1653. [18] Kumar K.S. et al.,\"A High Speed Flash Analog to Digital Converter,\" 2nd International Conference on I-SMAC (IoT in Social, Mobile, Analytics and Cloud) (I-SMAC)I-SMAC (IoT in Social, Mobile, Analytics and Cloud) (I-SMAC), 2018, pp. 283-288.

Copyright

Copyright © 2024 M. Adhithya, K. Lokesh Krishna. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Download Paper

Paper Id : IJRASET59057

Publish Date : 2024-03-16

ISSN : 2321-9653

Publisher Name : IJRASET

DOI Link : Click Here

Submit Paper Online

Submit Paper Online