Ijraset Journal For Research in Applied Science and Engineering Technology

- Home / Ijraset

- On This Page

- Abstract

- Introduction

- Conclusion

- References

- Copyright

High Speed and Area Efficient Scalable n-Bit Digital Comparator

Authors: B. Dhanalakshmi, A. Shireesha, A. Ramya, T. Bharath Simha Reddy, G. Krishna Kishore, Dr. V. Madhurima

DOI Link: https://doi.org/10.22214/ijraset.2024.58147

Certificate: View Certificate

Abstract

The digital comparator is a crucial design element in various applications, including scientific computations. It is optimized for general-purpose computer architecture, memory addressing logic, queue buffers, and test circuits. High-speed comparators are essential for arithmetic operations, data sorting, and decision-making processes in digital systems. Area efficiency is crucial in integrated circuit design, as it minimizes the physical space a comparator occupies on a chip, reducing manufacturing costs and optimizing performance. The term \"scalable\" means the comparator can be adapted to handle different word lengths (n-bit), making it versatile for various applications. This project proposes an area-efficient n-bit digital comparator with high operating speed and low-power dissipation. The comparator structure consists of two modules: the Comparison Evaluation Module (CEM) and the Final Module (FM). The CEM involves the regular structure of repeated logic cells used for parallel prefix tree structure, while the FM validates the final comparison based on results from the CEM. The design is implemented using Tanner EDA in 45nm technology.

Introduction

I. INRODUCTION

Digital comparator is a fundamental design element used in various applications, including scientific computations and test circuits. It is the key component in general-purpose computer architecture for memory addressing logic, queue buffers, and test circuits. The design of comparator logic requires optimization in terms of area, power, and speed. Some designs use dynamic logic for low-power consumption, but these have limitations due to low-speed and poor noise margin. Other designs use flat adder components and custom logic circuits for wider bit operands, but they provide slower response and area-intensive arrangements. Hierarchical prefix tree structure-based comparator improves scalability and reduces comparison delay, but may be prohibitive for wide input operands due to prolonged delay and power consumption. Parallel prefix tree structure can be improved by using two input multiplexers at each level and generate-propagate logic at the first level. However, the comparator structure has high power consumption since every cell remains active regardless of the applied operand values.The design of high-speed and low power binary comparators has gained significant attention in recent years. These digital systems are used for data comparison in arithmetic or logical operations, determining whether one number is greater than, equal, or less than another. Digital comparators are commonly used in combinational systems and can be connected in cascade arrangement to perform comparisons of longer lengths.

When comparing two binary numbers, the most significant bits (MSBs) are compared first. If these MSBs are equal, the next significant bits are compared. If not, the comparison ceases. The comparator produces three outputs: L, E, and G, which correspond to less than, equal, and greater than comparisons. This makes it essential for digital systems to have reliable and efficient data comparison tools.A magnitude digital comparator is a circuit that compares two digital or binary numbers, A and B, to determine their relative magnitudes. It uses three binary variables to indicate the outcome of the comparison, such as A>B, A<B, or A<B.

Magnitude comparators are crucial in microcontrollers and CPUs for data comparison, arithmetic operations, and decision-making. They are implemented in numerous devices, including auto-turn-off devices. A comparator is a decision-making tool that can be executed in multiple control devices. It accepts two binary numbers (A and B) and outputs equality (A=B) or logic 1 in two conditions (A>B or A< B).Binary comparators are essential in various circuits like microprocessors, communications systems, encryption devices, image processing, and 3D graphics. They are used to compare two n-bit bit numbers, determining their greater or equal value. Comparators are classified into Analog and Digital comparators, with the digital comparator being the primary focus. High-performance systems rely heavily on these comparators for performance and power consumption optimizations. Comparators are critical in determining the greater or equal value of two inputs.

II. EXISTING SYSTEM

This paper presents a new design for a high-speed and area-efficient N-bit digital comparator. The design is tailored for N-bit digital comparison, achieving remarkable speed without compromising area efficiency. It uses advanced circuit techniques to minimize propagation delays, enabling rapid and reliable comparisons. The design incorporates scalable elements, making it adaptable to various bit-width requirements. Low-power design principles enhance energy efficiency. Simulation results show superior performance in speed and area utilization compared to existing designs. This N-bit digital comparator is promising for applications in high-speed digital signal processing and arithmetic units.

Abdel-Hafeez,S., Gordon-Ross,A., and Parhami,B have developed a scalable digital CMOS comparator using a parallel prefix tree. This design allows for high-speed operation using conventional digital CMOS cells and reduces dynamic power dissipation by eliminating unnecessary transitions. The comparator is composed of locally interconnected CMOS gates with a maximum fan-in and fan-out of five and four, respectively. The design maintains high speed and power efficiency over a wide range and uses a reconfigurable VLSI topology for analytical derivation of input-output delay.

Vijaya Krishna Boppana, N. V., & Ren, S proposed a low-power and area-efficient 64-bit digital comparator, based on radix-4 trees. It offers lower power consumption and smaller area, making it ideal for low-power portable devices. Resource sharing is crucial, with 64 XE blocks contributing to the worst power consumption. The design can also be used for 64-bit adders and encryption devices. Lam, H.M., & Tsui, C.Y proposed a mux-based high-performance single-cycle CMOS comparator architecture, utilizing a hierarchical two-stage structure and a dynamic MUX for improved delay. The 64-bit comparator has less delay and is suitable for high-speed applications.

Saravanakumar proposes an ASIC implementation of a parallel binary comparator using Carry Look Ahead (CLA) technique. This design achieves low power and high-speed operation, especially in low-input data activity environments. The comparator is designed using VHDL code and synthesized using ALTERA QUARTUS - II. Experimental evaluation shows a reduction in delay and gate count for a 16-bit design.

Kumar, K.R.Reddy, P. M. Sadanandam, M. Kumar, A. S., & M.Raju proposed a 2T XOR gate-based full adder using the GDI technique to reduce power, improve speed, and optimize area through transistor count. The focus is on low power VLSI (Very Large Scale Integration) due to the increasing transistor count on chips. High power consumption increases the temperature of the IC and affects battery durability in portable devices. The GDI approach provides optimized conditions for the full adder design. The work is carried out in 180nm technology using LTspice tool for time delay and Xilinx 14.7 ISE for power analysis. The analysis shows that the proposed method is better than conventional CMOS.

Naseri.H & Timarchi.S propose novel circuits for XOR/XNOR and simultaneous XOR–XNOR functions, optimized for low power consumption and delay. They also propose six hybrid 1-bit full-adder circuits based on full-swing XOR–XNOR or XOR/XNOR gates. The proposed circuits have various merits in terms of speed, power consumption, power delay product (PDP), driving ability, and other factors. The researchers propose a new transistor sizing method using a numerical computation particle swarm optimization algorithm to optimize circuits. Manasi Vaidya designed a 2-bit magnitude comparator using CMOS, reducing complexity and increasing computation speed in digital devices like ADC and memory chips. The design was done using Full Adder circuit in Mentor Graphics Eldo net tool and 180nm technology file. Simulations were conducted on 0.6V, 0.8V, 1V, and 1.2V, finding the least dissipated power at 48.82pW in 0.6V but the longest delay at 53.098ns. The comparator design was compared with other logic styles. Panda, A. K., Palisetty, R., & Ray, K.C have developed an Area-Efficient Parallel-Prefix Binary Comparator for CLCG based PRBG methods. The 32-bit comparator consumes less power and less LUT area compared to magnitude and mux-based comparators. The merging circuit technique in prefix computation stages significantly reduces the area of the binary comparator. The 32-bit comparator is designed with Verilog HDL and implemented on a Spartan3E FPGA device for hardware performance.

Reto Zimmermann's study on low-power logic styles reveals that complementary CMOS is superior to complementary pass-transistor logic (CPL) in terms of speed, area, power dissipation, and power-delay products. CMOS logic gates offer robustness, generality, and ease-of-use, making it the preferred choice for implementing combinational circuits with low voltage, low power, and small power-delay products.

Oguz Ergin's study focuses on designing fast, energy-efficient CMOS comparators for high-performance microprocessors. These comparators, used in datapath components, are often energy-inefficient due to mismatches. Ergin proposes two new circuits that primarily dissipate energy on matches, resulting in significant savings in power dissipation. The designs are evaluated using SPICE simulations and micro-architectural level statistics. This approach can improve the performance of high-performance microprocessors.

III. PROPOSED SYSTEM

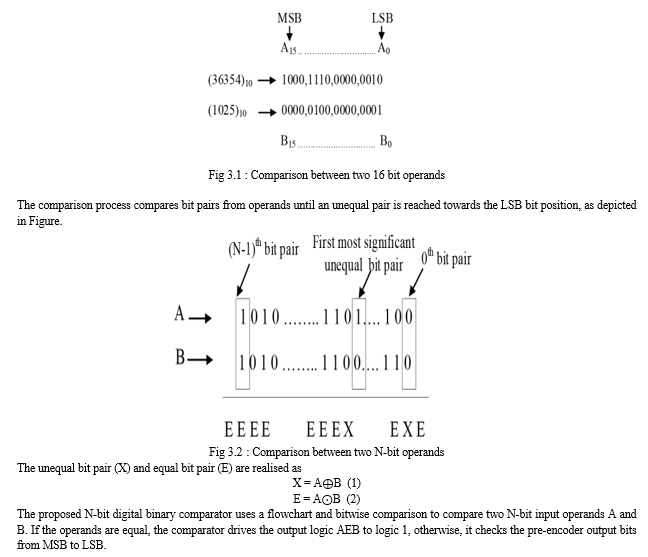

The conventional comparison principle involves comparing operands A and B with unequal most significant bit (MSB) bits. The first unequal bits are used to determine the comparison outcome, and remaining bits are ignored. The comparison process starts from the (N-1)th bit and progresses to the (N-2)th bit if the MSB bits are equal.

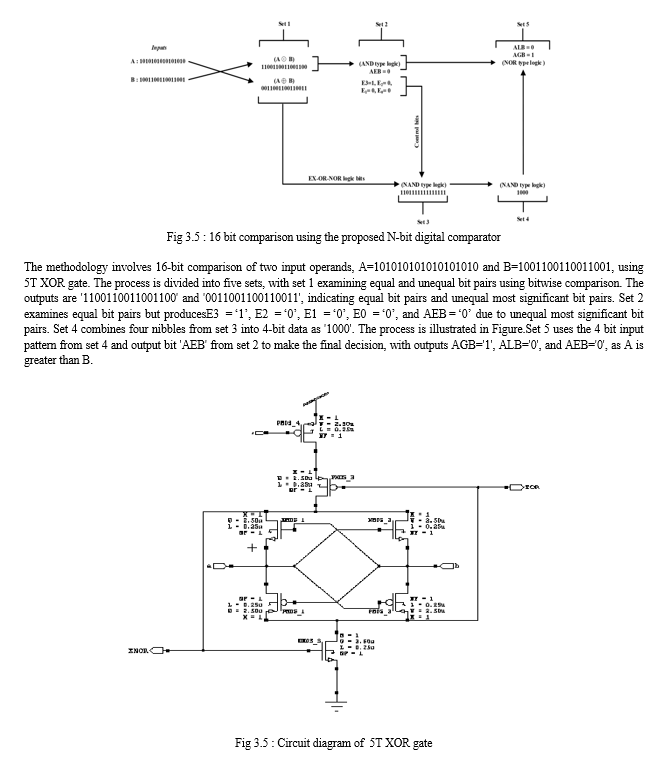

This paper presents a low power hardware efficient comparator using 5T XNOR, an essential module in combinational circuits and comparators. It also uses XNOR and XOR circuits in encryption and arithmetic circuits for low power consumption, making it suitable for VLSI design.The proposed work focuses on setting up a low power area efficient comparator circuit using a 5T XOR gate, consisting of 5 transistors, to achieve maximum output voltage while minimizing parasitic effect. The goal is to maintain a symmetry between power and speed at lower voltage levels and highest output voltage levels.A digital comparator is a hardware that compares two numbers and determines if one number is greater than, less than, or equivalent to the other.

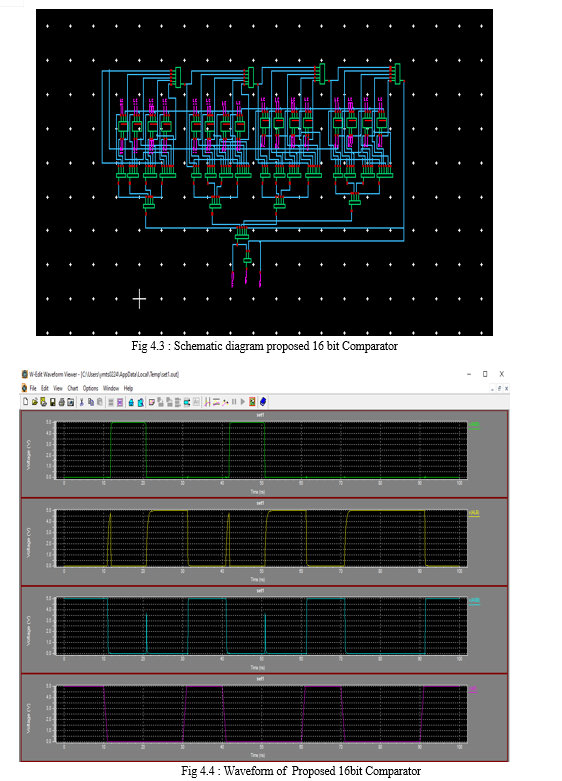

The 5T XOR gate is a simplified version of the traditional XOR gate, featuring five transistors including two NMOS, two PMOS, and an additional NMOS transistor, making it an ideal choice for area-efficient designs.This paper presents a new design for a high-speed, area-efficient N-bit digital comparator. The design is tailored for N-bit digital comparison, achieving speed without compromising area efficiency. The architecture optimizes circuit components and signal propagation, minimizing propagation delays. This design is essential for high-performance digital systems and enables rapid and reliable N-bit comparisons, meeting the growing demand for compact, high-performance comparators.

The proposed XOR gate offers superior power, area, full swing voltage, and excellent driving capability, allowing it to be cascaded to various stages due to its excellent driving capability.

Table 4.1 Power, Delay and Area calculations of the circuits

|

Name of the circuit |

Power(mw) |

Delay (ns) |

Area (nm) |

|

Proposed 64-bit comparator |

4.6 |

4.2 |

1318 |

|

Existing 64-bit comparator |

5.1 |

4.4 |

1382 |

|

Proposed 24-bit comparator |

1.7 |

1.2 |

498 |

|

Existing 24-bit comparator |

1.9 |

1.3 |

522 |

|

Proposed 16-bit comparator |

4.9 |

0.2 |

334 |

|

Existing 16-bit comparator |

6.8 |

0.3 |

350 |

Conclusion

In conclusion,the proposed scalable comparator uses CEM and FM structures, implementing a parallel prefix tree structure. This structure predicts the comparator\'s characteristics for arbitrary bit widths. This scalable n-bit digital comparator is a significant advancement in digital circuit design, ensuring adaptability across various applications and seamless integration into complex systems. High efficiency enhances performance and contributes to resource optimization. The comparator is suitable for scientific computations, test circuits, and memory addressing logic.

References

[1] Parhami, B.: ‘Efficient hamming weight comparators for binary vectors based on accumulative and up/down parallel counters’, IEEE Trans. Circuits Syst., 2009, 56, (2), pp. 167–171 [2] Liu, H.J.R., Yao, H.: ‘High-performance VLSI signal processing innovative architectures and algorithms’ (IEEE Press, Piscataway, NJ, 1998) [3] Sheng, Y., Wang, W.: ‘Design and implementation of compression algorithm comparator for digital image processing on component’. Proc. Ninth Int. Conf. Young Computer Scientists, Hunan, China, November 2008, pp. 1337– 1341 [4] Abramovici, M., Breuer, M.A., Friedman, A.D., et al.: ‘Digital systems testing and testable design’ (IEEE Press, Piscataway, NJ, 1990) [5] Chan, A., Roberts, G.W.: ‘A jitter characterization system using a componentinvariant Vernier delay line’, IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 2004, 12, (1), pp. 79–95 [6] Oklobdzija, V.G.: ‘An algorithmic and novel design of a leading zero detector circuit: comparison with logic synthesis’, IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 1994, 2, (1), pp. 124–128 [6] Suzuki, H., Kim, C.H., Roy, K., et al.: ‘Fast tag comparator using diode partitioned domino for 64 bit microprocessor’, IEEE Trans. Circuits Syst. I, 2007, 54, (2), pp. 322–328 [7] Ponomarev, D., Kucuk, G., Ergin, O., et al.: ‘Energy-efficient comparators for superscalar data paths’, IEEE Trans. Comput., 2004, 53, (7), pp. 892–904 [8] Guangjie, W., Shimin, S., Lijiu, J., et al.: ‘New efficient design of digital comparator’. Proc. Second Int. Conf. Applications Specific Integrated Circuits, Shanghai, China, 1996, pp. 263–266 [9] Abdel-Hafeez, S.: ‘Single rail domino logic for four-phase clocking scheme’, U.S. Patent 6265899, October 2001 [10] Ercegovac, M.D., Lang, T.: ‘Digital arithmetic’ (Morgan Kaufmann, San Mateo, CA, 2004) [12] Stine, J.E., Schulte, M.J.: ‘A combined two\'s complement and floating-point comparator’. Proc. Int. Symp. Circuits Systems, 2005, pp. 89–92 [11] Cheng, S.: ‘A high-speed magnitude comparator with small transistor count’. Proc. IEEE Int. Conf. Electronics, Circuits, Systems, Sharjah, United Arab Emirates, December 2003, pp. 1168–1171 [12] Bellaour, A., Elmasry, M.I.: ‘Low-power digital VLSI design circuits and systems’ (Kluwer, Norwood, MA, 1995) [13] Wang, C.C., Wu, C.F., Tsai, K.C., et al.: ‘1 GHz 64 bit high-speed comparator using ANT dynamic logic with two-phase clocking’, IEE Proc.-Comput. Digit. Tech., 1998, 145, (6), pp. 433–436 [14] Belluomini, W., Jamsek, D., Nartin, A.K., et al.: ‘Limited switch dynamic logic circuits for high-speed low-power circuit design’, IBM J. Res. Dev., 2006, 50, (2–3), pp. 277–286 [15] Wang, C., Lee, P., Wu, C., et al.: ‘High fan-in dynamic CMOS comparators with low transistor count’, IEEE Trans. Circuits Syst. I, 2003, 50, (9), pp. 1216–1220 [16] Huang, C.H., Wang, J.S.: ‘High-performance and power-efficient CMOS comparators’, IEEE J. Solid-State Circuits, 2003, 38, (2), pp. 254–262 [17] Lam, H.M., Tsui, C.Y.: ‘A mux-based high-performance single-cycle CMOS comparator’, IEEE Trans. Circuits Syst. II, 2007, 54, (7), pp. 591–595 [18] Maheshwari, N., Sapatnekar, S.S.: ‘Optimizing large multiphase level-clocked circuits’, IEEE Trans. Comput. Aided Des. Integr. Circuits Syst., 1999, 18, (9), pp. 1249–1264 [19] Frustaci, F., Perri, S., Lanuzza, M., et al.: ‘Energy-efficient single-clock-cycle binary comparator’, Int. J. Circuit Theory Appl., 2012, 40, (3), pp. 237–246 [20] Coussy, P., Morawiec, A.: ‘High-level synthesis: from algorithm to digital circuit’ (Springer-Verlag, New York, 2008) [21] Perri, S., Corsonello, P.: ‘Fast low-cost implementation of single-clock-cycle binary comparator’, IEEE Trans. Circuits Syst. II, 2008, 55, (12), pp. 1239– 1243 [22] Lutz, D.R., Jayasimha, D.N.: ‘The half-adder form and early branch condition resolution’. Proc. 13th IEEE Symp. Computer Arithmetic, Asilomar, CA, USA, July 1997, pp. 266–273 [23] Ercegovac, M.D., Lang, T.: ‘Sign detection and comparison networks with a small number of transitions’. Proc. 12th IEEE Symp. Computer Arithmetic, Bath, UK, July 1995, pp. 59–66 [26] Bruguera, J.D., Lang, T.: ‘Multilevel reverse most-significant carry computation’, IEEE Trans. Very Large Scale Integr. (VLSI) Syst., 2001, 9, (6), pp. 959– [24] Hensley, J., Singh, M., Lastra, A., et al.: ‘A fast, energy-efficient z comparator’. Proc. ACM Conf. Graphics Hardware, Los Angeles, California, 2005, pp. 41–44 [25] Ekanayake, V.N., Clinton, I.K., Manohar, R., et al.: ‘Dynamic significance compression for a low-energy sensor network asynchronous processor’. Proc. 11th IEEE Int. Symp. Asynchronous Circuits Systems, New York City, NY, USA, March 2005, pp. 144–154 [26] Lam, H.M., Tsui, C.Y.: ‘High-performance single clock cycle CMOS comparator’, Electron. Lett., 2006, 42, (2), pp. 75–77 [27] Kim, J.Y., Yoo, H.J.: ‘Bitwise competition logic for compact digital comparator’. Proc. IEEE Asian Solid-State Circuits Conf., Jeju, South Korea, November 2007, pp. 59–62. [28] M.U.agera, K.L.Krishna, K.Anuradha, “Implementation of Smart Home Automation with Enhanced Security”, International Journal of Scientific Research in Science, Vol. 4, Iss.4, 2018.

Copyright

Copyright © 2024 B. Dhanalakshmi, A. Shireesha, A. Ramya, T. Bharath Simha Reddy, G. Krishna Kishore, Dr. V. Madhurima. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Download Paper

Paper Id : IJRASET58147

Publish Date : 2024-01-23

ISSN : 2321-9653

Publisher Name : IJRASET

DOI Link : Click Here

Submit Paper Online

Submit Paper Online